资料介绍

描述

这是如何为 Alinx 制造的AXU2CGA/B Zynq UltraScale+ FPGA 开发板创建硬件加速器平台的分步教程,该平台 可用于在 Xilinx Vitis 工具集下运行具有加速功能的 GNU Radio 应用程序。

添加 EA4GPZ 开发的gr-satellites并构建您自己的 OOT 模块也包含在这套教程中。

这是第 3/4 部分:使用 DPU 创建 Vitis 平台

使用之前创建的 Vivado 项目和 PetaLinux SDK 创建 Vitis 平台。

如果你正在寻找这组教程的其他部分,你可以直接去那里:

- 第 1 部分 - 创建 Vivado 硬件设计

- 第 2 部分 - 软件 - 构建 PetaLinux 和 GNU Radio

- 第 3 部分 - 使用 DPU 创建 Vitis 平台和应用程序

- 第 4 部分 - 在 Colab 和 Vitis-AI 中构建 AI 模型

准备平台打包文件

1-转到项目主目录下先前创建的平台目录,如果不存在则创建它。

$ pwd

# /tools/workspace/axu2cgb

$ mkdir platform

$ ls

# hardware platform software

cd platform

2-创建一些新目录来存储一些以前创建的文件。

mkdir -p pfm/boot

mkdir -p pfm/sd_dir

3- 将生成的 Linux 软件启动组件从Part-2复制到 pfm/ boot目录。

$ cp ../software/axu2cgb_2021_2-petalinux/images/linux/zynqmp_fsbl.elf pfm/boot/

$ cp ../software/axu2cgb_2021_2-petalinux/images/linux/pmufw.elf pfm/boot/

$ cp ../software/axu2cgb_2021_2-petalinux/images/linux/bl31.elf pfm/boot/

$ cp ../software/axu2cgb_2021_2-petalinux/images/linux/system.dtb pfm/boot/

$ cp ../software/axu2cgb_2021_2-petalinux/images/linux/u-boot-dtb.elf pfm/boot/u-boot.elf

$ ls pfm/boot/

bl31.elf pmufw.elf system.dtb u-boot.elf zynqmp_fsbl.elf

注意:最后一个文件u-boot-dtb.elf被重命名为u-boot.elf。请不要使用原始的 u-boot.elf,因为它不包含设备树块。

4- 将boot.scr和system.dtb复制到pfm/sd_dir文件夹。

$ cp ../software/axu2cgb_2021_2-petalinux/images/linux/boot.scr pfm/sd_dir/

$ cp ../software/axu2cgb_2021_2-petalinux/images/linux/system.dtb pfm/sd_dir/

$ ls pfm/sd_dir/

boot.scr system.dtb

5- 将sysroot安装到pfm文件夹中。

在安装 sysroot 之前,您必须取消设置系统变量LD_LIBRARY_PATH

export LD_LIBRARY_PATH=

现在,您可以从之前生成的sdk.sh脚本安装 sysroot。

$ ../software/axu2cgb_2021_2-petalinux/images/linux/sdk.sh -d pfm

Y

注意:-d 选项告诉 sdk.sh 脚本安装 sysroot 的位置。

PetaLinux SDK installer version 2021.2

======================================

You are about to install the SDK to "/tools/workspace/axu2cgb/platform/pfm". Proceed [Y/n]?

Extracting SDK.....................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................................done

Setting it up...done

SDK has been successfully set up and is ready to be used.

Each time you wish to use the SDK in a new shell session, you need to source the environment setup script e.g.

$ . /tools/workspace/axu2cgb/platform/pfm/environment-setup-cortexa72-cortexa53-xilinx-linux

创建 Vitis 平台

在启动 Vitis IDE 程序之前,请确保您已设置以下所有路径和设置:

source /tools/Xilinx/Vitis/2021.2/settings64.sh

export OPENCV_INCLUDE=/usr/include/opencv4/

export OPENCV_LIB=/usr/lib/x86_64-linux-gnu/

export LD_LIBRARY_PATH=/usr/lib/x86_64-linux-gnu/

注意:重新设置LD_LIBRARY_PATH变量,因为它在 sysroot 安装期间被删除。

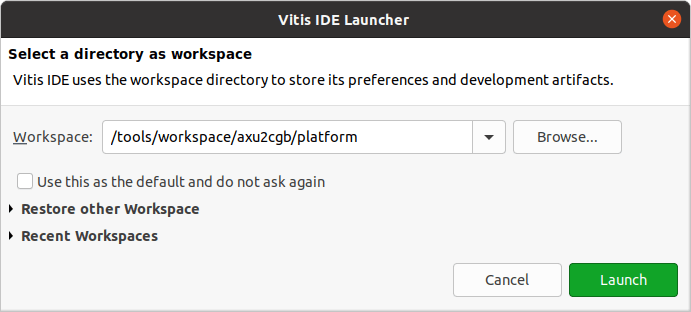

1- 在后台模式下在当前平台文件夹中启动 Vitis IDE,并将相同的文件夹设置为工作区目录。

vitis &

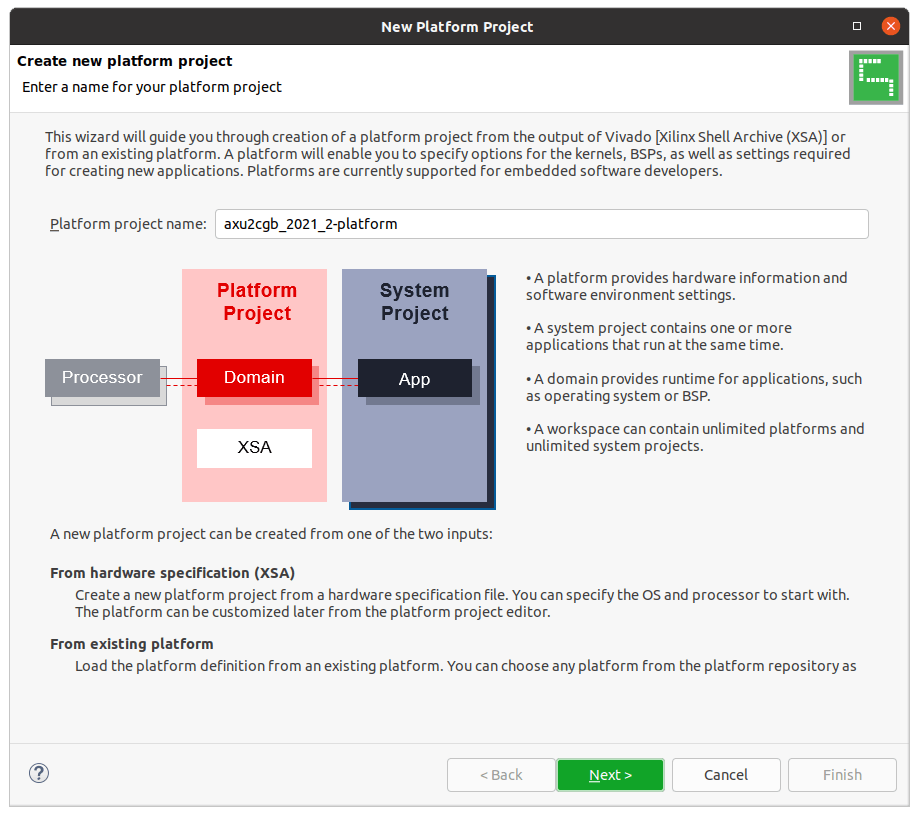

创建一个新平台:文件 > 新建 > 平台项目并将其命名为axu2cgb_2021_2-platform 。点击下一步。

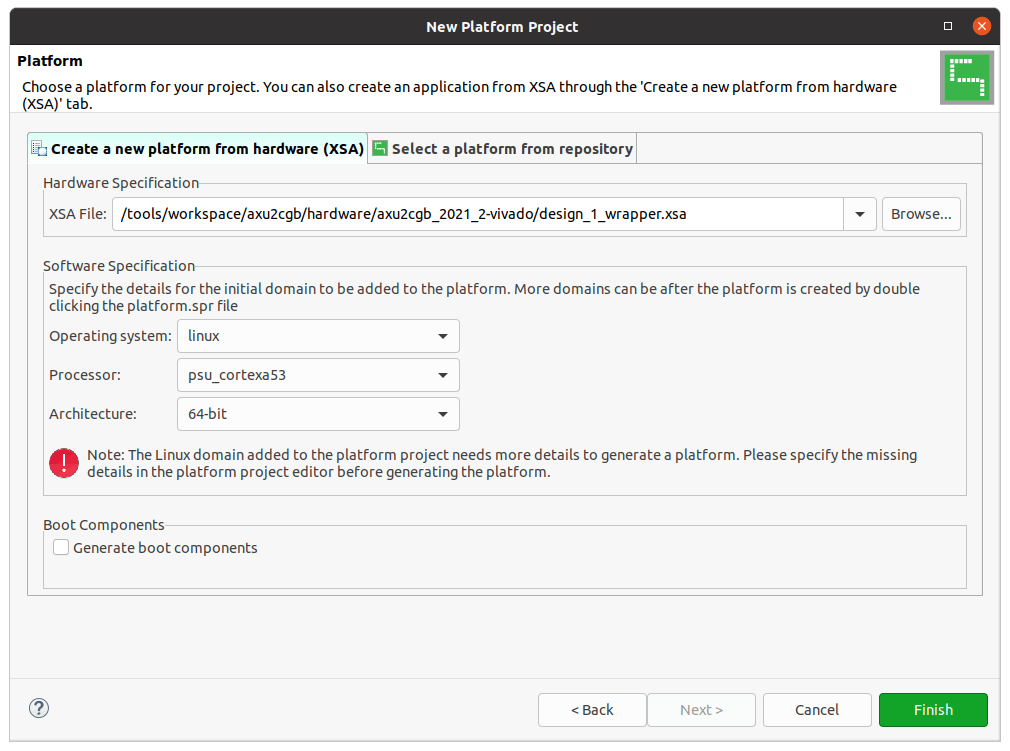

在Hardware Specification中,单击Browse按钮并选择Part-1末尾 Vivado 生成的 XSA 文件。

/tools/workspace/axu2cgb/hardware/axu2cgb_2021_2-vivado/design_1_wrapper.xsa

在操作系统下选择linux 、psu_cortexa53和64-bit 。

取消选中引导组件。单击完成。

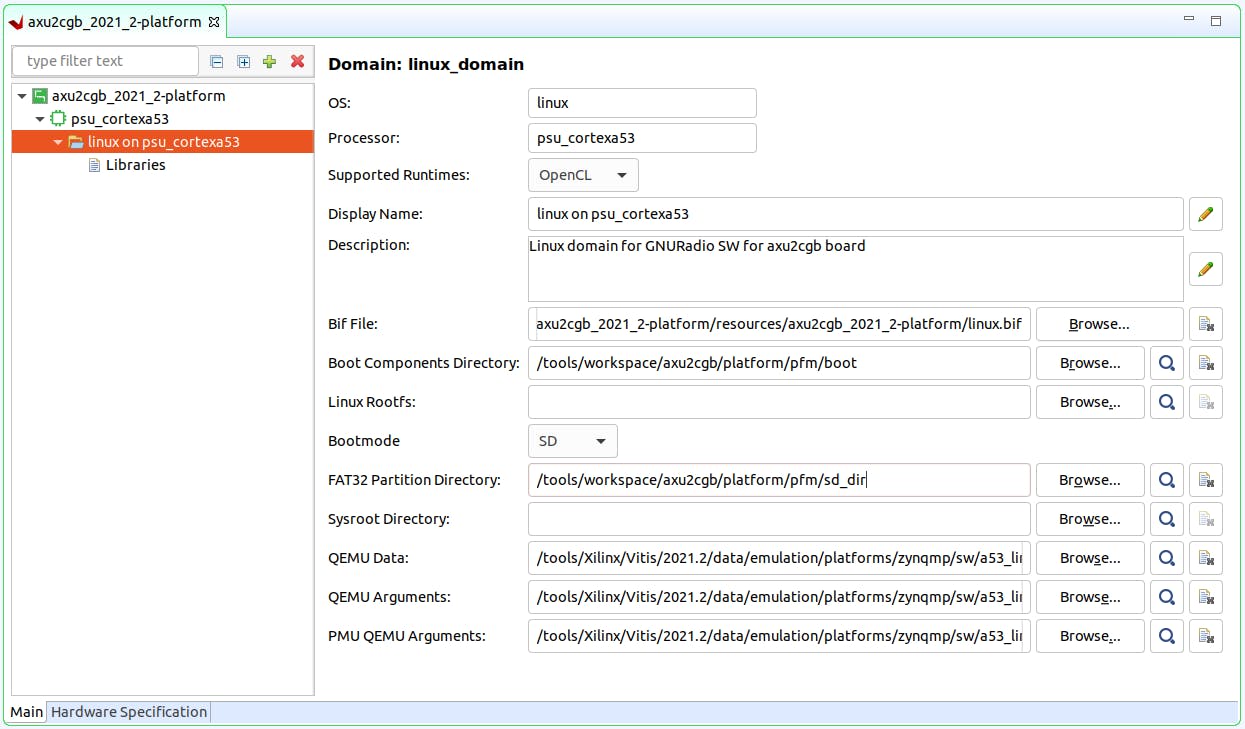

单击psu_cortexa53域上的 linux。

浏览到位置并选择完成以下对话框所需的目录或文件:

- 位文件- 单击生成 BIF (在浏览按钮的末尾

- 引导组件- 浏览到pfm/boot

- FAT32 分区目录- 浏览到pfm/sd_dir

保持所有其他设置不变。

注意:暂时将Linux RootFS和Sysroot 目录留空。

搭建平台

在 Explorer 选项卡窗口中,右键单击创建的平台:

- axu2cgb_2021_2-platform并选择Build Project 。等待几秒钟完成。

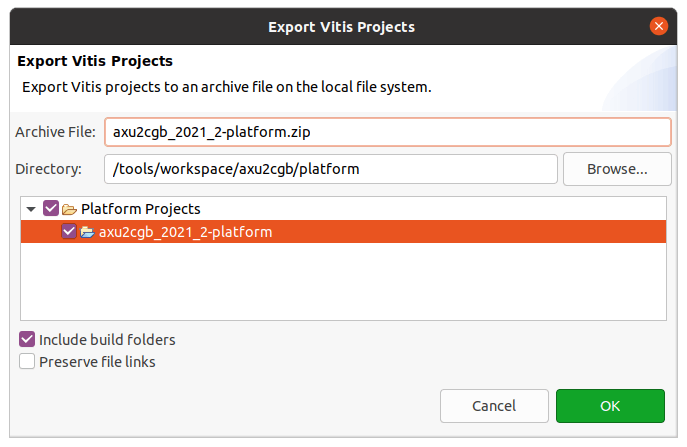

导出平台

在 Explorer 选项卡窗口中,右键单击创建的平台:axu2cgb_2021_2-platform并选择Exportas Archive 。选择您的平台名称并勾选包含构建文件夹。等待几分钟完成。

您可以使用这个导出的 zip 文件来创建新项目。

安装 Vitis-AI

我们创建了一个将 Xilinx 深度学习处理器单元 DPU 集成为内核的新应用程序。Xilinx 已经提供了一个脚本来创建我们需要的一切。

有关 DPU 的更多详细信息,请查看DPU-TRD GitHub 存储库并阅读PG338 DPU IP 产品指南。

首先,我们需要将 Vitis-AI 存储库添加到 Vitis IDE 中。

如果您还没有启动 Vitis IDE,请启动它。我们可以重用之前创建的平台的工作空间。

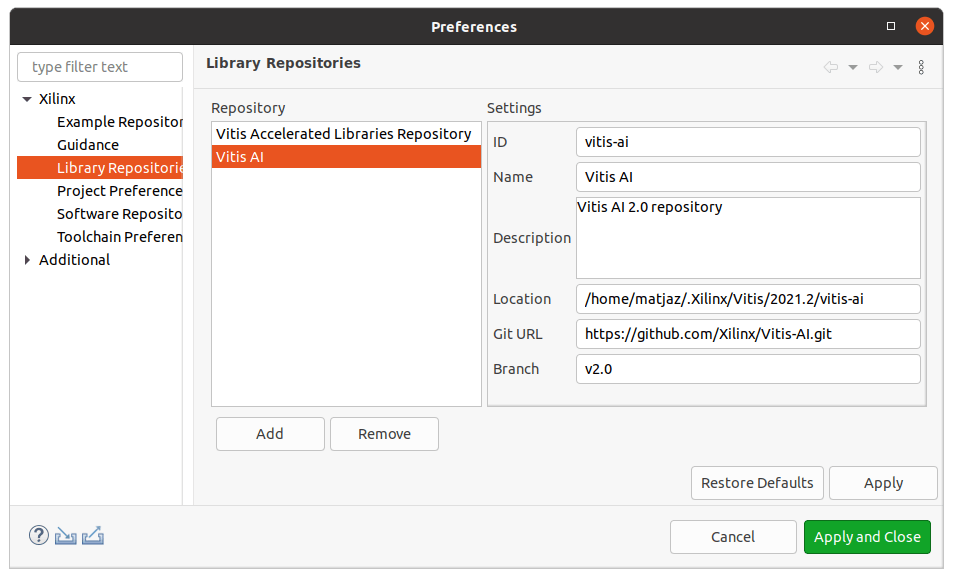

打开菜单Window > Preferences > Library Repository选项卡 > Add

设置以下内容:

- 输入 ID:vitis-ai

- 名称:Vitis AI

- Git 网址:https ://github.com/Xilinx/Vitis-AI.git

- 分支:v2.0或master

申请并关闭

下载 Vitis-AI 库:

- 打开菜单Xilinx >库。

- 找到我们刚刚添加的Vitis-AI条目。

- 点击它上面的下载按钮。

- 等待 Vitis-AI 存储库的下载完成(几分钟)。

- 单击确定。

- v2.0的git 提交 ID 为:d02dcb6041663dbc7ecbc0c6af9fafa087a789de

- master的git commit ID当前为:ba8905493876674716ab08ea4266962193df970b

创建 DPU 应用程序项目

在我们之前创建的 axu2cg_2021_2 平台上创建新的 Vitis-AI 设计。

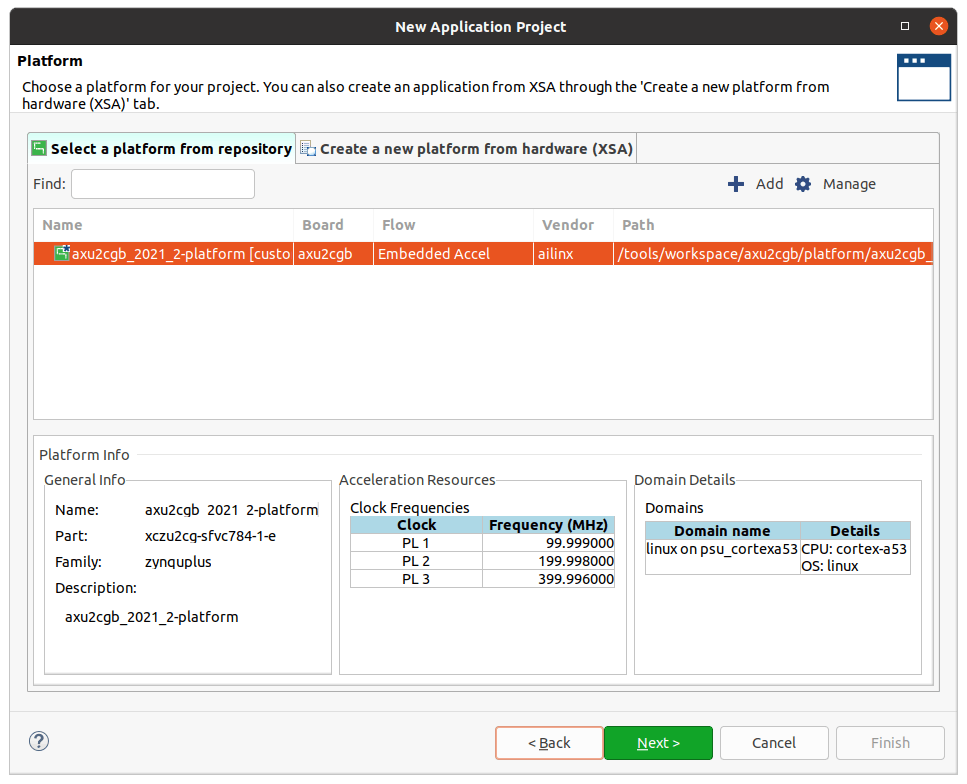

转到菜单文件 > 新建 > 应用程序项目> 下一步。

选择平台axu2cgb_2021_2-platform 。点击下一步。

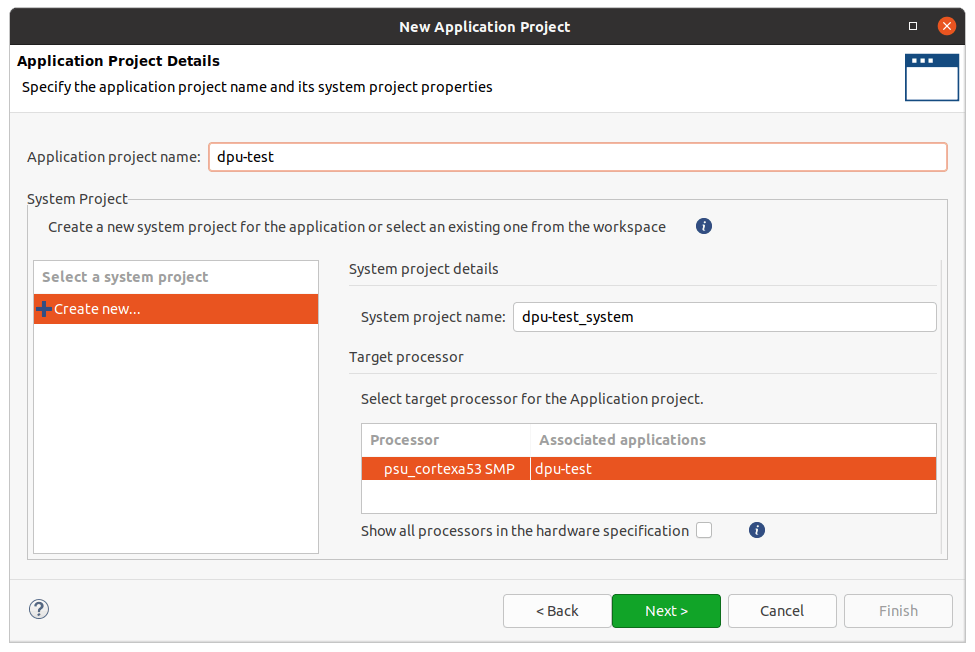

将项目命名为dpu-test ,点击下一步。

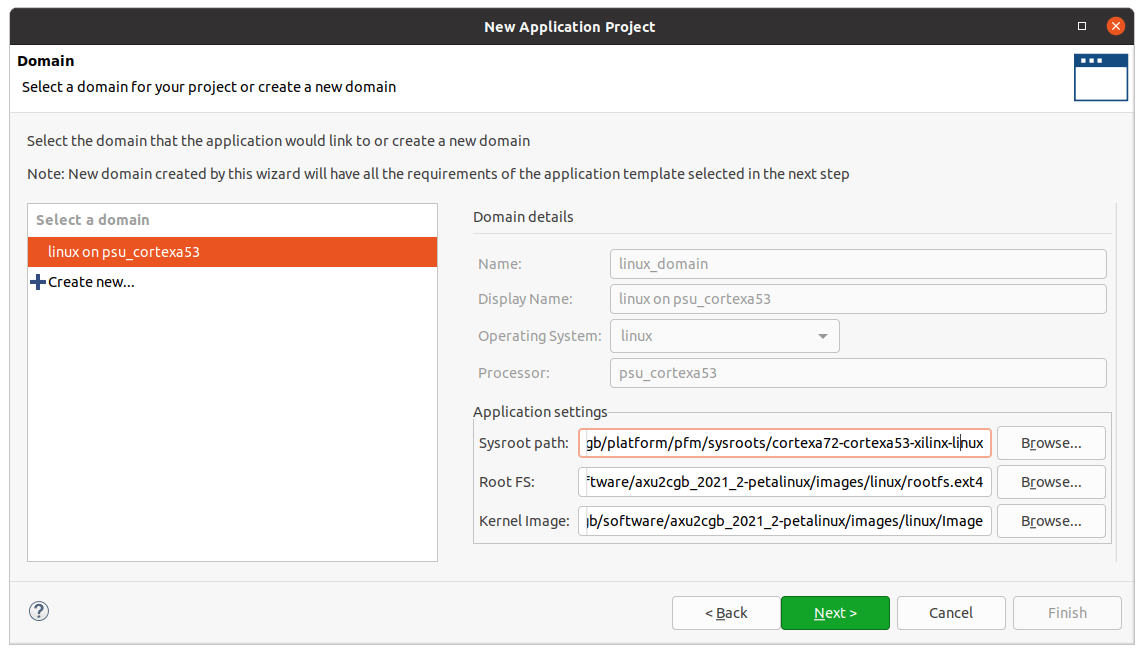

设置域:linux on psu_cortexa53

- 在上一步中将 Sys_root 路径设置为 sysroot 安装路径:

tools/workspace/axu2cgb/platform/pfm/sysroots/cortexa72-cortexa53-xilinx-linux

- 将根 FS设置为 rootfs.ext4。

/tools/workspace/axu2cgb/software/axu2cgb_2021_2-petalinux/images/linux/rootfs.ext4

- 将内核映像设置为映像。

/tools/workspace/axu2cgb/software/axu2cgb_2021_2-petalinux/images/linux/Image

最后两个文件位于第 2 部分中创建的 axu2cgb_2021_2-petalinux/images/linux 文件夹中。

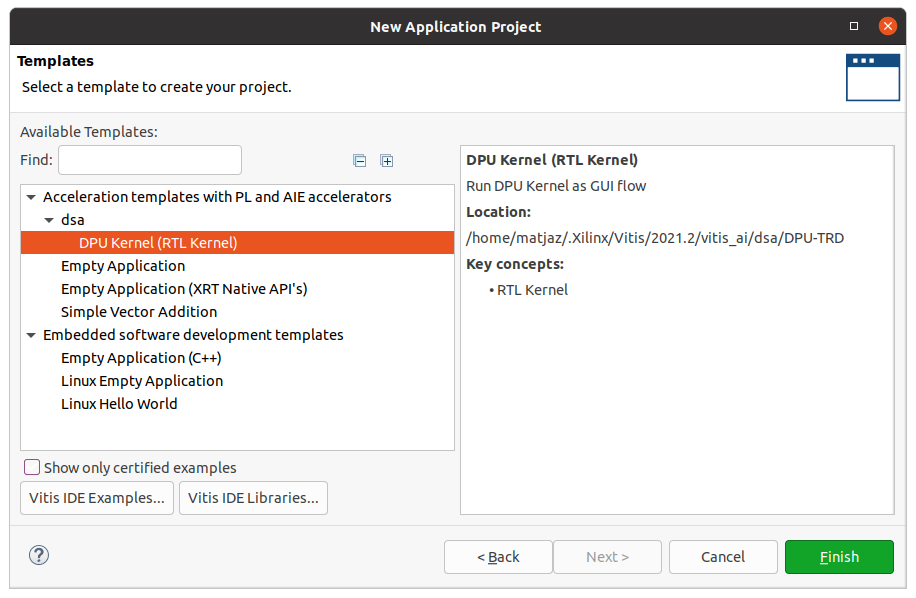

单击下一步并选择:

- dsa > DPU 内核(RTL 内核)

然后单击完成以生成应用程序。

更新构建目标:

- 双击系统项目文件dpu-test_system.sprj并

- 将Active Build Configuration更改为Hardware。

AXU2CGB 的 DPU 设置

由于 axu2cgb 板上的 FPGA 设备没有足够的资源来构建默认配置的 DPU,我们需要:

- 只集成一个内核(默认不是 2 个)。

- 更改 DPU 处理器选择。

- 禁用某些功能。

从dpu-test_kernels/src/prj/Vitis目录打开dpu_conf.vh文件。

- 将 B4096更改为B1152 (第 26 行)

- 将 DRAM_DISABLE更改为DRAM_ENABLE (第 59 行)

- 将 CHANNEL_AUGMENTATION_ENABLE更改为CHANNEL_AUGMENTATION_DISABLE (第 92 行)

- 将 DWCV_ENABLE更改为DWCV_DISABLE (第 103 行)

- 更改 RELU_LEAKYRELU_RELU6 RELU_RELU6 (第 136 行)

如果您拥有更强大的 FPGA,请随意尝试启用更多选项,但是:

- 确保 POOL_AVG 已启用,因为我们的模型需要它。(第 114 行)

保存文件并再次检查所有内容,因为内核构建过程持续很长时间。

//Setting the arch of DPU, For more details, Please read the PG338

/*====== Architecture Options ======*/

// |------------------------------------------------------|

// | Support 8 DPU size

// | It relates to model. if change, must update model

// +------------------------------------------------------+

// | `define B512

// +------------------------------------------------------+

// | `define B800

// +------------------------------------------------------+

// | `define B1024

// +------------------------------------------------------+

// | `define B1152

// +------------------------------------------------------+

// | `define B1600

// +------------------------------------------------------+

// | `define B2304

// +------------------------------------------------------+

// | `define B3136

// +------------------------------------------------------+

// | `define B4096

// |------------------------------------------------------|

`define B1152

// |------------------------------------------------------|

// | If the FPGA has Uram. You can define URAM_EN parameter

// | if change, Don't need update model

// +------------------------------------------------------+

// | for zcu104 : `define URAM_ENABLE

// +------------------------------------------------------+

// | for zcu102 : `define URAM_DISABLE

// |------------------------------------------------------|

`define URAM_DISABLE

//config URAM

`ifdef URAM_ENABLE

`define def_UBANK_IMG_N 5

`define def_UBANK_WGT_N 17

`define def_UBANK_BIAS 1

`elsif URAM_DISABLE

`define def_UBANK_IMG_N 0

`define def_UBANK_WGT_N 0

`define def_UBANK_BIAS 0

`endif

// |------------------------------------------------------|

// | You can use DRAM if FPGA has extra LUTs

// | if change, Don't need update model

// +------------------------------------------------------+

// | Enable DRAM : `define DRAM_ENABLE

// +------------------------------------------------------+

// | Disable DRAM : `define DRAM_DISABLE

// |------------------------------------------------------|

`define DRAM_ENABLE

//config DRAM

`ifdef DRAM_ENABLE

`define def_DBANK_IMG_N 1

`define def_DBANK_WGT_N 1

`define def_DBANK_BIAS 1

`elsif DRAM_DISABLE

`define def_DBANK_IMG_N 0

`define def_DBANK_WGT_N 0

`define def_DBANK_BIAS 0

`endif

// |------------------------------------------------------|

// | RAM Usage Configuration

// | It relates to model. if change, must update model

// +------------------------------------------------------+

// | RAM Usage High : `define RAM_USAGE_HIGH

// +------------------------------------------------------+

// | RAM Usage Low : `define RAM_USAGE_LOW

// |------------------------------------------------------|

`define RAM_USAGE_LOW

// |------------------------------------------------------|

// | Channel Augmentation Configuration

// | It relates to model. if change, must update model

// +------------------------------------------------------+

// | Enable : `define CHANNEL_AUGMENTATION_ENABLE

// +------------------------------------------------------+

// | Disable : `define CHANNEL_AUGMENTATION_DISABLE

// |------------------------------------------------------|

`define CHANNEL_AUGMENTATION_DISABLE

// |------------------------------------------------------|

// | DepthWiseConv Configuration

// | It relates to model. if change, must update model

// +------------------------------------------------------+

// | Enable : `define DWCV_ENABLE

// +------------------------------------------------------+

// | Disable : `define DWCV_DISABLE

// |------------------------------------------------------|

`define DWCV_DISABLE

// |------------------------------------------------------|

// | Pool Average Configuration

// | It relates to model. if change, must update model

// +------------------------------------------------------+

// | Enable : `define POOL_AVG_ENABLE

// +------------------------------------------------------+

// | Disable : `define POOL_AVG_DISABLE

// |------------------------------------------------------|

`define POOL_AVG_ENABLE

// |------------------------------------------------------|

// | support multiplication of two feature maps

// | It relates to model. if change, must update model

// +------------------------------------------------------+

// | Enable : `define ELEW_MULT_ENABLE

// +------------------------------------------------------+

// | Disable : `define ELEW_MULT_DISABLE

// |------------------------------------------------------|

`define ELEW_MULT_DISABLE

// +------------------------------------------------------+

// | RELU Type Configuration

// | It relates to model. if change, must update model

// +------------------------------------------------------+

// | `define RELU_RELU6

// +------------------------------------------------------+

// | `define RELU_LEAKYRELU_RELU6

// |------------------------------------------------------|

`define RELU_RELU6

// |------------------------------------------------------|

// | DSP48 Usage Configuration

// | Use dsp replace of lut in conv operate

// | if change, Don't need update model

// +------------------------------------------------------+

// | `define DSP48_USAGE_HIGH

// +------------------------------------------------------+

// | `define DSP48_USAGE_LOW

// |------------------------------------------------------|

`define DSP48_USAGE_HIGH

// |------------------------------------------------------|

// | Power Configuration

// | if change, Don't need update model

// +------------------------------------------------------+

// | `define LOWPOWER_ENABLE

// +------------------------------------------------------+

// | `define LOWPOWER_DISABLE

// |------------------------------------------------------|

`define LOWPOWER_DISABLE

// |------------------------------------------------------|

// | DEVICE Configuration

// | if change, Don't need update model

// +------------------------------------------------------+

// | `define MPSOC

// +------------------------------------------------------+

// | `define ZYNQ7000

// |------------------------------------------------------|

`define MPSOC

移除 SoftMax 函数和一个内核实例

我们使用在主 CPU 上运行的 SoftMax 功能的软件实现,因此我们将其从内核中删除以节省一些资源。

此外,如果我们使用的是 AXU2CGB 板,我们只能集成一个 DPU 内核实例。

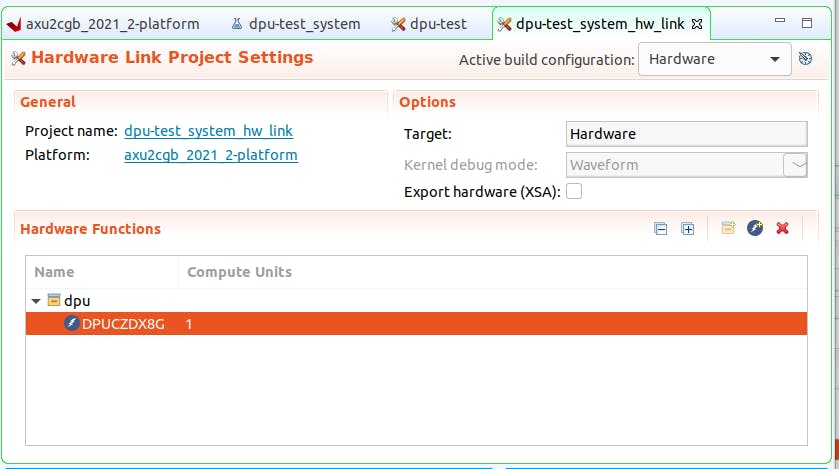

双击dpu-test_system_hw_link.prj:

- 通过右键单击删除sfm_xrt_top函数并选择删除。

- 将DPUCZDX8G的 Compute Units 更改为1。

V++ 配置设置

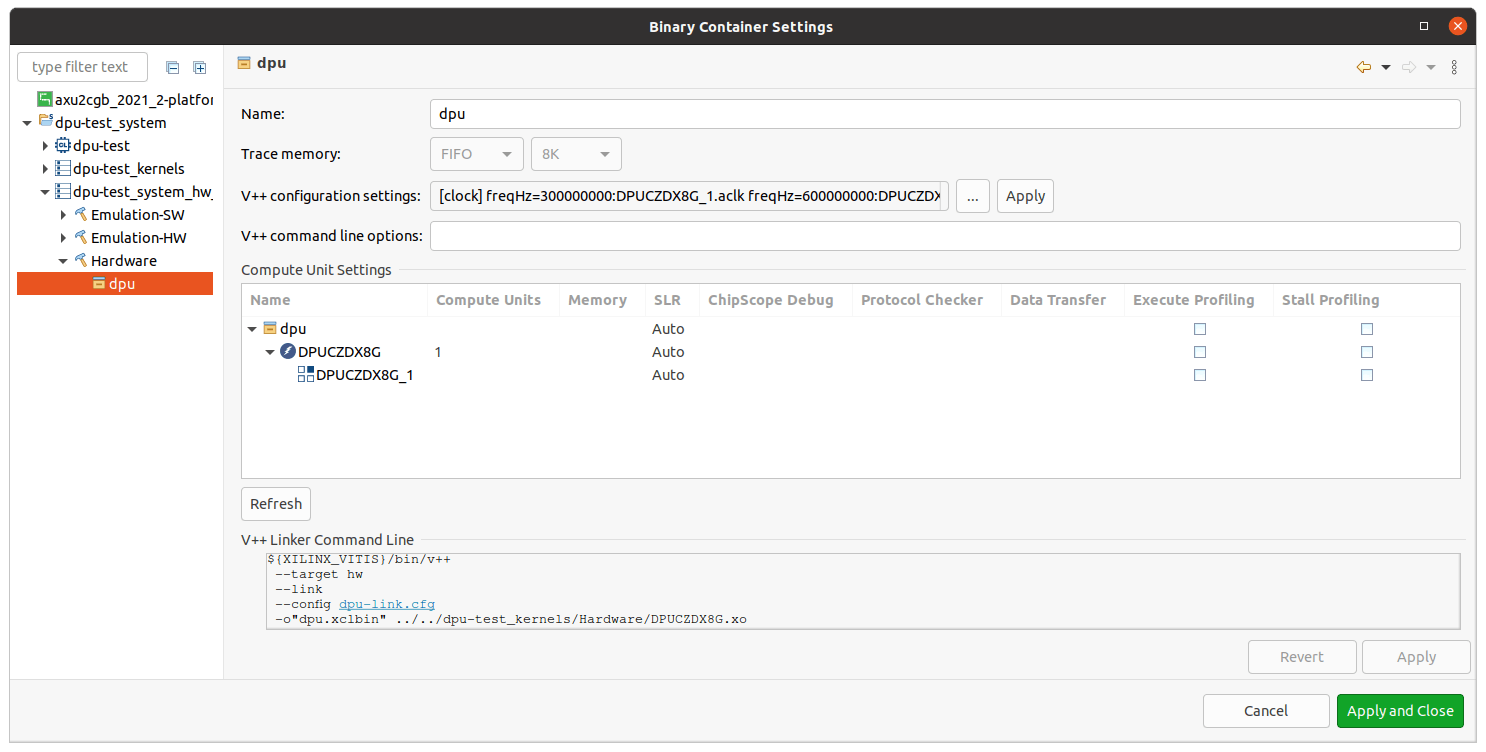

如果我们删除了 DPUCZDX8G 的一个内核实例,我们还需要删除专用于先前删除的第二个实例的所有时钟和连接。

- 转到助手视图。

- 双击dpu-test_system [系统]。

- 展开左侧树面板并找到 dpu-test_system > dpu-test_system_hw_link > Hardware > dpu。

单击...名为V++ configuration settings的行中的按钮。将 V++ 链接器设置窗口内容更改为以下内容:

[clock]

freqHz=300000000:DPUCZDX8G_1.aclk

freqHz=600000000:DPUCZDX8G_1.ap_clk_2

[connectivity]

sp=DPUCZDX8G_1.M_AXI_GP0:HPC0

sp=DPUCZDX8G_1.M_AXI_HP0:HP0

sp=DPUCZDX8G_1.M_AXI_HP2:HP1

单击确定、应用、应用,然后单击应用并关闭。

将自定义 Python 应用程序添加到项目(可选)

现在,我们从命令行界面添加来自 GitHub 存储库的新 python 测试脚本。

- 转到 Ubuntu 终端程序并将目录更改为dpu-test/src 。

- 从我的 (S59MZ) GitHub 帐户中克隆名为test-dpu的存储库。

$ cd platform/dpu-test/src

$ git clone https://github.com/s59mz/test-dpu

$ cd test-dpu

$ git checkout main

$ rm -rf test-dpu/.git

$ cd ../../..

现在我们有了一个新目录test-dpu ,里面有一些测试 python 脚本。

注意:如果您有与 AXU2CGB 板不同的硬件,它使用 SD 卡的 SD0 接口(例如 zcu102 或 zcu104 板),您应该检查mmcblk0 branch 而不是main 。

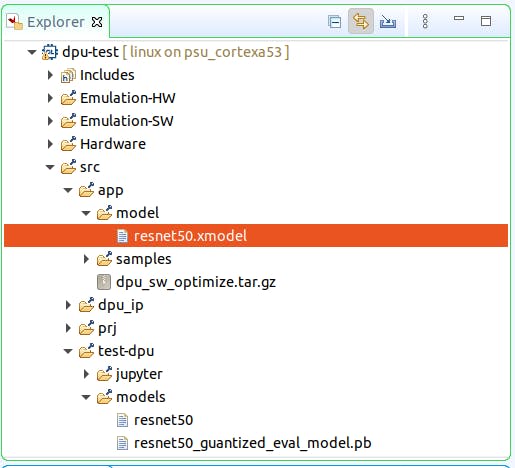

替换旧的 resnet50 型号(可选)

您可以将app/model目录中的resnet50.xmodel替换为重新编译的新模型,因为我们更改了dpu_conf.vh文件中的 DPU 设置。

但仅当您想使用默认包含的 resnet50 模型运行一些 DPU 测试时。GNU Radio 不需要。

在dpu-test/models目录中之前克隆的 GitHub 存储库中已经有重新构建的resnet50.xmodel 。用重建的模型替换旧模型。

$ cd dpu-test/src/app/model

$ rm resnet50.xmodel

$ mv ../../test-dpu/models/resnet50.xmodel .

注意:还有dpu_conf.vh文件应该转到dpu-test_kernels/src/prj/Vitis目录,以防您尚未在上一节中设置 DPU 配置。你可以比较两个文件,应该是一样的。

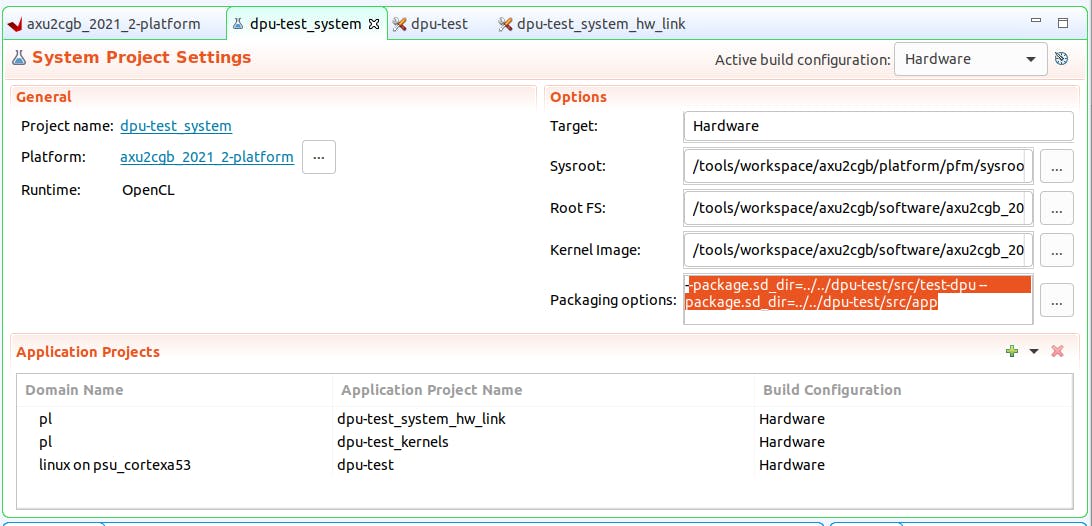

打包

更新打包选项以在SD 卡上添加应用程序和这个新的 test-dpu目录。

- 双击dpu-test_system.sprj

- 单击包选项上的...按钮

- 输入:

--package.sd_dir=../../dpu-test/src/test-dpu --package.sd_dir=../../dpu-test/src/app

点击确定

注意: /test-dpu和--package.sd_dir之间有一个空格

注意:要添加到 src 目录中的新目录名称不应以单词dpu- something 开头。这会导致 Makefile 错误。

构建应用程序

右键单击dpu-test_system[axu2cgb_2021_2-platform]系统项目并选择Build Project 。等待大约一个小时完成。

生成的 SD 卡映像位于dpu-test_system/Hardware/package/sd_card.img。我们的目标板需要那个。

在此构建过程中生成的最重要的文件是dpu.xclbin 。是FPGA二进制映像在FPGA中实现了DPU内核。它位于Hardware目录中,添加到 SD 卡的引导分区并包含在 sd_card.img 映像中。

在 Target 上测试 GNU Radio 平台

准备空的 SD 卡,大小至少 8GB。

为 AXU2CGB 板准备的SD 卡映像也可以从GitHub 存储库下载。

使用 Linux DD命令或用于写入 SD 卡映像的类似程序 (Etcher)将上一步中创建的sd_card.img写入空 SD 卡。

注意:仔细检查= / dev / sd的输出设备......它必须指向SD卡,除非您可以丢失主机上的所有数据。

$ cd axu2cgb/platform/dpu-test_system/Hardware/package

$ sudo dd if=sd_card.img of=/dev/sd?? bs=512; sync

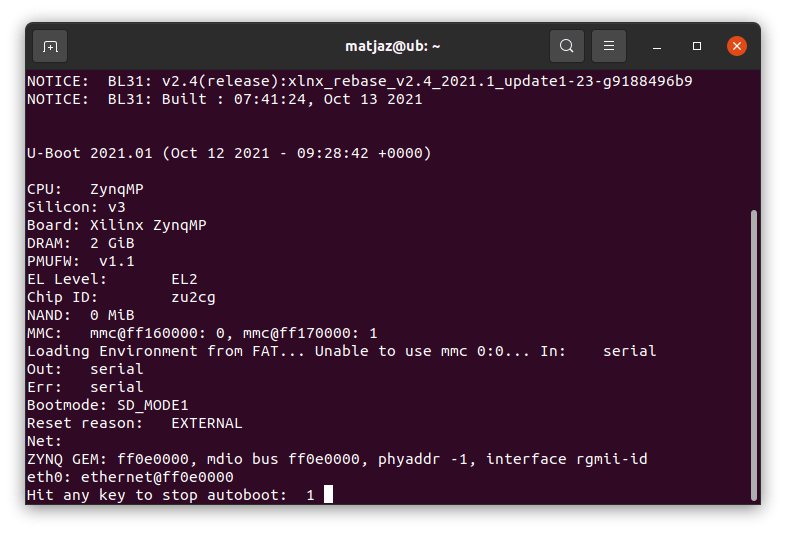

将 SD 卡插入 AXU2CGB 板,通过 USB 电缆将串行控制台连接到主机并运行串行终端程序,例如minicom 。

$ minicom -D /dev/ttyUSB0 -b 115200

将以太网电缆连接到板上。板子和主机应该在同一个局域网中。

给AXU2CGB板加电。U-Boot应该启动,然后是 Linux 内核和 rootfs 文件系统。等待提示。

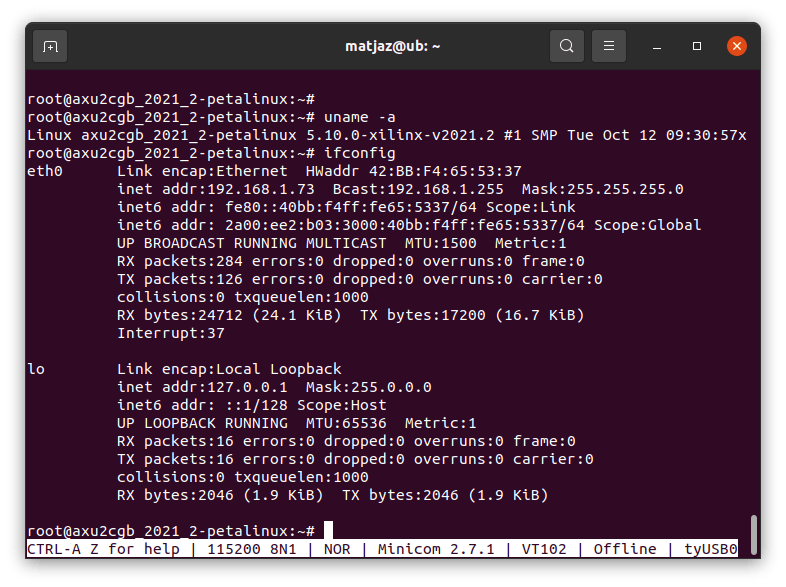

分别通过运行“ uname -a ”和ifconfig Linux 命令检查 Linux 版本和板的 IP 地址。

$ uname -a

$ ifconfig

记下 IP 地址,因为我们需要它来进行SSH -X访问。

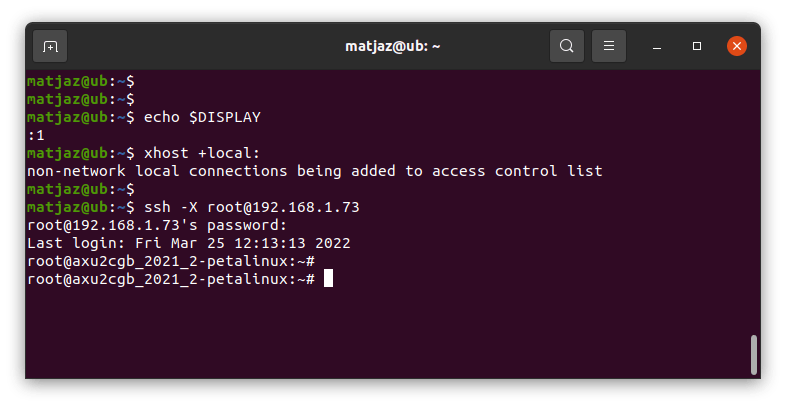

准备主机

现在我们使用主机作为显示器,所以我们准备主机作为X11服务器并使用“ -X ”选项ssh 到板。

在主机计算机上:

- 检查$DISPLAY变量。应该是“ :1 ”。

- 将本地连接添加到访问控制列表。类型:“ xhost +本地:”

- 从主机打开到板的ssh -X会话。

- 以root身份登录,密码为root 。

$ echo $DISPLAY

$ xhost +local:

$ ssh -X root@192.168.1.73

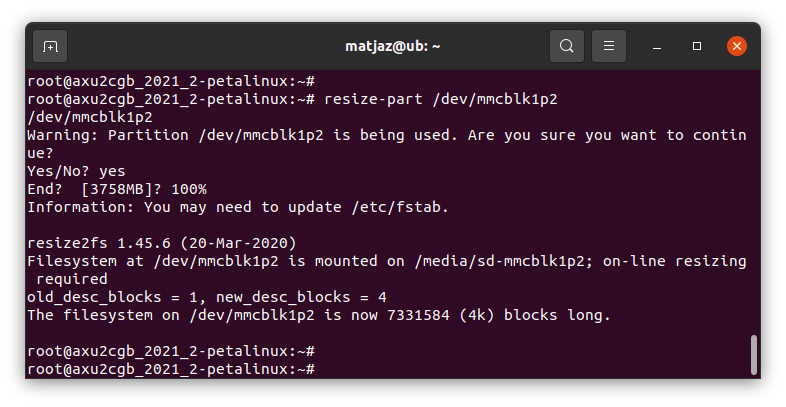

准备目标

首先要做的是调整SD 卡的 EXT4 分区的大小。该命令应该只运行一次。

resize-part /dev/mmcblk1p2

此外,更新数据包管理器。

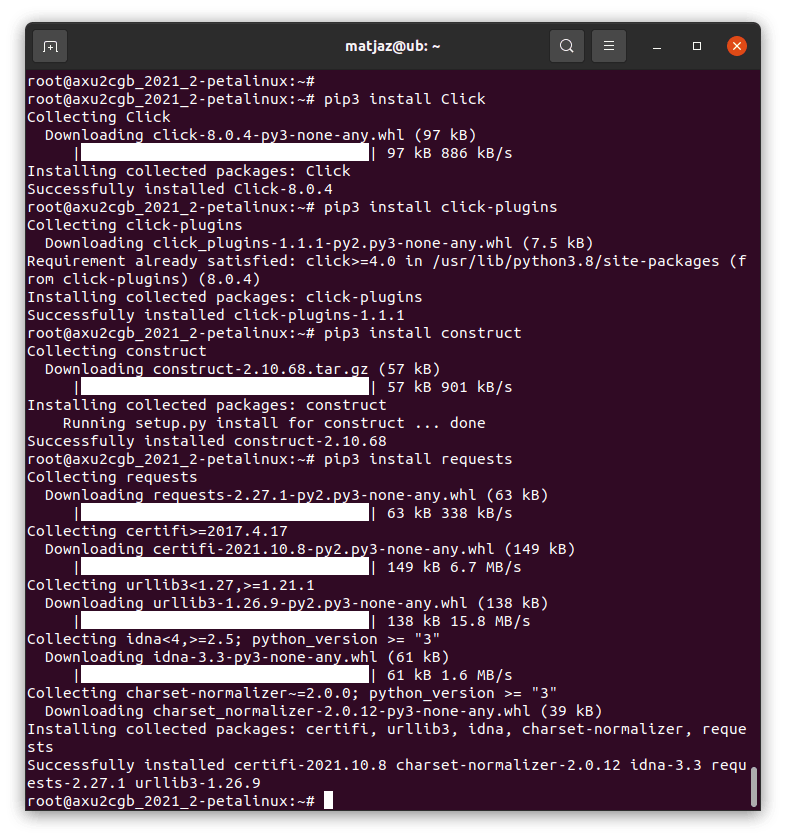

$ dnf update

注意:如果您想为 GNU Radio 构建自己的OOT模块,则应手动安装以下 python 库:

$ pip3 install Click

$ pip3 install click-plugins

注意:要使用 EA4GPZ 的gr-satellites模块解码来自卫星的信号,请安装以下两个附加库:

$ pip3 install construct

$ pip3 install requests

在真实 Target 上测试 DPU 单元

现在,我们可以在板上运行一些测试。

在运行任何测试之前,您应该设置一些系统变量。

对于使用DPU 单元,此变量指向 FPGA 二进制图像:

$ export XLNX_VART_FIRMWARE=/media/sd-mmcblk1p1/dpu.xclbin

为了执行任何使用 DPU 的 C/C++ 程序,此变量指向所需的库:

$ export LD_LIBRARY_PATH=/media/sd-mmcblk1p1/app/samples/lib

对于使用任何 GNU Radio 模块,此变量指向 Python 包的位置:

$ export PYTHONPATH=/usr/lib/python3/dist-packages/

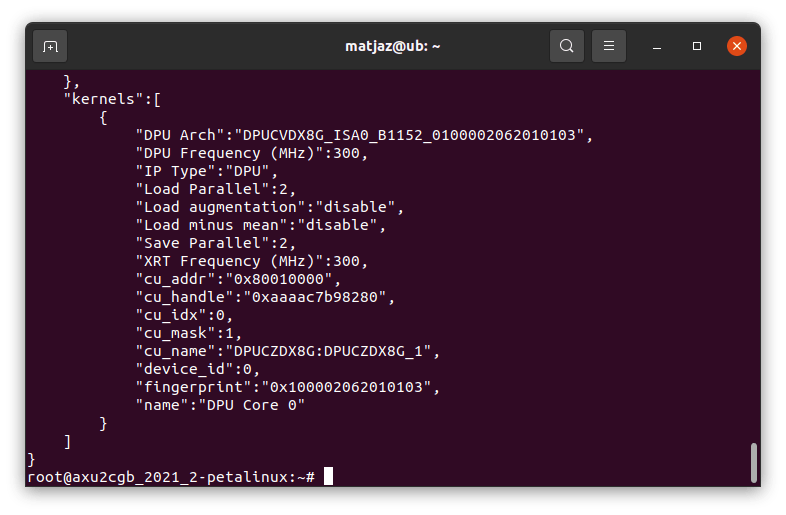

要获取构建您自己的 AI 模型所需的DPU 指纹,可以使用“ xdputil query ”命令:

$ export XLNX_VART_FIRMWARE=/media/sd-mmcblk1p1/dpu.xclbin

$ xdputil query

在控制台打印的近端找到“指纹”:“0x100002062010103 ”参数,并将此参数存储在花括号 {}中,以新创建的arch.json文件。

将此文件存储在主机上的某处。使用Vitis-AI编译 AI 模型需要此文件。

$ echo '{"fingerprint":"0x100002062010103"}' > arch.json

注意:确保文件中包含括号和双引号。

$ cat arch.json

{"fingerprint":"0x100002062010103"}

注意:由于未知原因,Vitis-AI 在创建 dpu-test 应用程序时生成的原始arch.json文件值错误。指纹值以 -203 而不是 -103 结尾。请直接使用从 FPGA 读取的指纹值来编译您自己的模型。

将目录更改为 SD 卡BOOT分区上的test-dpu ,所有需要的测试脚本都位于该目录:

$ cd /media/sd-mmcblk1p1/test-dpu

该目录下有五个 bash 测试脚本,均以“run_ ”前缀开头。

随意探索脚本并检查脚本中的所有系统变量是否都指向正确的位置,尤其是检查 mmcblk 1 p1 或 mmcblk 0 p1 SD 卡分区,具体取决于您选择的硬件平台。

$ ls -l run_*

run_recognize_image.sh

run_test_performance.sh

run_test_accuracy.sh

run_gnuradio.sh

run_rf_classification.sh

运行每个脚本并检查一切是否正常。

最后两个使用 GNU Radio 的测试应该通过ssh -X session 运行,因为它们通过主机上的X11 服务器使用图形显示。

注意:如果重复出现错误,请先尝试重新启动板。

$ reboot -h

图像分类测试

这是 AMD-Xilinx 教程中包含的原始 DPU 测试。测试识别提供图像中的对象。

运行run_recognize_image.sh脚本:

$ pwd

/media/sd-mmcblk1p1/test-dpu

$ ./run_recognize_image.sh

Recognising Unknown Image...

score[688] = 0.999914 text: oscilloscope, scope, cathode-ray oscilloscope, CRO,

score[662] = 1.30062e-05 text: modem,

score[844] = 1.30062e-05 text: switch, electric switch, electrical switch,

score[592] = 1.01292e-05 text: hard disc, hard disk, fixed disk,

score[811] = 7.88864e-06 text: space heater,

/media/sd-mmcblk1p1/test-dpu

如果图片被正确识别(在这种情况下是示波器),则测试通过。随意用不同的图片更改脚本内的图片。

射频调制分类性能测试

该测试测量推理的最大可能帧速率。

运行run_test_performance.sh脚本。

确保 AXU2CGB 板的测量 FPS 约为 500 帧/秒。

$ pwd

/media/sd-mmcblk1p1/test-dpu

$ ./run_test_performance.sh

Number of RF Samples is 2000

FPS=532.79, total RF frames = 2000.00 , time=3.753795 seconds

射频调制分类精度测试

该测试使用给定的测试数据集测量模型的准确性。

运行run_test_accuracy.sh脚本。

确保 top-1 准确度约为 0.53。我们使用了一个基线模型,该模型仅使用 6% 的可用数据集样本进行训练。

$ pwd

/media/sd-mmcblk1p1/test-dpu

$ ./run_test_accuracy.sh

Number of RF Samples Tested is 998

Batch Size is 1

Top1 accuracy = 0.53

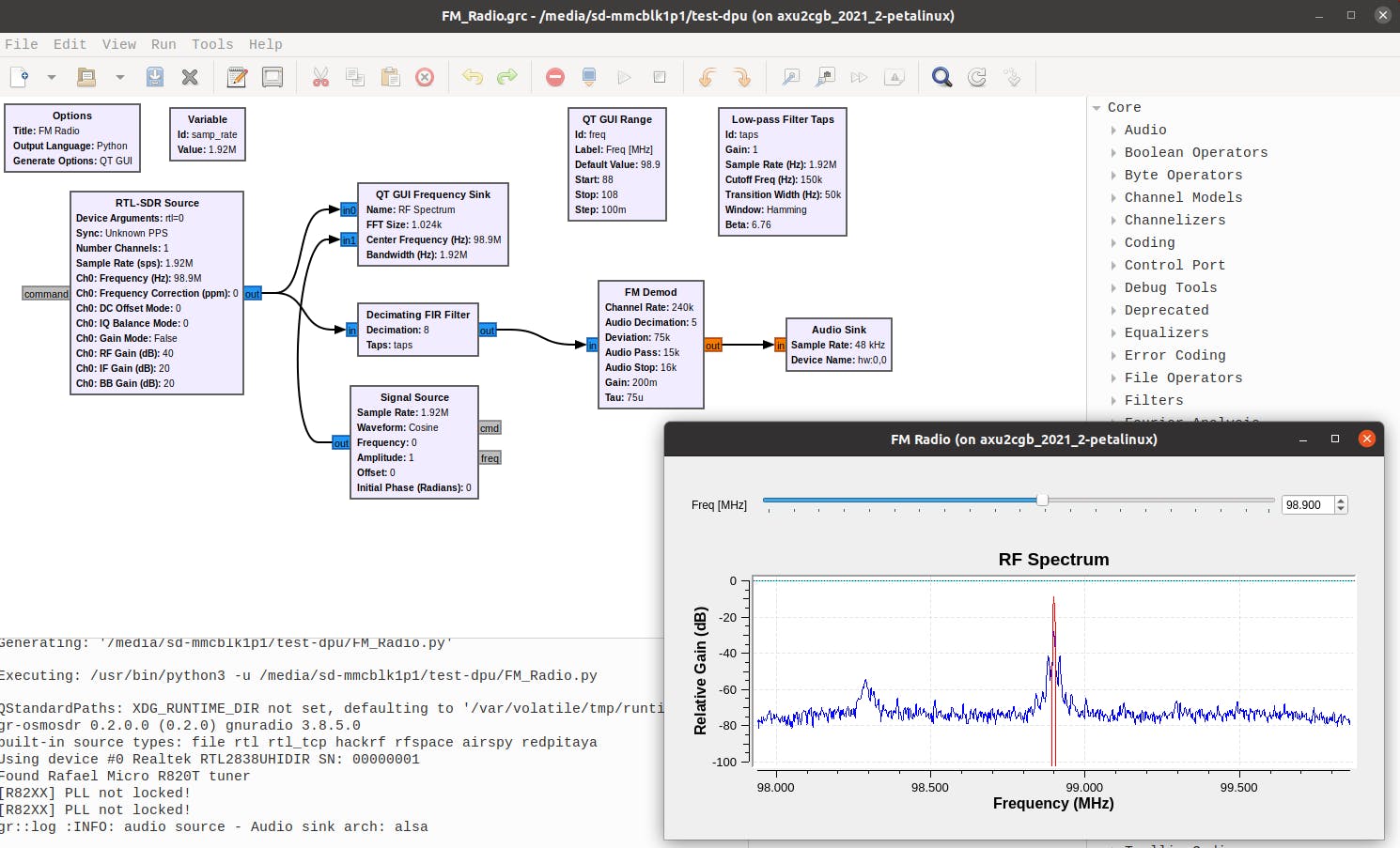

调频收音机测试

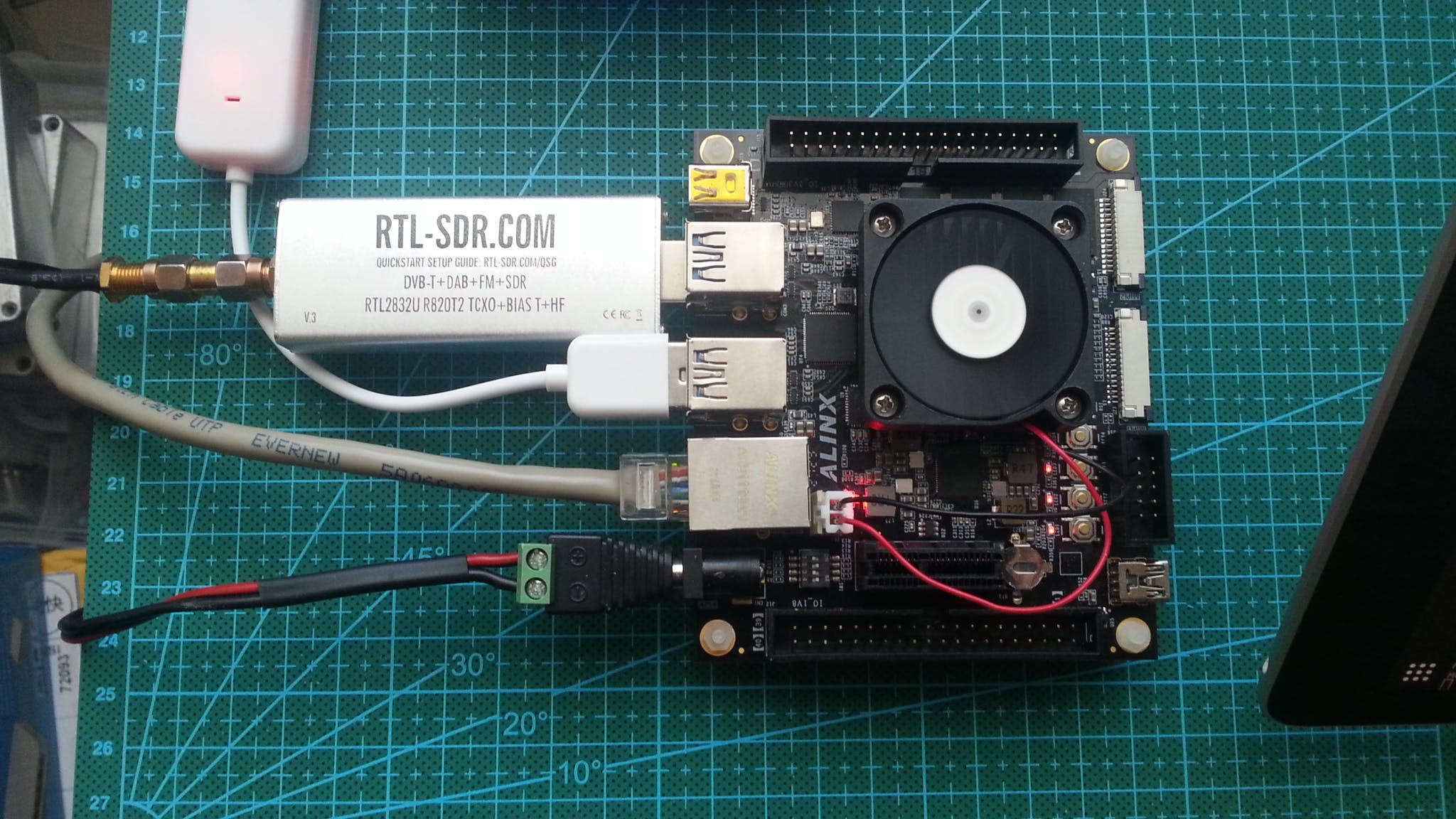

它是一个在 GNU Radio 平台上实现的简单 FM 收音机。该板应已将RTL-SDR USB 加密狗插入 AXU2CGB 板上的可用 USB 端口之一。

RTL-SDR USB dongle 是软件定义的无线电接收器。应将适当的小型天线连接到 RTL-SDR。

此测试使用图形显示,应通过 ssh -X 会话运行。

将 USB 声卡与扬声器或电话连接到声卡的音频插孔输入。也可以将音频路由到 X11 服务器,而无需使用任何 USB 声卡。

一切都连接好后,运行run_gnuradio.sh脚本。

- GNU Radio 将启动。

- 单击上方工具箱上的播放按钮或按键盘上的F6 。

- 将打开一个新的 GUI。忽略警告消息(它只显示一次)。

- 调整新 GUI 的大小以使其更明显。

- 将 GUI 中的频率设置为附近的任何本地 FM 广播电台。

- 您应该在扬声器中听到选定的本地广播电台(如果它们已连接),并在 GUI 小部件中看到接收到的无线电频谱。

要将音频路由到 X11 服务器,请关闭无线电 GUI 并双击Audio Sink块:

- 删除设备名称字段中值为“ hw:0, 0 ”的内容。

- 单击确定,然后再次播放。

- 您现在应该可以听到主机扬声器上的音频了。

随意将频率更改为附近的任何其他 FM 广播电台。

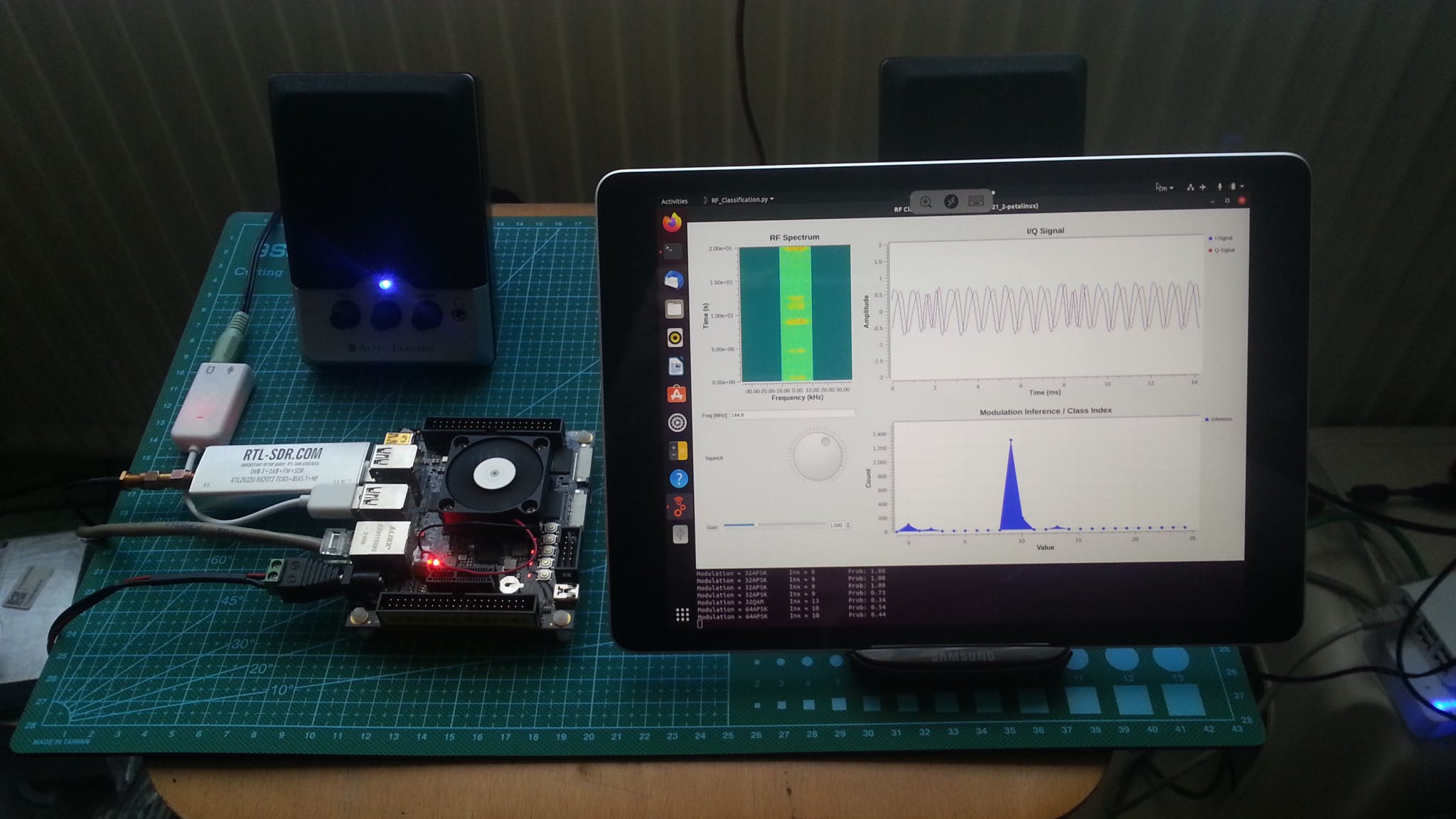

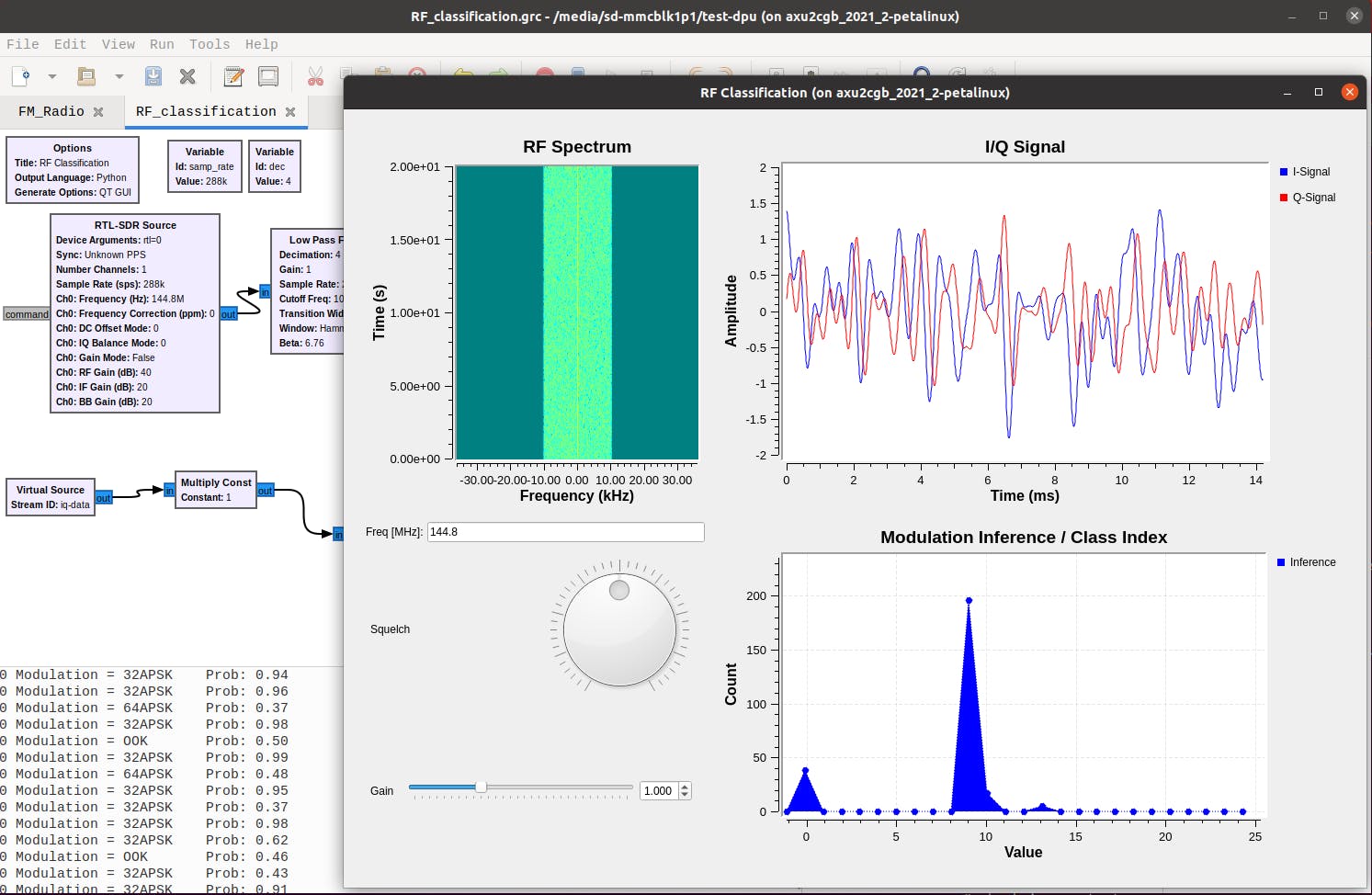

在 GNU Radio 上运行射频调制分类测试

该测试运行在 Python 下运行的 GNU Radio 平台上开发的简单 GUI 应用程序。

该应用程序接收业余无线电爱好者 2m 频段上的信号,并实时预测接收数字信号的调制。对于推理,它使用在板上的 FPGA 中实现的深度学习处理器单元 (DPU)。

该测试使用图形显示并且应该通过 ssh -X 会话运行。

该板应已将RTL-SDR USB 加密狗插入 AXU2CGB 板上的可用 USB 端口之一。

它是一个软件定义的无线电接收器,作为 USB 加密狗。建议将外部 VHF/UHF 天线连接到 RTL-SDR。

将 USB 声卡与扬声器或电话连接到声卡的音频插孔输入。也可以将音频路由到 X11 服务器,无需 USB 声卡。

注意:平板电脑仅作为X11 服务器工作,并显示来自 GNU Radio 的 GUI,在 FPGA 板上运行。

一切都连接好后,运行run_rf_classification.sh脚本。

- 应用程序自动启动。适当调整 GUI 大小。

- SDR 接收器在业余无线电频段上调谐到 144.8 MHz,并在该频段上收听一些随机数字信号。

- 当出现强信号时,它可以显示在瀑布上。

- 此时程序开始预测接收信号的调制。预测的调制打印在 SSH 控制台上,直方图计算所有预测的类索引。

- 分析信号的样本也显示在时域(示波器)中。

AI 模型已包含在应用程序的test-dpu/models/rfClassification.xmodel文件中。它是一个基线模型,仅使用 10 个 epoch 进行训练,并且仅使用数据集中 6% 的可用样本。

下一步

随意构建您自己的模型并在本系列的下一个/最后一个教程中使用更多示例对其进行训练:

- LabView工具包WebSocket-API主机下载 69次下载

- AXU2CGB Zynq UltraScale板上的GNU Radio工具包 第4部分

- AXU2CGB Zynq UltraScale板上的GNU Radio工具包 第1部分

- 如何在arduino IDE上安装STM32的开发板工具包 3次下载

- 布局电源板以将EMI降至最低:第3部分

- 布局电源板以将EMI降至最低:第2部分

- 如何使用KEELOQ3开发工具包作为开发工具来在目标板上仿真和调试固件

- 如何使用入门工具包开发工具在目标板上仿真和调试固件的详细资料概述

- 如何使用PIC32MX1/2/5入门工具包在目标板上仿真和调试固件的详细概述

- 如何使用高性能工具包作为开发工具在目标板上仿真和调试固件

- PIC32以太网入门工具包的中文介绍和使用的详细概述

- 如何使用PIC32MZ嵌入式连接(EC)入门工具包的详细使用说明

- 电压基准如何影响ADC性能,第2部分 10次下载

- 使用触摸传感器的设备的输入和控制,第2部分:控制器和开发包 5次下载

- 多媒体启动工具包

- 软件无线电安全之GNU Radio基础知识 4955次阅读

- NPOI WEG报表工具包简介 1074次阅读

- ADI公司设计工具:ADIsimRF第2部分 1223次阅读

- ADC眼中的虚拟评估,第2部分 822次阅读

- Arm®ML处理器 嵌入式评估工具包介绍 8193次阅读

- 基于Xilinx Zynq ultraScale+ 系列FPGA的AXU2CGB 开发板评测 9735次阅读

- 米尔科技Zynq UltraScale+ MPSoC技术参考手册介绍 3246次阅读

- 北大语言计算与机器学习研究组推出一套全新中文分词工具包pkuseg 3826次阅读

- Xilinx基于ARM的Zynq-7000和Zynq UltraScale+ MPSoC及RFSoC器件是否存在安全漏洞 2686次阅读

- Zynq UltraScale+ MPSoC 上的多个Linux UIO设计 3349次阅读

- 细数工具包Kanzi® UI及Kanzi Connect®其中每个插件实现的功能 1w次阅读

- Ti推出面向Zynq UltraScale+ MPSoC的电源参考设计 3731次阅读

- Adam Taylor玩转MicroZed系列之58:Zynq和PicoBlaze第3部分 1211次阅读

- 无源元件并非真的“无源”:第1部分——电容 2519次阅读

- 混合信号系统接地揭秘之第二部分 1712次阅读

下载排行

本周

- 1山景DSP芯片AP8248A2数据手册

- 1.06 MB | 532次下载 | 免费

- 2RK3399完整板原理图(支持平板,盒子VR)

- 3.28 MB | 339次下载 | 免费

- 3TC358743XBG评估板参考手册

- 1.36 MB | 330次下载 | 免费

- 4DFM软件使用教程

- 0.84 MB | 295次下载 | 免费

- 5元宇宙深度解析—未来的未来-风口还是泡沫

- 6.40 MB | 227次下载 | 免费

- 6迪文DGUS开发指南

- 31.67 MB | 194次下载 | 免费

- 7元宇宙底层硬件系列报告

- 13.42 MB | 182次下载 | 免费

- 8FP5207XR-G1中文应用手册

- 1.09 MB | 178次下载 | 免费

本月

- 1OrCAD10.5下载OrCAD10.5中文版软件

- 0.00 MB | 234315次下载 | 免费

- 2555集成电路应用800例(新编版)

- 0.00 MB | 33566次下载 | 免费

- 3接口电路图大全

- 未知 | 30323次下载 | 免费

- 4开关电源设计实例指南

- 未知 | 21549次下载 | 免费

- 5电气工程师手册免费下载(新编第二版pdf电子书)

- 0.00 MB | 15349次下载 | 免费

- 6数字电路基础pdf(下载)

- 未知 | 13750次下载 | 免费

- 7电子制作实例集锦 下载

- 未知 | 8113次下载 | 免费

- 8《LED驱动电路设计》 温德尔著

- 0.00 MB | 6656次下载 | 免费

总榜

- 1matlab软件下载入口

- 未知 | 935054次下载 | 免费

- 2protel99se软件下载(可英文版转中文版)

- 78.1 MB | 537798次下载 | 免费

- 3MATLAB 7.1 下载 (含软件介绍)

- 未知 | 420027次下载 | 免费

- 4OrCAD10.5下载OrCAD10.5中文版软件

- 0.00 MB | 234315次下载 | 免费

- 5Altium DXP2002下载入口

- 未知 | 233046次下载 | 免费

- 6电路仿真软件multisim 10.0免费下载

- 340992 | 191187次下载 | 免费

- 7十天学会AVR单片机与C语言视频教程 下载

- 158M | 183279次下载 | 免费

- 8proe5.0野火版下载(中文版免费下载)

- 未知 | 138040次下载 | 免费

电子发烧友App

电子发烧友App

创作

创作 发文章

发文章 发帖

发帖  提问

提问  发资料

发资料 发视频

发视频 上传资料赚积分

上传资料赚积分

评论