资料介绍

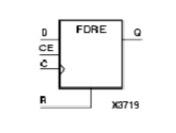

1、源语---FDRE

FDRE代表一个单D型触发器,含的有五个信号分别为: 数据(data,D)、时钟使能(Clock enable,CE)、时钟(Clock)、同步复位(synchronous reset,R)、数据输出(dataout,Q)。当输入的同步复位信号为高时,否决(override)所有输入,并在时钟的上升沿将输出Q为低信号。在时钟的上升沿数据被加载进入D触发器的输入。

FDRE #( .INIT (INITIALISE[0]) ) data_sync_reg1 ( .C (clk), // 同步时钟 .D (data_sync0), //异步数据输入 .Q (data_sync1), //同步数据输出 .CE (1'b1), //时钟使能信号 .R (1'b0) //复位信号输入,高电平有效 );

由于数据可能与时钟存在着不同步的情况,尤其是在对同步精度要求高的场合,一般还是用多次FDRE源语使得数据、控制信号等同步,例如在一个三态网数据同步模块中使用了四个D触发器进行数据同步:

`timescale 1ps / 1ps (* dont_touch = "yes" *) module tri_mode_ethernet_mac_0_sync_block #( parameter INITIALISE = 1'b0, parameter DEPTH = 5 ) ( input clk, // clock to be sync'ed to input data_in, // Data to be 'synced' output data_out // synced data ); // Internal Signals wire data_sync0; wire data_sync1; wire data_sync2; wire data_sync3; wire data_sync4; (* ASYNC_REG = "TRUE", SHREG_EXTRACT = "NO" *) FDRE #( .INIT (INITIALISE[0]) ) data_sync_reg0 ( .C (clk), .D (data_in), .Q (data_sync0), .CE (1'b1), .R (1'b0) ); (* ASYNC_REG = "TRUE", SHREG_EXTRACT = "NO" *) FDRE #( .INIT (INITIALISE[0]) ) data_sync_reg1 ( .C (clk), .D (data_sync0), .Q (data_sync1), .CE (1'b1), .R (1'b0) ); (* ASYNC_REG = "TRUE", SHREG_EXTRACT = "NO" *) FDRE #( .INIT (INITIALISE[0]) ) data_sync_reg2 ( .C (clk), .D (data_sync1), .Q (data_sync2), .CE (1'b1), .R (1'b0) ); (* ASYNC_REG = "TRUE", SHREG_EXTRACT = "NO" *) FDRE #( .INIT (INITIALISE[0]) ) data_sync_reg3 ( .C (clk), .D (data_sync2), .Q (data_sync3), .CE (1'b1), .R (1'b0) ); (* ASYNC_REG = "TRUE", SHREG_EXTRACT = "NO" *) FDRE #( .INIT (INITIALISE[0]) ) data_sync_reg4 ( .C (clk), .D (data_sync3), .Q (data_sync4), .CE (1'b1), .R (1'b0) ); assign data_out = data_sync4; endmodule

本文转载自:https://www.cnblogs.com/luxinshuo/p/11913988.html,转载此文目的在于传播相关技术知识,版权归原作者所有,如涉及侵权,请联系小编删除(联系邮箱:service@eetrend.com )。

- Xilinx-ISE9.x-FPGA-CPLD设计指南合集 76次下载

- XILINX ARTIX7系列FPGA芯片产品目录 26次下载

- Xilinx-DCM的使用方法技巧 12次下载

- 基于FDRE的节水灌溉智能控制系统 26次下载

- Xilinx的时序设计与约束资料详细说明 32次下载

- 如何使用Xilinx的FPGA对高速PCB信号实现优化设计 25次下载

- Xilinx 7 系列FPGA中的Serdes总结 25次下载

- XILINX中的zynq ultrascale plus产品选择指南 5次下载

- xilinx FPGA的IOB使用教程说明 12次下载

- xilinx的FPGA芯片选型手册免费下载 49次下载

- xilinx实验板原理图 235次下载

- Xilinx下载电缆原理图 114次下载

- xilinx ISE设计套装10.1下载 1915次下载

- Xilinx Solutions for Automotiv 14次下载

- usb xilinx源代码 41次下载

- Xilinx fpga芯片系列有哪些 238次阅读

- Xilinx FPGA IP之Block Memory Generator功能概述 740次阅读

- 仿真Xilinx网表 3124次阅读

- Xilinx FPGA的FMC介绍 5125次阅读

- 米尔科技Xilinx下载线介绍 1923次阅读

- Xilinx品牌FPGA使用的三种证书 3979次阅读

- 基于QEMU系统模拟器Xilinx/QEMU的运行与调试 8411次阅读

- xilinx公司的代理商有哪些_十大xilinx公司的代理商推荐 3.8w次阅读

- Xilinx设备的驱动程序 7711次阅读

- 基于Xilinx的软件工程的创建 1395次阅读

- Xilinx SDK使用教程 4272次阅读

- 记利用compxlibgui工具编译Xilinx库 1274次阅读

- 如何在设计阶段考虑降低XILINX的功耗 1919次阅读

- Xilinx DPD 解决方案使用经验(七) 3006次阅读

- 说说赛灵思(Xilinx )的FPGA 高速串行收发器 5961次阅读

下载排行

本周

- 1电子电路原理第七版PDF电子教材免费下载

- 0.00 MB | 1491次下载 | 免费

- 2单片机典型实例介绍

- 18.19 MB | 95次下载 | 1 积分

- 3S7-200PLC编程实例详细资料

- 1.17 MB | 27次下载 | 1 积分

- 4笔记本电脑主板的元件识别和讲解说明

- 4.28 MB | 18次下载 | 4 积分

- 5开关电源原理及各功能电路详解

- 0.38 MB | 11次下载 | 免费

- 6100W短波放大电路图

- 0.05 MB | 4次下载 | 3 积分

- 7基于单片机和 SG3525的程控开关电源设计

- 0.23 MB | 4次下载 | 免费

- 8基于AT89C2051/4051单片机编程器的实验

- 0.11 MB | 4次下载 | 免费

本月

- 1OrCAD10.5下载OrCAD10.5中文版软件

- 0.00 MB | 234313次下载 | 免费

- 2PADS 9.0 2009最新版 -下载

- 0.00 MB | 66304次下载 | 免费

- 3protel99下载protel99软件下载(中文版)

- 0.00 MB | 51209次下载 | 免费

- 4LabView 8.0 专业版下载 (3CD完整版)

- 0.00 MB | 51043次下载 | 免费

- 5555集成电路应用800例(新编版)

- 0.00 MB | 33562次下载 | 免费

- 6接口电路图大全

- 未知 | 30320次下载 | 免费

- 7Multisim 10下载Multisim 10 中文版

- 0.00 MB | 28588次下载 | 免费

- 8开关电源设计实例指南

- 未知 | 21539次下载 | 免费

总榜

- 1matlab软件下载入口

- 未知 | 935053次下载 | 免费

- 2protel99se软件下载(可英文版转中文版)

- 78.1 MB | 537793次下载 | 免费

- 3MATLAB 7.1 下载 (含软件介绍)

- 未知 | 420026次下载 | 免费

- 4OrCAD10.5下载OrCAD10.5中文版软件

- 0.00 MB | 234313次下载 | 免费

- 5Altium DXP2002下载入口

- 未知 | 233046次下载 | 免费

- 6电路仿真软件multisim 10.0免费下载

- 340992 | 191183次下载 | 免费

- 7十天学会AVR单片机与C语言视频教程 下载

- 158M | 183277次下载 | 免费

- 8proe5.0野火版下载(中文版免费下载)

- 未知 | 138039次下载 | 免费

电子发烧友App

电子发烧友App

创作

创作 发文章

发文章 发帖

发帖  提问

提问  发资料

发资料 发视频

发视频 上传资料赚积分

上传资料赚积分

评论