资料介绍

在多CPU的分布式信号处理系统中,往往涉及CPU间的通讯与数据交换,大数据量的数据传输一般采用DMA方式,而小数据量的数据交换采用并行接口则比较快速灵活。因此,对于传输速度要求较高的DSP间的小数据量的数据交换及通讯来说,要提高DSP的工作效率,不仅要求并行接口的响应快,而且必须采用异步方式以免相互等待。本文介绍了采用CYPRESS公司的FIFO芯片CY7C419来实现DSP间的双向并行异步通讯接口。该方法不仅比用TTL锁存器的方式速度快,而且译码逻辑简单,另外,由于FIFO芯片有一定的深度(256个),因此,在少于256个数据传输时,可实现零等待时间。

1 FIFO芯片简介

全满(FF)和全空(EF)标志用以防止数据溢出或不足;

扩展输入(XI)、扩展输出(X0)、首次装载(FL):用以实现无限的宽度及深度扩展,深度扩展技术可使操纵控制信号从一个元件并行传至另一个元件,因而消除了传输延迟的串行附加,其最高读、写速度可达50MHz,读写信号低电平有效;

当CY7C419独立使用或多片实现宽度扩展结构时,半空标志(HF)输出有效,在深度扩展结构中,该此脚输出扩展输出信息(XO)并告知下一个FIFO;

D0~D8为数据输入,Q0~Q8为数据输出。

R、W及MR分别为读、写及复位信号的输入端,它们均为低电平有效。

2 硬件结构与通讯流程

2.1 硬件结构

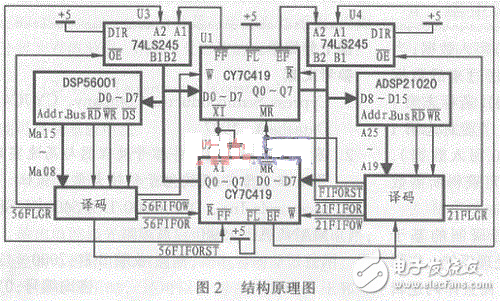

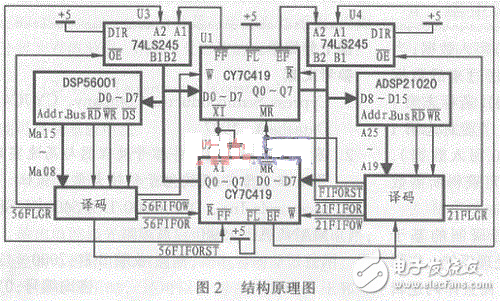

利用FIFO实现DSP间双向并行异步通讯的结构原理如图2所示。DSP56001和ADSP21020分别树熊美国Motorola和ADI公司的DSP芯片。两个CY7C419芯片U1、U2分别用于DSP56001和ADSP21020间双向并行接口的一个方向,其中U1用于完成DSP56001向ADSP21020的数据传送,U2则用于完成ADSP21020向DSP56001的数据传送。U1的全满标志(FF)与U2的全空标志(EF)通过缓冲器74LS245与DSP56001的数据总线相连,该缓冲器被映射为DSP56001数据区的一个地址单元(0x600),因此,DSP56001通过对该地址单元的读操作便可获知U1是否已写满以及U2是否有数所要读。同理,U2的全志(FF)与U1的全空标志(EF)通过一缓冲器74LS245连于ADSP21020的数据总线,该片74LS245补映射为ADSP21020数据区的一个地址单元(身份地址+0x100000),这样ADSP21020通过对该地址单元的读操作也可获知U2是否已写满以及U1是否有数据要读。另外,DSP56001对U1的写操作、对U2的读操作映射为对其数据存储区一个地址单元(0x200)的写、读操作;而ADSP21020对U2的写操作和对U1的读操作则被映射为对其数据存储区地址单元(身份地址+0x180000)的写、读操作。两个DSP芯睡均可同时对U1、U2进行复位操作。

DSP56001对双向口的读56FIFOR、写56FIFOW、复位56FIFORST及对标志口状态56FLGR的读信号可由DSP56001的地址线与读写信号译码获得;ADSP21020对双向口的读21FIFOR、写21FIFOW、复位56FIFORST及对标志口状态56FLGR的读信号则可由ADSP21020的地址线与读写信号译码获得。各译码输出的逻辑表达式如下:

56FIFOR=AdEn+Ma10+Ma9+MRD

(映射地址为:0x200)

56FIFOW=AdEn+Ma10+Ma9+MWR

(映射地址为:0x200)

56FIFOORST=AdEn+Ma10+Ma9+MWR

(映射地址为:0x400)

56FLGR=AdEn+Ma10+Ma9+MRD

(映射地址为:0x600)

AdEn=DS+Ma15+Ma14+Ma13+Ma12+Ma11

21FIFOR=IDMAT+A21+A20+A19+RD

(映射地址为:身份地址+0x180000)

21FIFOW=IDMAT+A21+A20+A19+WR

(映射地址为:身份地址+0x180000)

FIFORST=(IDMAT+A21+A20+A19+WR)56FIFORST

(映射地址为:身份地址+0x200000)

21FLGR=IDMAT+A21+A20+A19+RD

(映射地址为:身份地址+0x100000)

1 FIFO芯片简介

全满(FF)和全空(EF)标志用以防止数据溢出或不足;

扩展输入(XI)、扩展输出(X0)、首次装载(FL):用以实现无限的宽度及深度扩展,深度扩展技术可使操纵控制信号从一个元件并行传至另一个元件,因而消除了传输延迟的串行附加,其最高读、写速度可达50MHz,读写信号低电平有效;

当CY7C419独立使用或多片实现宽度扩展结构时,半空标志(HF)输出有效,在深度扩展结构中,该此脚输出扩展输出信息(XO)并告知下一个FIFO;

D0~D8为数据输入,Q0~Q8为数据输出。

R、W及MR分别为读、写及复位信号的输入端,它们均为低电平有效。

2 硬件结构与通讯流程

2.1 硬件结构

利用FIFO实现DSP间双向并行异步通讯的结构原理如图2所示。DSP56001和ADSP21020分别树熊美国Motorola和ADI公司的DSP芯片。两个CY7C419芯片U1、U2分别用于DSP56001和ADSP21020间双向并行接口的一个方向,其中U1用于完成DSP56001向ADSP21020的数据传送,U2则用于完成ADSP21020向DSP56001的数据传送。U1的全满标志(FF)与U2的全空标志(EF)通过缓冲器74LS245与DSP56001的数据总线相连,该缓冲器被映射为DSP56001数据区的一个地址单元(0x600),因此,DSP56001通过对该地址单元的读操作便可获知U1是否已写满以及U2是否有数所要读。同理,U2的全志(FF)与U1的全空标志(EF)通过一缓冲器74LS245连于ADSP21020的数据总线,该片74LS245补映射为ADSP21020数据区的一个地址单元(身份地址+0x100000),这样ADSP21020通过对该地址单元的读操作也可获知U2是否已写满以及U1是否有数据要读。另外,DSP56001对U1的写操作、对U2的读操作映射为对其数据存储区一个地址单元(0x200)的写、读操作;而ADSP21020对U2的写操作和对U1的读操作则被映射为对其数据存储区地址单元(身份地址+0x180000)的写、读操作。两个DSP芯睡均可同时对U1、U2进行复位操作。

DSP56001对双向口的读56FIFOR、写56FIFOW、复位56FIFORST及对标志口状态56FLGR的读信号可由DSP56001的地址线与读写信号译码获得;ADSP21020对双向口的读21FIFOR、写21FIFOW、复位56FIFORST及对标志口状态56FLGR的读信号则可由ADSP21020的地址线与读写信号译码获得。各译码输出的逻辑表达式如下:

56FIFOR=AdEn+Ma10+Ma9+MRD

(映射地址为:0x200)

56FIFOW=AdEn+Ma10+Ma9+MWR

(映射地址为:0x200)

56FIFOORST=AdEn+Ma10+Ma9+MWR

(映射地址为:0x400)

56FLGR=AdEn+Ma10+Ma9+MRD

(映射地址为:0x600)

AdEn=DS+Ma15+Ma14+Ma13+Ma12+Ma11

21FIFOR=IDMAT+A21+A20+A19+RD

(映射地址为:身份地址+0x180000)

21FIFOW=IDMAT+A21+A20+A19+WR

(映射地址为:身份地址+0x180000)

FIFORST=(IDMAT+A21+A20+A19+WR)56FIFORST

(映射地址为:身份地址+0x200000)

21FLGR=IDMAT+A21+A20+A19+RD

(映射地址为:身份地址+0x100000)

下载该资料的人也在下载

下载该资料的人还在阅读

更多 >

- 基于McBSP实现DSP与串行Flash之间的接口通讯

- DSP间的双向并行异步通讯接口解析 5次下载

- 基于FIFO实现DSP间的双向并行异步通讯的方法 0次下载

- 基于PC机与DSP之间的并行通讯技术 1次下载

- 基于CY7C68013A的USB接口系统设计 43次下载

- 基于CY7C68013A的FPGA配置和通信接口设计 175次下载

- 基于USB2.0芯片CY7C68013的高速数据通信接口设计 177次下载

- 基于CY7C68013的高速数据通信接口设计 69次下载

- 基于TL16C752B的DSP通用异步串行接口设计 98次下载

- DSP核信号采集系统通讯接口设计

- PC机与DSP之间的并行通讯技术

- DSP核信号采集系统通讯接口设计

- 双口RAM CY7C025 实现DSP间的高速数据通信

- 基于CY7C63723/CY7C63722芯片的鼠标电路图及

- CY7C4225/CY7C4235/CY7C4245 pdf

- 四种PLC间跨网段通讯的方法 2.3k次阅读

- 基于XC95108芯片实现DSP和ARM的并行通信系统的设计 5.7k次阅读

- 基于DSP芯片实现异步串行通信系统的软硬件设计 3.6k次阅读

- 基于DSP实现异步串行数据通讯系统的应用设计 3.3k次阅读

- 基于CY7C68033和TMS320DM6437芯片实现高速图像采集处理系统的设计 3.4k次阅读

- 基于TLl6C550C实现数字信号处理器与PC机串行通信的应用设计 2.1k次阅读

- 采用PDIUSBD12芯片和ADuC812芯片实现串行总线接口设计 2.2k次阅读

- 通过CY7C68013微控制器实现数据低速控制、高速传输的设计 5.9k次阅读

- 微雪电子CY7C68013A高速USB通信模块简介 4k次阅读

- 如何实现ABB机器人和视觉系统间的TCP/IP通讯呢? 2.4w次阅读

- 通过EMIF接口控制各种芯片的复杂系统设计实现 1.4w次阅读

- 如何利用LUT来实现FPGA中的DSP功能 1.4w次阅读

- 基于CPLD的高速数据采集系统的实现 2k次阅读

- 利用异步通信芯片16C552实现PC机与DSP的串行通讯 2k次阅读

- 多路异步串行通信系统在光纤陀螺组合中的设计与实现 1.1k次阅读

下载排行

本周

- 1冷柜-电气控制系统讲解

- 13.68 MB | 4次下载 | 10 积分

- 2安川A1000变频器中文版说明书

- 20.16 MB | 3次下载 | 3 积分

- 3直流电路的组成和基本定律

- 1.67 MB | 2次下载 | 免费

- 4丹佛斯2800系列变频器说明书

- 8.00 MB | 1次下载 | 5 积分

- 5PC8011同步开关型降压3.5A单节锂电池充电管理电路技术手册

- 0.74 MB | 1次下载 | 免费

- 6ES7243E+ES8311音频录制与播放电路资料

- 0.06 MB | 1次下载 | 5 积分

- 7SDM02 激光测距模块产品手册

- 0.43 MB | 1次下载 | 免费

- 8SDFM 激光测距模块模组手册

- 0.54 MB | 1次下载 | 免费

本月

- 1CH341编程器软件NeoProgrammer_2.2.0.10

- 20.47 MB | 170次下载 | 1 积分

- 22025智能家居传感器市场分析及创新应用

- 3.11 MB | 43次下载 | 免费

- 3RV1126B系列开发板产品资料

- 4.19 MB | 18次下载 | 免费

- 4CH341编程软件下载

- 2.50 MB | 16次下载 | 5 积分

- 5全志系列-米尔基于T153核心板开发板 四核异构、3路千兆网,赋能多元化工业场景

- 3.05 MB | 12次下载 | 免费

- 6【开源】60余套STM32单片机、嵌入式Linux、物联网、人工智能项目案例及入门学习资源包

- 10.55 MB | 8次下载 | 免费

- 7冷柜-电气控制系统讲解

- 13.68 MB | 4次下载 | 10 积分

- 8特斯拉MODEL S车载充电机主电路回路原理图

- 0.81 MB | 4次下载 | 3 积分

总榜

- 1matlab软件下载入口

- 未知 | 935137次下载 | 10 积分

- 2开源硬件-PMP21529.1-4 开关降压/升压双向直流/直流转换器 PCB layout 设计

- 1.48MB | 420064次下载 | 10 积分

- 3Altium DXP2002下载入口

- 未知 | 233094次下载 | 10 积分

- 4电路仿真软件multisim 10.0免费下载

- 340992 | 191448次下载 | 10 积分

- 5十天学会AVR单片机与C语言视频教程 下载

- 158M | 183356次下载 | 10 积分

- 6labview8.5下载

- 未知 | 81604次下载 | 10 积分

- 7Keil工具MDK-Arm免费下载

- 0.02 MB | 73824次下载 | 10 积分

- 8LabVIEW 8.6下载

- 未知 | 65991次下载 | 10 积分

电子发烧友App

电子发烧友App

创作

创作 发文章

发文章 发帖

发帖  提问

提问  发资料

发资料 发视频

发视频 上传资料赚积分

上传资料赚积分

评论