游戏爱好者或者硬件爱好者肯定都对显卡有一定的了解,显卡一般插在主板上的扩展槽上面,显卡和CPU交互的方式就是通过PCIE协议,现在常见的扩展槽就是PCIE槽,很多人了解PCIE但也有很多人只是听过不知道具体的功能含义,今天我们就来浅谈下PCIE。

PCIE的发展史

PCIExpress(PCIe)的发展历史可以追溯到PCI(Peripheral Component Interconnect)的起源。PCI是Intel于1991年提出的一种计算机总线标准,主要用于计算机连接其外围设备,如硬盘控制器、声卡、显卡和网卡等。这些设备都使用PCI插槽来连接到计算机的主板上。随着Intel Pentium处理器的诞生,PCI总线得以迅速发展。

最初的PCI总线工作在33MHz频率之下,传输带宽达到132MB/s,这基本上满足了当时处理器的发展需要。然而,随着对更高性能的要求,PCI总线技术也在不断发展。后来提出了将PCI总线的频率提升到66MHz,使得传输带宽能达到264MB/s。

然而,PCI总线速率的瓶颈逐渐显现,特别是在服务器和工作站中,高速磁盘和网络适配器对更高带宽的需求日益迫切。为了满足这种需求,PCI技术开始往更高速率的方向发展,形成了PCI-X新总线标准。PCI-X最大支持到64bit/533M,但在其第二代之后,仍存在一定的局限性。

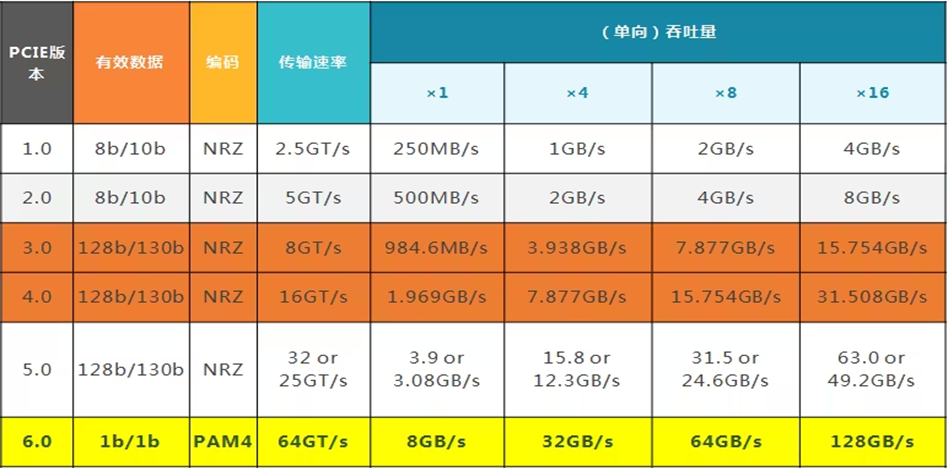

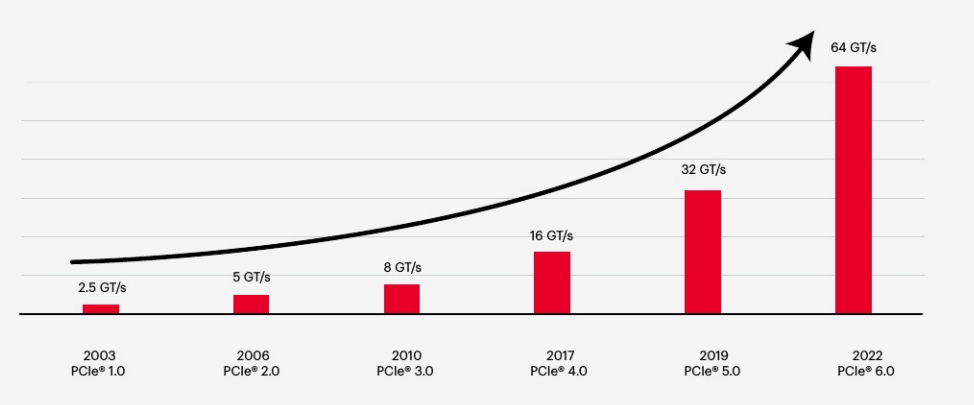

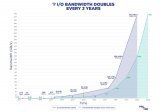

随后,PCIe作为PCI的串行总线版本被推出。从2003年开始,PCIe标准不断得到更新和升级。PCIe 1.0在2003年推出,支持更高的数据传输速率。随后,PCIe 2.0在2007年推出,进一步提升了传输速率。然而,之后几年PCIe的发展相对缓慢,直到2010年PCIe 3.0的推出,它支持更高的速率,最高可以达到8GT/s。

2017年,PCIe 4.0标准发布,进一步提升了PCI Express总线的带宽,最高可以达到16GT/s。紧接着,2019年PCIe5.0标准发布,成为当时最新的PCI Express标准,最高可以达到32GT/s的传输速率。

2021年,PCI-SIG 组织发布PCIe 6.0 是最新一代的 PCI Express 接口标准,速率达到64GT/s。

而在最近的2024年,PCI-SIG组织已经公布了PCIe 7.0标准。根据这一标准,PCIe 7.0将在一条通道(x1)上单向实现128GT/s或128Gbps速率。新的规范预计在2025年正式推行。在x16双向传输模式下,PCIe 7.0的速率高达512GB/s,这对于云端应用、大数据中心等领域来说,无疑是一个巨大的飞跃。

总的来说,PCIe的发展历史体现了计算机技术的不断进步和发展,从最初的并行总线到现在的串行总线,从较低的传输速率到如今的极高传输速率,满足了不断增长的数据处理和传输需求。

PCIE历代速率一览表

PCIE的使用场景

PCIe(Peripheral Component Interconnect Express)因其高带宽、低延迟和灵活性等特点,在众多计算和数据密集型场景中广泛应用。以下列举了一些典型的PCIe使用场景:

图形处理单元(GPU显卡):

1、游戏和图形渲染:PCIe插槽用于连接高性能显卡,为桌面和工作站提供高质量的游戏画面渲染和三维建模能力。

GPU加速卡通过PCIe接口与主机相连,用于大规模并行计算,加速机器学习模型的训练过程。

高速存储:

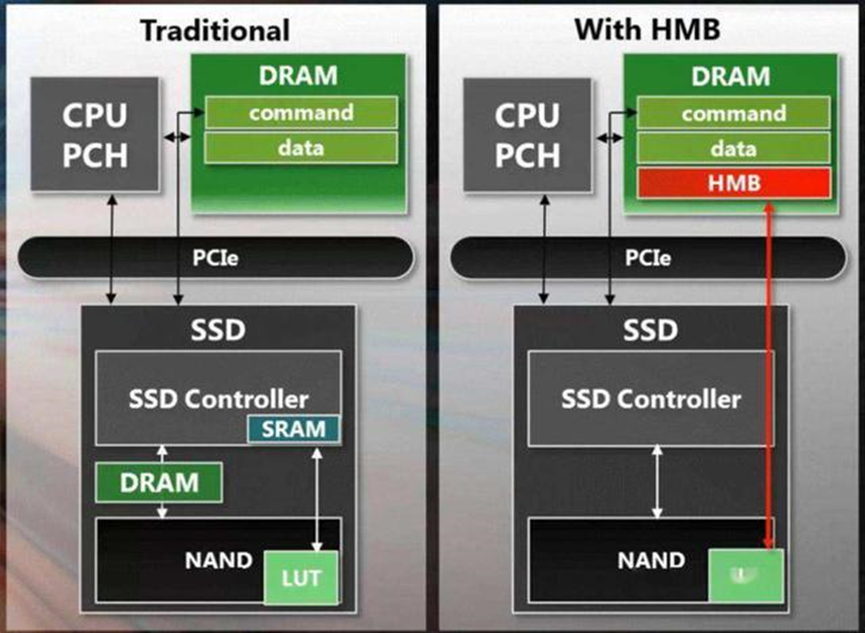

1、NVMe SSD:

PCIe SSD(非易失性内存express)可以利用PCIe通道直接与CPU通信,提供极高的读写速度,用于大型数据库、高性能计算集群以及对存储速度要求极高的应用程序。

网络接口卡(NIC):

高速网络适配器通过CIe接口接入服务器或工作站,实现万兆或更高速度的以太网连接,满足数据中心内部或互联网之间的高速数据传输需求。

加速卡与协处理器:

FPGA加速卡、智能网卡、加密/解密加速卡等通过PCIe连接到系统,提供特定领域的加速计算,如金融交易、密码破解、大数据分析等。

高级的多通道音频和视频输入输出设备通常使用PCIe接口,以实现高清视频流的实时处理和传输。

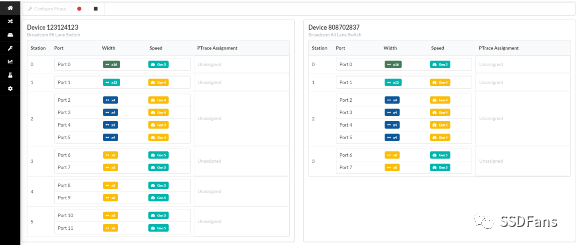

科研仪器与工业控制:

在实验室环境和工业自动化领域,高端测量设备和控制器可通过PCIe接口与计算机整合,实现高效的数据采集和处理。

总之,PCIe在任何需要高速、低延迟数据交换的场合都有广泛的应用,尤其是那些需要大量并发数据处理、高速存取或高吞吐量网络连接的场景。随着PCIe规范的持续演进,其带宽和性能不断提升,进一步拓宽了其在现代计算架构中的应用范围。

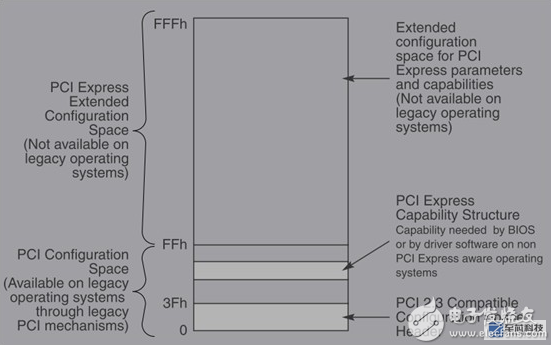

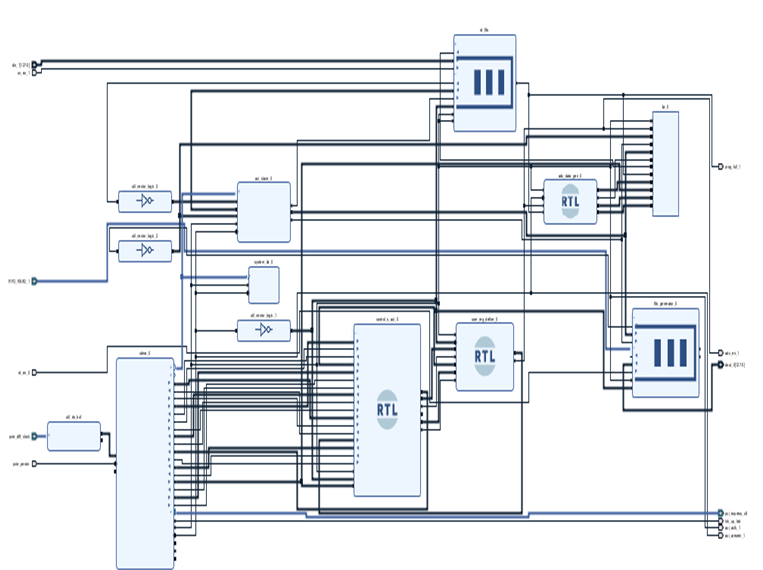

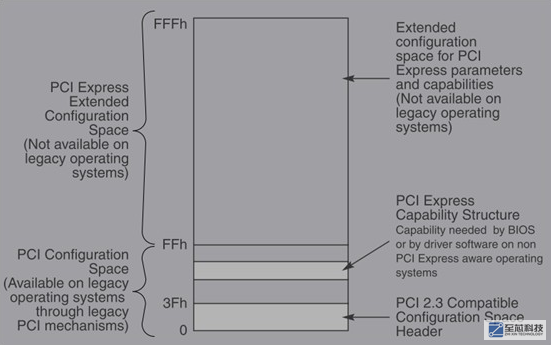

PCIE的架构

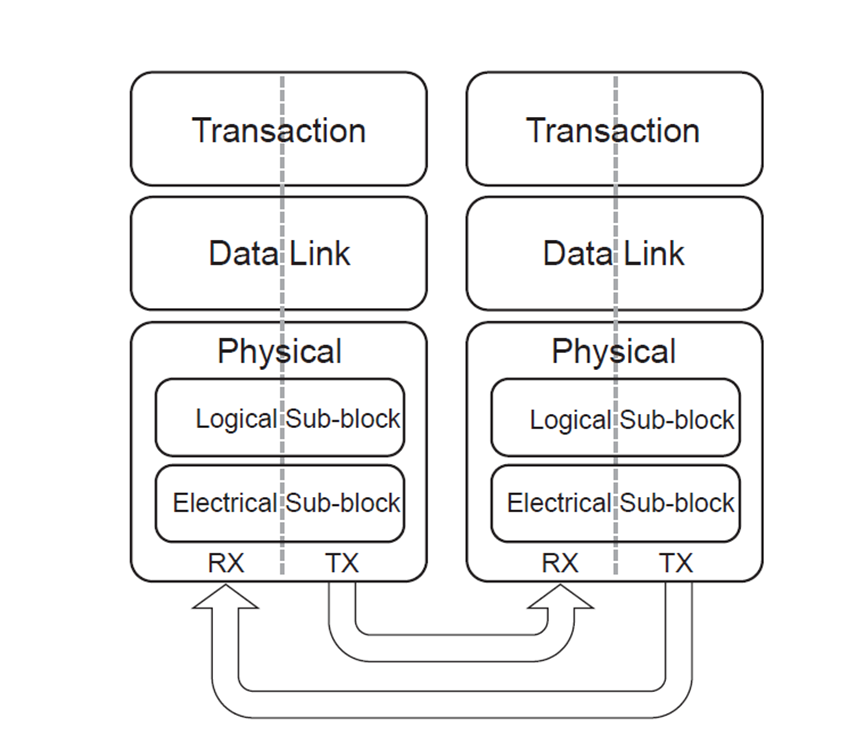

PCIE的结构是一种分层的设计,旨在确保模块化和灵活性,同时提供强大的性能。以下是PCIe结构的详细说明:

1. 物理层(PhysicalLayer)

物理层是PCIe架构的底层,负责处理实际的信号传输。物理层的详细描述包括以下几个核心部分:

(1)物理逻辑子层(PhysicalLayer Logic Sublayer, PLSL)

PLSL负责对接数据链路层的数据,并将其转换为物理层可以处理的格式。这一层处理数据包的序列化和反序列化、信号的编码与解码,以及数据的打包和解包。

(2)物理编码子层(PhysicalCoding Sublayer, PCS)

PCS负责对数据进行编码,以适应物理介质的传输特性,如在PCIe中使用8b/10b编码或更高级别的128b/130b编码来保证足够的DC平衡和时钟恢复能力。

(3)物理介质附属子层(PhysicalMedium Attachment Sublayer, PMAS)

这一层关注信号在物理媒介上的传输,包括信号的预加重、均衡、去加重等处理,以优化信号质量和克服传输距离所带来的损耗。

(4)物理介质相关子层(PhysicalMedium Dependent Sublayer, PMDS)

PMDS定义了具体的物理接口规范,如电气特征、电缆类型、连接器标准、信号品质参数等,确保不同制造商生产的组件能够相互兼容。

(5)物理层信号和时序

PCIe物理层采用差分信号传输,降低电磁干扰并提高信号完整性,通过正负信号对来表示二进制数据,从而在高速传输时仍能保持良好的信号质量。

(6)链路训练与状态机(LinkTraining and Status State Machine, LTSSM

LTSSM是一个重要的组成部分,它负责初始化和管理PCIe链路的状态,包括速率协商、位锁定、符号锁定、电气均衡设置以及链路激活和退出的过程。

(7)物理层包(PhysicalLayer Packet, PLP)

物理层还生成和处理一些特殊类型的包,如用于链路训练和管理的命令集(OrderedSets),这些不是常规的数据包,而是用于维护和优化链路性能的信号序列。

(8)电气子层

包括了发射和接收电路,负责生成和识别信号,并确保信号在物理线路上传输时符合规范的要求,包括但不限于信号幅度、边沿速度、噪声容限和信号衰减等问题。

2. 数据链路层(DataLink Layer)

数据链路层位于物理层之上,负责处理数据包的封装、解码和错误检测。主要包括以下方面:

(1)帧化与去帧化

数据链路层将事务层传递下来的TLPs(TransactionLayer Packets)帧化,以便在物理层上进行传输。同时,接收端的数据链路层将接收到的帧解码成原始的TLPs,然后传递给事务层。

(2)错误检测与校正

数据链路层通过CRC(循环冗余检查)等算法对TLPs进行错误检测。如果检测到错误,数据链路层会根据协议规定采取相应的错误处理措施,比如请求重发。

(3)流量控制

数据链路层使用Credit-based流控机制来防止发送方的数据淹没接收方。每发送一个TLP,接收方就会消耗一个Credit,而发送方只有在拥有足够Credit的情况下才能发送下一个TLP。

(4)链路状态管理

数据链路层负责监控和管理链路的状态,包括链路的训练、配置和维护等。此外,数据链路层还负责链路的恢复和重新训练过程。

(5)链路功耗管理

PCIe支持多种低功耗状态,数据链路层参与管理这些状态,以降低系统的能耗。例如,当没有数据传输时,链路可以被置于低功耗状态。

(6)链路层报文(LLPs, Link Layer Packets)

数据链路层定义了自己的报文格式,用于执行特定的控制和状态管理任务。LLPs通常包括用于链路初始化、训练、状态报告和错误处理的报文。

(7)DLLP(DataLink Layer Packet)

DLLP是一种特殊的链路层报文,用于在设备和控制器之间传送流量控制信息和其他控制消息。DLLP的开销很小,通常只包含8字节,因此对性能的影响非常有限。

3. 事务层(TransactionLayer)

事务层是PCIe结构中的第三层,它负责处理事务级的操作,如读取、写入和I/O操作。几个主要功能:

(1)TLP(TransactionLayer Packet)处理

事务层的主要职责是创建、处理和解析TLPs。TLPs是封装了PCIe事务数据的包,它们包含了必要的头部信息,如命令类型、地址、长度和其他控制信息。

(2)命令与响应处理

事务层支持各种类型的数据传输命令,包括读(Read)、写(Write)、配置读(Config Read)、配置写(Config Write)等。对于每种操作,事务层都会生成相应的TLPs,并在数据传输完成后生成相应的完成状态TLPs。

(3)虚拟通道(VC,Virtual Channel)管理

为了提高带宽利用率和响应时间,事务层提供了多通道(通常是两个)的并发数据传输能力。每个虚拟通道都有自己的Credit池和优先级,使得不同的流量可以独立地被管理和调度。

(4)地址翻译

事务层负责将软件层面的内存地址转换为PCIe地址空间,包括事务层格雷码地址。这使得TLPs能够在PCIe网络上正确路由。

(5)数据缓冲与分段

为了适应物理层的数据传输要求,事务层会对较大的数据块进行分段处理,并将其存储在缓冲区中。这样可以确保数据的连续性和完整性。

(6)流控制

事务层通过与数据链路层交互来实施流控制机制。这保证了发送方不会因为发送速度过快而导致接收方缓冲区溢出。

(7)事务排序

事务层负责保证数据按照正确的顺序进行传输,特别是在存在多个并发事务时,以确保数据的正确性和一致性。

(8)错误处理

事务层能够检测和处理一些传输错误,例如地址错误、大小错误或者无效的操作等。对于无法纠正的错误,事务层会向上游发送错误报告

4. 设备层和应用层

在事务层之上,是设备层和应用层。这些层次提供了对PCIe设备的抽象和接口,使得上层软件能够方便地与PCIe设备进行交互。设备层定义了PCIe设备的特定属性和功能,而应用层则提供了对这些功能的访问和使用。

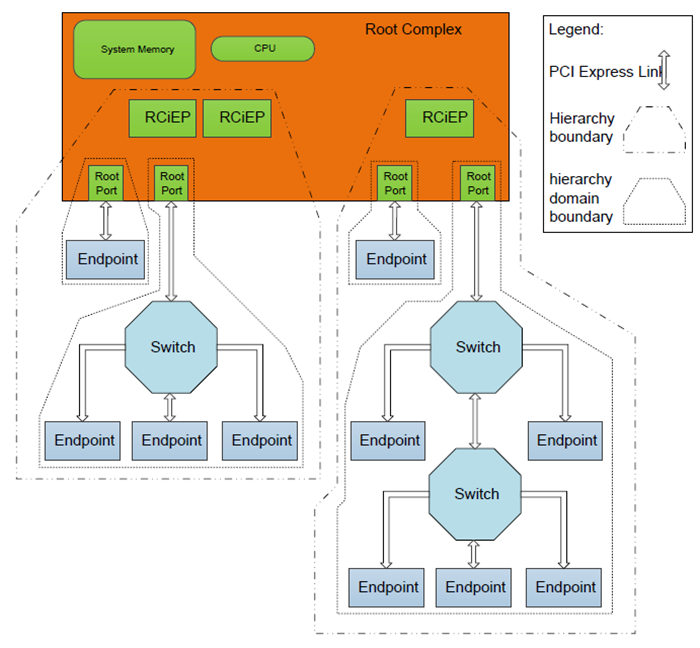

5. 端点(Endpoints)和根联合体(Root Complex)

在PCIe系统中,端点(Endpoints)是实际的数据源或数据目的地,它们可以是各种PCIe设备,如显卡、网卡等。根联合体(Root Complex)则是连接CPU和内存的子系统,它作为PCIe系统的主机,负责管理PCIe总线上的设备,并协调它们之间的数据传输。

在复杂的PCIe系统中,交换机和桥接器用于扩展总线的范围,连接更多的设备。交换机用于在多个PCIe设备之间提供数据通道,而桥接器则用于连接不同类型的总线,实现不同总线之间的通信。

总体来说,PCIe的结构设计充分考虑了模块化和灵活性,使得不同层次的组件可以独立演进和扩展。这种设计确保了PCIe能够满足不断变化的应用需求,并提供持续的性能提升。

PCIE未来发展趋势

PCIE未来的发展趋势主要集中在以下几个方面:

1、更高的传输速率:随着数据中心和高性能计算需求的增加,PCIe标准的传输速率将继续提升。例如,PCIe 5.0标准相比于PCIe 4.0,带宽翻倍,而正在开发中的PCIe 6.0和PCIe 7.0将进一步大幅提高速率。

2、更低的延迟:为了满足实时计算和网络通信的需求,PCIe的未来发展将致力于减少传输延迟,提高数据处理效率。

3、能效优化:随着绿色计算和可持续发展的重视,PCIe技术的能效比将成为重要指标。未来的发展将着重于降低能耗,特别是在空闲或低负载状态下。

4、增强的虚拟通道功能:虚拟通道技术允许PCIe设备在多个通道上同时进行数据传输,提高带宽利用率。未来的PCIe版本可能会进一步增强VC的功能,提供更多的通道以及更复杂的调度策略。

5、更好的兼容性与互操作性:随着不同代数的PCIe设备并存,确保新旧设备间的兼容性和互操作性将是PCIe发展的关键。

6、集成安全特性:为了应对日益增长的安全威胁,PCIe未来可能会集成更多的安全特性,如硬件加密和认证机制,以保护数据传输过程中的安全性。

7、扩展应用场景:PCIe不仅应用于传统的计算机和服务器领域,还将拓展至更多新兴领域,如汽车电子、物联网设备等,以满足这些领域的特定需求。

综上所述,PCIe的未来发展将围绕提升性能、降低功耗、增强安全性以及扩大应用范围等方面展开。随着技术的不断进步,PCIe将继续作为连接各种硬件组件的关键桥梁,支撑着现代计算和通讯技术的发展。

审核编辑:黄飞

电子发烧友App

电子发烧友App

评论