ARM720T是一款通用的32位微处理器,具有8KB的高速缓存、扩大的写入缓冲区和内存管理单元(MMU),组合在一个芯片中。ARM720T中的CPU是ARM7TDMI。ARM720T是与ARM处理器

2023-08-02 11:36:56

性能--ARM调试架构,额外支持实时调试。这使关键异常处理程序能够在调试系统时执行。

•支持外部紧密耦合存储器(TCM)。为每个外部指令和数据存储器块提供TCM接口。指令和数据TCM块的大小都是特定于实现者的,可以在0KB到1MB之间

2023-08-02 10:17:36

PrimeCell DC-DC转换器接口是由ARM开发、测试和许可的符合高级微控制器总线架构(AMBA)的片上系统外围设备。

PrimeCell DC-DC转换器接口是一个AMBA从模块,连接到高级

2023-08-02 11:14:26

(AXI),用于支持优先级的二级接口

多处理器实现

•九级管道

•带返回堆栈的分支预测

•低中断延迟

•外部协处理器接口和协处理器CP14和CP15

•可选的指令和数据存储器保护单元(MPU)

•可选的指令

2023-08-02 09:15:45

高速缓存体系结构处理器,适用于全内存管理、高性能和低功耗至关重要的多程序应用。此设计中的独立指令和数据缓存大小分别为16KB,具有8字线长度。ARM920T处理器实现了一个增强的ARM架构v4-MMU,为

2023-08-02 13:05:00

CPU。16KB指令与 16KB 数据缓存。指令与数据存储器管理单元(MMU)。写缓冲器。高级微处理器总线架构(AMBA)总线接口。ETM(内置追踪宏单元)接口。 ARM920T中的ARM

2019-09-26 09:43:55

ARM966E-S是一个可合成的宏单元,将ARM处理器与紧密耦合的SRAM存储器相结合。它是ARM9 Thumb系列高性能32位片上系统(SoC)处理器解决方案的一员,面向广泛的嵌入式应用,在这

2023-08-02 07:46:42

ARM9E 系列微处理器的主要特点如下。支持 DSP 指令集,适合于需要高速数字信号处理的场合。5级流水线,指令执行效率更高。 支持 32 位 ARM 指令集和 16 位 Thumb 指令集。支持

2019-09-26 09:36:52

ARM处理器中断处理的编程是怎么实现的?

2021-04-27 06:46:53

。ARM处理器模式ARM微处理器支持7种运行模式,分别为:用户模式(usr):ARM处理器正常的程序执行状态。快速中断模式(fiq):用于高速数据传输或通道处理。外部中断模式(irq):用于通用的中断

2011-01-27 11:13:20

。ARM处理器模式ARM微处理器支持7种运行模式,分别为:用户模式(usr):ARM处理器正常的程序执行状态。快速中断模式(fiq):用于高速数据传输或通道处理。外部中断模式(irq):用于通用的中断

2011-01-27 14:19:05

(32位)数据,从第四个字节到第七个字节放置第二个存储的字数据,一次排列。作为32位的微处理器,arm体系结构所支持的最大寻址空间为4GB。存储器格式1、大端格式:高字节在低地址,低字节在高地址;2、小端

2017-11-06 10:43:47

32位的微处理器,arm体系结构所支持的最大寻址空间为4GB。存储器格式1、大端格式:高字节在低地址,低字节在高地址;2、小端格式:高字节在高地址,低字节在低地址。指令长度Arm微处理器的指令长度是32位

2017-10-12 11:30:08

32位的微处理器,arm体系结构所支持的最大寻址空间为4GB。 存储器格式1、大端格式:高字节在低地址,低字节在高地址;2、小端格式:高字节在高地址,低字节在低地址。 指令长度Arm微处理器的指令长度

2017-10-25 16:55:35

。ARM复位后PC无条件的指向0x00000000处。MMU是ARM处理器的内存管理单元,CPU管理虚拟存储器、物理存储器的控制线路,同时负责虚拟地址映射为物理地址,以及提供硬件机制的内存访问授权;进行虚拟地址到物理地址的转换通过查找页表来完成,每次在访问内存时先查TLB,查不到再到内存中查整个页表。.

2021-12-21 07:16:24

ARM处理器模式和ARM处理器状态有何区别?

2022-11-01 15:15:13

处理器内核二、经典ARM处理器编程模型三、Cortex-M4处理器四、STM32F407芯片简洁一、ARM处理器特点1.ARM处理器主要特点(1)ARM7系列采用冯诺依曼结构(输入输出、控制器、存储器、处理器),ARM9~11采用哈佛体系结构(存储器分为程序存储器和数据存储器)(2)属于RISC型处理器结

2021-12-13 07:18:29

。因此在介绍ARM之前,需要对RISC体系结构、组织结构是基本情况进行全面介绍。1. RISC体系结构计算机体系结构描述:从用户角度看到的计算机属性,如计算机的指令集、可见寄存器、存储器管理单元和异常处理

2022-04-24 09:57:10

时的实现工艺。容易实现高性能。RISC体系结构的简单性、有效性很容易设计出低成本、高性能的处理器。RISC技术的历史贡献在计算机设计技术的发展变化中,20世纪60年代初引入的虚拟存储器、Cache和流水线

2022-04-24 10:02:29

。作为 32 位的微处理器,ARM920T 体系结构所支持的最大寻址空间位 4GB(232字节) 。ARM920T 体系结构支持两种方法存储字数据,即大端(Big Enddian)格式和小端

2019-09-27 09:37:35

2.ARM微处理器的指令系统ARM微处理器的指令集是加载/存储型的,即指令集仅能处理寄存器中的数据,而且处理结果都要放回寄存器中,而对系统存储器的访问则需要通过专门的加载/存储指令来完成。ARM

2021-12-20 06:54:28

慕课电子科技大学.嵌入式系统.第三章.ARM微处理器编程基础和接口实验.ARM微处理器编程基础实验0 目录3 ARM微处理器编程基础和接口实验3.1 ARM微处理器编程基础实验3.1.1课堂重点

2021-12-14 09:04:05

慕课电子科技大学.嵌入式系统.第三章.ARM微处理器编程基础和接口实验.ARM设备接口实验0 目录3 ARM微处理器编程基础和接口实验3.2 ARM设备接口实验3.2.1课堂重点3.2.2测试与作业

2021-12-14 08:46:10

[table][tr][td=670][table][tr][td]arm处理器本身所产生的地址为虚拟地址,每一个arm芯片内都有存储器,而这个芯片内的存储器的地址为物理地址。我们写程序的目的是为了

2014-03-24 11:57:18

各位大神,小菜需要一款主频在600MHZ以上的,带有PWM,和AD转换的ARM处理器,用作运动控制的。

2014-04-13 09:58:18

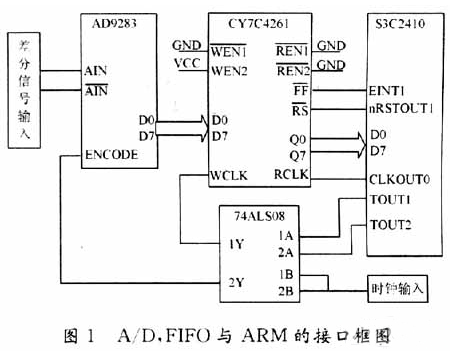

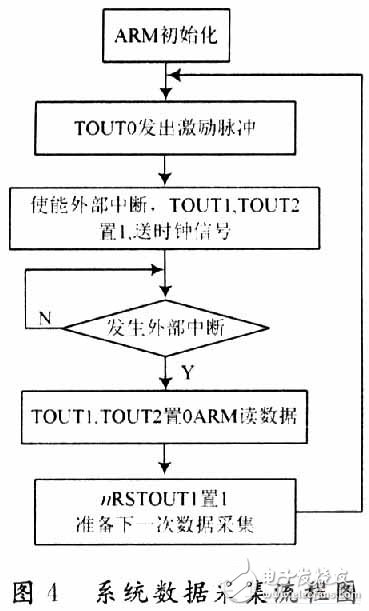

FIFO存储器是系统的缓冲环节,如果没有FIFO存储器,整个系统就不可能正常工作,它主要有几方面的功能:1)对连续的数据流进行缓存,防止在进机和存储操作时丢失数据;2)数据集中起来进行进栈和存储,可

2022-01-18 10:03:06

第一套在8086的微计算机系统中,存储器是如何组织的?是如何与处理器总线连接的?#BHE信号起什么作用?答:8086 为 16 位处理器,可访问 1M 字节的存储器空间;1M 字节的存储器分为两个

2021-07-26 06:06:49

PXA255处理器开发诸如车载导航系统时,电子地图等海量地理信息数据需要一个容量大、体积小、性能优异的存储器。“Compact Flash”卡,简称CF卡,具有高速度、大容量、体积小、重量轻、功耗低

2019-04-08 09:36:20

描述此参考设计面向目前使用 FPGA 或 ASIC 将高速数据转换器连接到基带处理器的宽带接收器系统开发人员,他们需要缩短产品上市时间,同时增强性能并大大降低成本、功率和尺寸。此参考设计包括首个广泛

2018-09-20 09:07:06

高速模/数转换器AD10242的功能特点与应用有哪些?如何实现AD10242与DSP进行接口连接?

2021-04-14 06:36:19

高速硬盘存储设备实现数据的持续高速存储,要求处理数据的速度高。通常这些需要传输和处理大量数据的设备均选用数字信号处理器DSP作为微处理器。同时,SCSI协议中许多复杂的控制功能也需要这个微处理器来实现

2011-06-02 09:33:21

本章节介绍了 Cyclone® IV 器件的存储器接口管脚的支持以及外部存储器接口的特性。除了大量供应的片上存储器,Cyclone IV 器件可以很容易地与各种外部存储器件建立连接,其中包括

2017-11-14 10:12:11

了设计的一大挑战。FPGA可通过在单个FPGA中实现多个视频处理器来提供强大的处理能力。那么现在的挑战就变成了要使数据尽快且高效地从FPGA进出。DDR3存储器系统在大多数情况下可以为这些基于FPGA的系统

2019-05-24 05:00:34

FPGA实现高速FFT处理器的设计介绍了采用Xilinx公司的Virtex - II系列FPGA设计高速FFT处理器的实现方法及技巧。充分利用Virtex - II芯片的硬件资源,减少复杂逻辑,采用

2012-08-12 11:49:01

为了满足智能手机功能日益提高的数据需求,现代数字移动通信系统的基础设施必须持续发展以支持更宽的带宽和更快的数据转换。为实现高速的数据速率,数字转换器中的数字中频处理、包括DDC(数字下变频器

2019-08-01 07:26:17

缓存,而 SL3另外还可在局域 L2 高速缓存中进行缓存。 为向软件执行提供快速通道,外部存储器同内部共享存储器一样,通过同一存储器控制器进行连接,而并非像在嵌入式处理器架构上所进行的传统做法那样

2011-08-13 15:45:42

存储器访问权限控制Cache通过MMU的访存MMU会先查找TLB中的虚拟地址表如果TLB中没有虚拟地址的入口,硬件从主存储器中的转换表中获取转换与访问权限。ARM的MMU访存原理ARM的MMU页表格

2022-06-13 16:41:04

ARM7TDMI处理器内核,为用户提供了面向移动终端应用的丰富外设、低功耗管理和低成本的外存配置,整个芯片可以运行在75 MHz。数据通信系统使用的主要功能模块如下:20 KB片上零等待静态存储器

2019-04-26 07:00:06

和存储。FPGA将一组数据处理完毕后,以中断的方式通知SEP3203,处理器以DMA方式将运算后的结果存储到片外的SDRAM中。由于数据写满FIFO的时间大于FPGA处理数据的时间,所以整个系统实现了

2018-12-05 10:13:09

了PowerPC、集成的APU控制器以及一个与之相连的协处理器。来自高速缓存或存储器中的指令可以立即出现在CPU解码器和APU控制器上,如果CPU能识别指令,则运行这些指令。否则,APU控制器或用

2015-02-02 14:18:19

计算机指令以及处理计算机软件中的数据。中央处理器主要包括运算器(算术逻辑运算单元,ALU,Arithmetic Logic Unit)和高速缓冲存储器(Cache)及实现它们之间联系的数据(Dat...

2022-02-10 08:00:15

串行外围设备接口SPI(serial peripheral interface)总线技术是Motorola公司推出的一种同步串行接口,它允许CPU与TTL移位寄存器、A/D或D/A转换器、实时时钟(RTO)、存储器以及LCD和LED显示驱动器等外围接口器件以串行方式进行通讯。

2019-07-12 06:33:07

ARM处理器本身是32位设计,但也配备16位指令集。一般来讲存储器比等价32位代码节省达35%,然而保留了32位系统的所有优势。

2019-11-11 06:48:04

户模式进入系统模式。ARM 处理器是一个综合体,ARM 公司自身并不制造微处理器。它们是由 ARM 的合作 伙伴(Intel 或 LSI)制造。ARM 还允许将其处理器通过协处理器接口进行紧耦合。它还

2019-09-24 17:47:38

高速转换器是什么

2021-03-04 07:26:53

关于高速存储器的调试和评估,看完你就懂了

2021-05-11 06:28:25

关于数Gpbs高速存储器接口设计的分析,看完你就懂了

2021-05-19 06:38:12

描述此参考设计介绍高可靠性应用(基于 66AK2Gx 多内核 DSP + ARM 处理器片上系统 (SoC))中具有纠错码 (ECC) 支持的双倍数据速率 (DDR) 存储器接口的系统注意事项。其中

2022-09-15 06:26:24

微处理器送往存储器和I/O接口电路的,如读/写信号,片选信号、中断响应信号等;也有是其它部件反馈给CPU的,比如:中断申请信号、复位信号、总线请求信号、限备就绪信号等。控制总线的具体情况取决于CPU。三

2022-08-17 15:20:52

的,因此,还应将微处理器的一些必要引脚用接口插座引出,方便实验开发使用。下面将以模块为单元介绍典型的需要引出的引脚,并给出相应电路的选型。3.2.1 FLASH存储器模块所需引脚为ADDR[21:0

2011-11-25 10:03:34

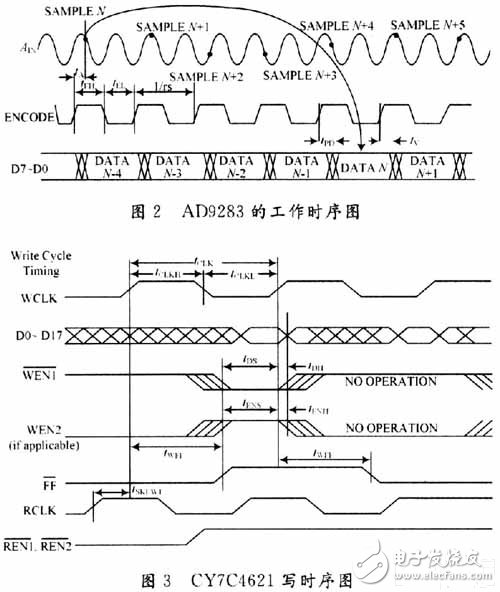

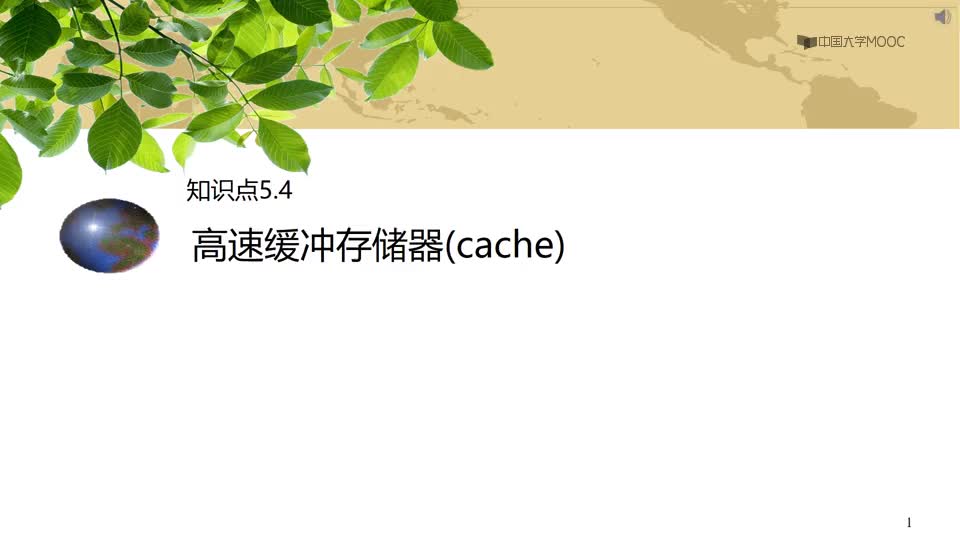

在高频超声波数据采集系统中,很多高速A/D转换器往往不能直接与处理器相连接,这时就需要使用FIFO在处理器与A/D转换器之间架一座桥梁,FIFO的先入先出特性可以方便缓存大量的数据块。在基于ARM

2020-12-28 06:55:06

了设计的一大挑战。FPGA可通过在单个FPGA中实现多个视频处理器来提供强大的处理能力。那么现在的挑战就变成了要使数据尽快且高效地从FPGA进出。DDR3存储器系统在大多数情况下可以为这些基于FPGA的系统

2019-05-27 05:00:02

。在结构上的改进主要包括可变宽度的存储器接口、更快速的指令周期时间、可设置优先级的双通道DMA处理器、灵活的引导程序装入方式、可重新定位的中断向量表以及可选的边缘/电平触发中断方式等。 1

2019-06-14 05:00:08

FIFO、紧耦合存储器及16位的SRAM集成在SOPC系统中,并在FPGA开发板上实现的方法,其内容包括外设的接入方法,以及紧耦合存储器如何通过紧耦合从端口直接与处理器的紧耦合数据/指令主端口相连等

2018-12-07 10:27:46

基于Proteus的Arm处理器的SPI接口实现

2010-02-10 10:41:58

处理器供电的理想选择。对相位的增加或遮蔽能力可在宽范围的负载条件下实现高效率。LP8758 就是业内最先进多相位转换器的最好示例,它是手机处理器电源的理想选择。它具有低IQ,小总体解决方案尺寸,16A

2018-09-06 15:55:29

一、什么是CacheCache是一种容量比较小,但访问速度比较快存储器。由于处理器的速度远高于主存,处理器直接从内存中存取数据要等待一定周期,而Cache位于处理器与主存之间,保存着最近一段时间

2016-08-31 16:30:26

如何实现扩展存储器的设计?

2021-10-28 08:08:51

本文介绍了使用XCR3032实现K9K1G08U0M与微控制器的接口原理,给出了VerilogHD L实现程序。对大容量FLASH存储器的接口设计具有一定的参考价值。

2021-04-29 06:34:20

如何利用Xilinx FPGA和存储器接口生成器简化存储器接口?

2021-05-06 07:23:59

DDR3存储器控制器面临的挑战有哪些?如何用一个特定的FPGA系列LatticeECP3实现DDR3存储器控制器。

2021-04-30 07:26:55

什么是I2C总线?一种基于I2C总线的AT24存储器数据串并转换接口的VHDL设计

2021-05-27 06:55:42

的工作时钟频率。然而,设计至DDR3的接口也变得更具挑战性。在FPGA中实现高速、高效率的DDR3控制器是一项艰巨的任务。直到最近,只有少数高端(昂贵)的FPGA有支持与高速的DDR3存储器可靠接口的块

2019-08-09 07:42:01

如何用低成本FPGA解决高速存储器接口挑战?

2021-04-29 06:59:22

我喜欢使用verilog,vivado2017.1设计处理器(MIPS32),设备是Virtex7 vc707。我已经使用BRAM作为主存储器(.coe文件的init指令)在FPGA(Virtex7

2020-08-25 13:19:36

本文采用SoPC内嵌32位的软核处理器Nios,实现了一个UART串行口和以太网接口的转换器(以下简称转换器),并基于Microtronix公司针对Nios处理器移植的μClinux开发了应用程序。

2021-04-25 06:17:46

困难,因此高性能的ARM协处理器接口仅限于片上使用。最常使用的协处理器是用于控制片上功能的系统协处理器,例如控制ARM720上的高速缓存Cache和存储器管理单元MMU等。ARM也开发了浮点协处理器

2022-04-24 09:36:47

本文讲述了一种基于ARM7处理器实现USB接口与CAN总线的实例,通过其可以在PC实现对CAN总线上设备的监控。

2021-05-21 06:58:17

如何满足各种读取数据捕捉需求以实现高速接口?怎么缩短高端存储器接口设计?

2021-04-29 07:00:08

描述此参考设计介绍高可靠性应用(基于 66AK2Gx 多内核 DSP + ARM 处理器片上系统 (SoC))中具有纠错码 (ECC) 支持的双倍数据速率 (DDR) 存储器接口的系统注意事项。其中

2018-10-22 10:20:57

模数转换器(Analog To Digital Converter)简称ADC(也可以写成A/D),是指将连续变化的模拟信号转换为离散的数字信号的器件。 直接存储器存取技术(Direct

2022-02-07 08:29:11

协议用于维护由于多个处理器共享数据引发的多处理器数据一致性问题。论述了一个适用于64位多核处理器的共享缓存设计,包括如何实现多处理器缓存一致性及其全定制后端实现。本文介绍了一种共享高速存储器模块

2021-02-23 07:12:38

本文设计了一种在多处理器系统中的Nios II软核处理器的启动方案,这个方案在外部处理器向Nios II的程序存储器和数据存储器加载数据时,可以控制Nios II处理器的启动。

2021-04-27 06:52:42

数据存储器 FLASH程序存储器 FLASH数据存储器 片内RAM数据存储器16M字节外部数据存储器各有什么区别?特点?小弟看到这段 很晕。ADuC812的用户数据存储器包含三部分,片内640字节的FLASH数据存储器、256字节的RAM以及片外可扩展到16M字节的数据存储器。求助高手。解释一下不同。

2011-11-29 09:50:46

STM32F103处理器内部存储器结构及映射 STM32F103存储器映像为预定义形式,严格规定了哪个位置使用哪条总线。 STM32F103的程序存储器、数据存储器、寄存器和IO端口被组织到

2021-12-09 07:51:09

用于高速数据转换器的串行接口有哪些选择?

2021-04-09 06:55:28

解码器需要一个恒速的传输流)。虽然存储器对同步的要求似乎很小,但当涉及到多个码流时它可能很显著。这种同步可以由一个异步FIFO实现。 2) 帧存储: 帧存储在这些地方需要:任何暂时的处理如帧率转换

2011-07-15 09:18:00

如何满足各种读取数据捕捉需求以实现高速接口?如何让接收到的时钟与数据中心对准?为了缩短设计周期应遵循哪些规则?如何设计存储器接口才能获得更高性能?

2021-04-14 06:30:23

40kB 的片内SRAM、512kB 嵌入的高速Flash 存储器,128 位宽度的存储器接口和独特的加速结构使32 位代码能够在最大时钟速率下运行, 为通信网关、协议转换器、软件modem、语音识别

2019-06-04 05:00:15

In First Out)存储器凭借其操作简单、可靠性好等特点,被广泛的应用于数据采集系统中,成为了连接MCU与AD芯片的桥梁。为了使MCU、AD芯片以及高速FIFO存储器能够协调工作,就需要设计好这

2019-05-23 05:01:08

。在结构上的改进主要包括可变宽度的存储器接口、更快速的指令周期时间、可设置优先级的双通道DMA处理器、灵活的引导程序装入方式、可重新定位的中断向量表以及可选的边缘/电平触发中断方式等。 1

2019-06-12 05:00:08

如何使用Arm-2D在小资源Cortex-M处理器芯片中实现图形界面,非arm cortex处理器能用Arm-2D吗?

2022-08-04 14:14:51

设计AD7574 A D转换器与微处理器的接口(该接口用作存储器映像输入设备) :

2009-06-12 14:21:32 52

52 FPGA设计的高速FIFO电路技术

本文主要介绍高速FIFO电路在数据采集系统中的应用,相关电路主要有高速A/D转换器、FPGA、SDRAM存储器等。图1为本方案的结构框图。在大容量

2010-05-27 09:58:59 2226

2226

摘要:基于TI公司的高速数字信号处理器芯片,详细描述美国SST公司推出的28SF040闪存芯片的性能特点、引脚功能,同时给出用其扩展DSP芯片的数据存储器空间的硬件设计电路及相应的软件编程方法。 关键词:闪烁存储器,接口,DSP

2011-02-27 20:42:54 23

23 大多数的高速模数转换器不能够直接和DSP 相连。一个比较好的解决办法是使用FIFO 作为输入缓冲。FIFO 可以通过C6000 系列的外部存储器接口( EMIF) 与TMS320C6000 系列

2017-05-31 16:09:36 3

3 EE-162:通过外部存储器总线将ADSP-BF535 Blackfin处理器连接到高速转换器(如AD9860/2上的转换器)

2021-05-20 20:48:46 2

2

电子发烧友App

电子发烧友App

评论