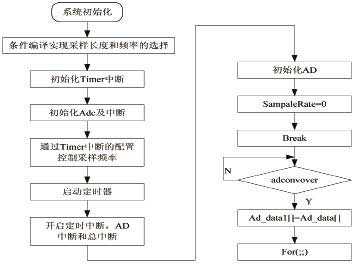

3 软件设计

首先编写CPLD程序对ADG726及ADS7805进行地址译码,然后对CPLD在线编程生成译码电路。

/*--adc mux--*/

assign mux_wr=~((addr==4'h3)&(~is)&(~dsp_wr));//ADG726映射到I/O空间的地址0x3000~0x3FFF,得到写使能信号

assign mux_en=0;//ADG726的使能引脚始终有效

/*--adc--*/

assign buffer_cs=(~(addr==4'h0))|is;//ADC映射到I/O空间的地址0x0000~0x0FFF,得到缓冲器的片选信号

assign adc_cs=~((addr==4'h0)&(~is)&dsp_rdwr);//得到ADC的片选信号

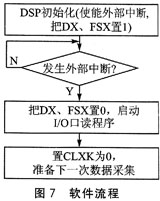

在DSP程序中,对0x3000~0x3FFF的任意地址执行一个读操作,由DSP选择的通道就被选通,信号由ADG726输出到运放AD620,差分转单端后输出到ADC。通过写数字I/O的控制寄存器,先将R//C拉低,再对I/O空间的0x0000~0x0FFF执行一个读操作,然后将R//C拉高,就启动了ADC。读0x0000~0x0FFF 其中任一个地址产生低电平的CS信号,该信号保持的时间由访问I/O空间的等待时间决定,通过设置等待状态寄存器来保证获得有效的延时时间。

/*--设置等待状态寄存器--*/

WSGR = 0x01C0;//bit8-6=111,访问I/O空间时插入7个等待状态

ADC转换完成置BUSY为高电平,向DSP申请中断,相应中断被使能之后DSP开始处理中断服务程序,完成数据的读取与其他处理。

/*--初始化ADC字程序--*/

*MCRA &= 0xFC3F;//配置4个I/O引脚bit9-6为通用功能用于ADG726通道选择

*MCRB &= 0xFF7F;//bit7对应的I/O引脚控制R//C

*PADATDIR |= 0xC000;//bit7-6配置为输出,对应通道选择的两个引脚

*PBDATDIR |= 0x0300;//bit1-0配置为输出,对应通道选择的另两个引脚

*PCDATDIR |= 0xC000;//bit6配置为输出,对应R//C

*XINT1CR |= 0x7;//上升沿有效,低优先级,使能外部中断

*IMR |= 0x20;//使能内核对应的中断

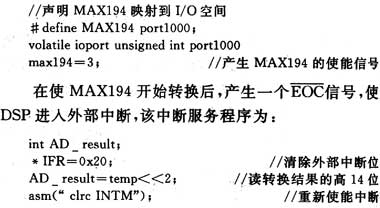

/*--声明ADG726,ADC映射到的存储单元--*/

#define AD_Output port0000

volatile ioport unsigned int port0000;

#define mux_ad port3000

volatile ioport unsigned int port3000;

/*--ADG726通道选择函数--*/

*PADATDIR &= 0xFF3F;//bit7,bit6清0

*PBDATDIR &= 0xFFFC;//bit1,bit0 清0

*PADATDIR |= ( nChlNum & 0x3 ) << 6;//设置bit7,bit6

*PBDATDIR |= ( nChlNum & 0xC ) >> 2;//设置bit1,bit0

mux_ad = 0;//产生写使能信号

/*--主程序--*/

int temp;

……

AD_Init();//初始化

ADC_MUX(13);//选择通道13

/*--启动ADC--*/

*PCDATDIR &= 0xFF7F;//使AD_R/C*变低

temp=AD_Output;//产生有效的AD_CS*

*PCDATDIR |= 0x80;// 使AD_R/C*变高

for(;;);//等待ADC中断

......

/*--中断服务程序--*/

int AD_result;

*IFR = 0x20; //清除中断标志位,以响应后续中断

AD_result = AD_Output;//读转换结果

asm(“ clrc INTM”);//重新使能中断,因为一进服务程序中断就被禁止了

4 结束语

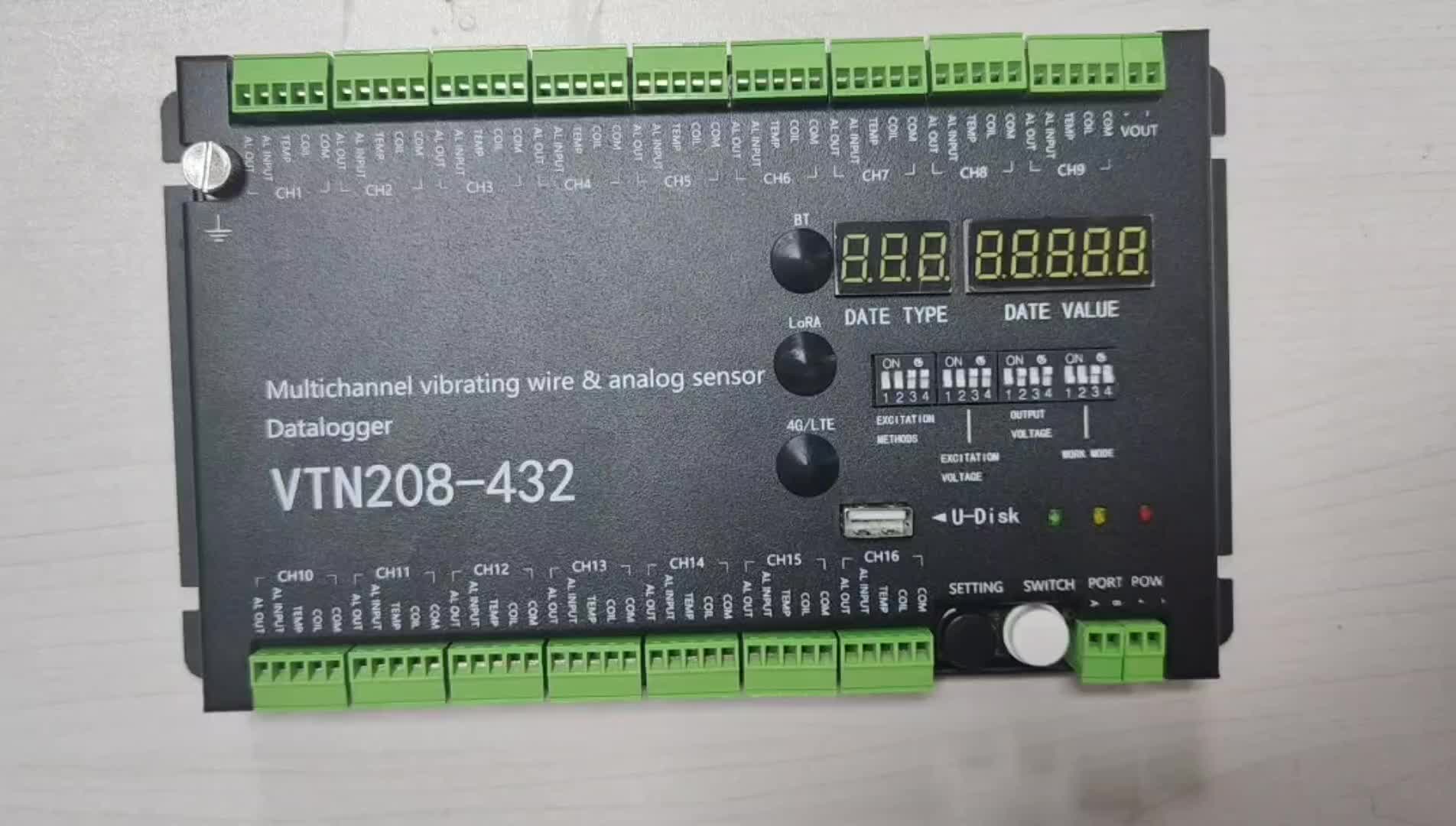

本文设计了基于TMS320LF2407A与EPM3032A的ADS7805多通道采集系统,介绍了系统的工作原理,详细描述了ADS7805、DSP及CPLD之间接口的硬件与软件设计,该方案已在笔者参与研制的嵌入式实时控制系统中得到了成功应用。

电子发烧友App

电子发烧友App

评论