MSP430 单片机时钟模块提供 3个时钟信号输出,以供给片内各部电路使用。

1-ACLK: 辅助时钟信号。由图所示,ACLK 是从 FLXT1CLK 信号由 1/2/4/8 分频器分频后所得到的。由BCSCTL1 寄存器设置DIVA相应为来决定分频因子.ACLK可用于提供CPU外围功能模块作时钟信号使用。

2-MCLK: 主时钟信号。由图所示,MCLK 是由 3 个时钟源所提供的。他们分别是LFXT1CLK,XT2CLK(F13、F14,如果是 F11,F11X1 则由 LFXT1CLK 代替),DCO 时钟源信号提供.MCLK主要用于MCU和相关系统模块作时钟使用。同样可设置相关寄存器来决定分频因子及相关的设置。

3-SMCLK: 子系统时钟,SMCLK 是由 2 个时钟源信号所提供。他们分别是XT2CLK(F13、F14)和DCO,如果是F11、F11X1则由LFXT1CLK代替TX2CLK。同样可设置相关寄存器来决定分频因子及相关的设置。

BCSCTL1 基本时钟系统控制寄存器1

7 6 5 4 3 2 1 0

XT2OFF TXS DIVA.1 DIVA.0 XT5V Rsel.2 Resl.1 Resl.0

XT2OFF 控制XT2振荡器的开启与关闭。

TX2OFF=0,XT2振荡器开启。

TX2OFF=1,TX2振荡器关闭(默认为TX2关闭)

XTS 控制LFXT1 工作模式,选择需结合实际晶体振荡器连接情况。

XTS=0,LFXT1 工作在低频模式(默认)。

XTS=1,LFXT1 工作在高频模式(必须连接有高频相应的高频时钟源)。

DIVA.0 DIVA.1 控制ACLK分频。

0 不分频(默认)

1 2分频

2 4分频

3 8分频

XT5V 此位设置为0。

Resl1.0,Resl1.1,Resl1.2 三位控制某个内部电阻以决定标称频率。

Resl=0,选择最低的标称频率。

……。。

Resl=7,选择最高的标称频率。

BSCCTL2 |= DIVM_x (x=0,1,2,3)MCLK分频(x=0,不分频;x=1,2分频;x=2,4分频;x=3,8分频)

DIVS_0

BCSCTL2 基本时钟系统控制寄存器2

7 6 5 4 3 2 1 0

SELM.1 SELM.0 DIVM.1 DIVM.0 SELS DIVS.1 DIVS.0 DCOR

SELM.1 SELM.0 选择MCLK时钟源

0 时钟源为DCOCLK(默认)

1 时钟源为DCOCLK

2 时钟源为LFXT1CLK(对于MSP430F11/12X),时钟源为XT2CLK(对于MSP430F13/14/15/16X);

3 时钟源为LFTXTICLK。

DIVM.1 DIVM.0 选择MCLK分频

0 1分频(默认)

1 2分频

2 4 分频

3 8 分频

SELS 选择SMCLK时钟源

0 时钟源为DCOCLK(默认)

1 时钟源为LFXT1CLK(对于MSP430F11/12X),时钟源为XT2CLK(对于MSP430F13/14/15/16X)。

DIVS.1 DIVS.0 选择SMCLK分频。

0 1分频

1 2分频

2 4分频

4 8分频

DCOR 选择DCO电阻

0 内部电阻

1 外部电阻

PUC信号之后,DCOCLK被自动选择MCLK时钟信号,根据需要,MCLK的时钟源可以另外设置为LFXT1或者XT2。设置顺序如下:

[1] 复位OscOff

[2] 清除OFIFG

[3] 延时等待至少50us

[4] 再次检查OFIFG,如果仍然置位,则重复[3]、[4]步骤,直到OFIFG=0为止。

低功耗设置的技巧问题:

1、LPM4:在振荡器关闭模式期间,处理机的所有部件工作停止,此时电流消耗最小。此时只有在系统上电电路检测到低点电平或任一请求异步响应中断的外部中断事件时才会从新工作。因此在设计上应含有可能需要用到的外部中断才采用这种模式。否则发生不可预料的结果。

2、LPM3:在DC发生器关闭期间,只有晶振是活动的。但此时设置的基本时序条件的DC发生器的DC电流被关闭。由于此电路的高阻设计,使功耗被抑制。注:当从DC关闭到启动DC0要花一端时间(ns-us)

3、LPM2:在此期间,晶镇振和DC发生器是工作的,所以可实现快速启动。

4、LPM1:在此振荡器已经工作,所以不存在启动时间延时问题。

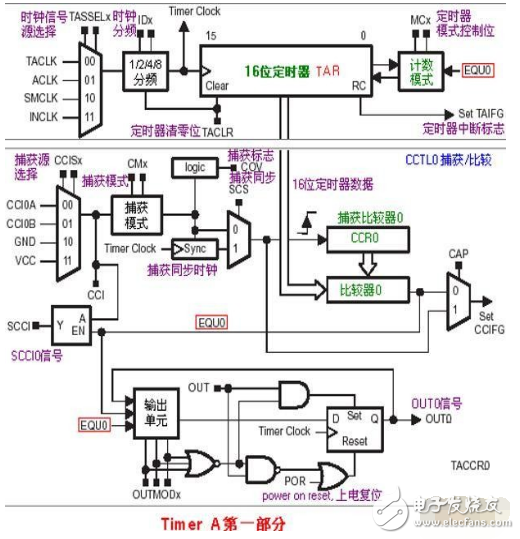

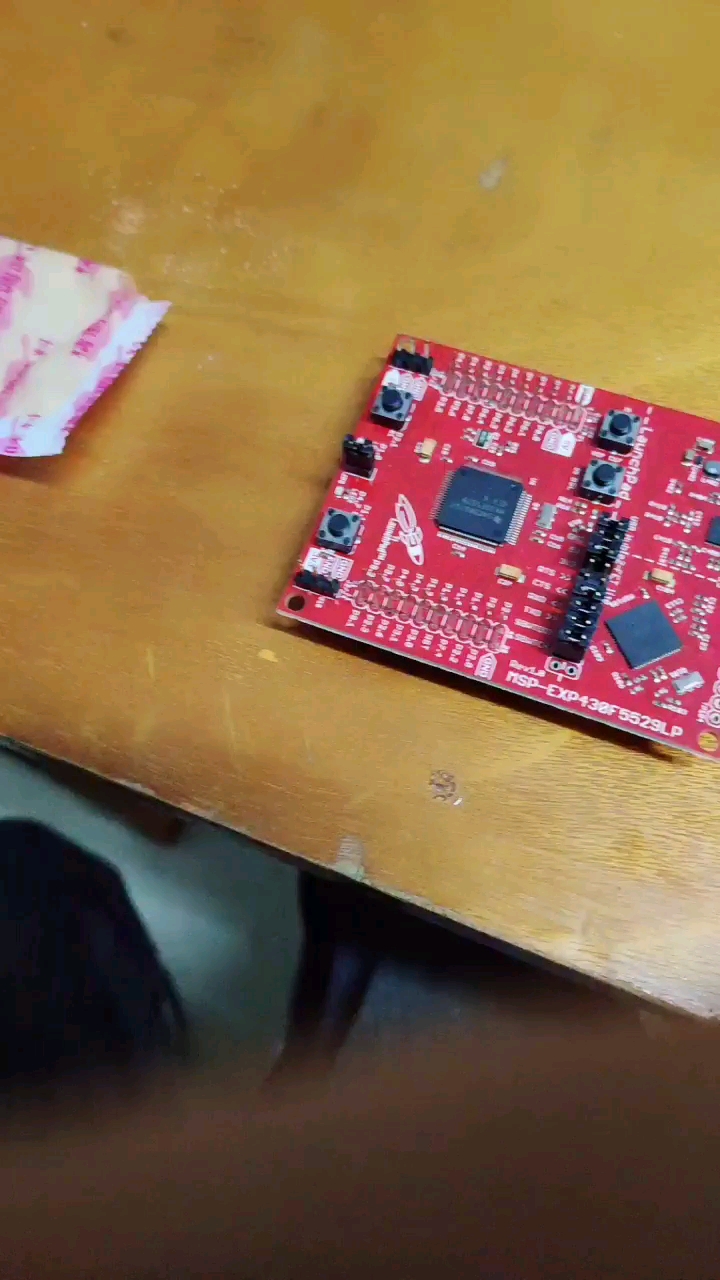

Timer_A的寄存器

寄存器 缩写 读定类型 地址 初态

Timer_A控制寄存器 TACTL R/W 160H POR复位

Timer_A计数器 TAR R/W 170H POR复位

捕捞/比较控制寄存器0 CCTL0 R/W 162H POR复位

捕捞/比较寄存器0 CCR0 R/W 172H POR复位

捕捞/比较控制寄存器1 CCTL1 R/W 164H POR复位

捕捞/比较寄存器1 CCR1 R/W 174H POR复位

捕捞/比较控制寄存器2 CCTL2 R/W 166H POR复位

捕捞/比较寄存器2 CCR2 R/W 176H POR复位

中断向量寄存器 TAIV R/W 12EH POR复位

时钟发生器的原理说明:

问题的提出:

1、高频、以便能对系统硬件请求和事件作出快速响应

2、低频率,以便将电流消耗降制至最少

3、稳定的频率,以满足定时器的应用。

4、低 Q值振荡器,以保证开始或停止操作没有延时

MSP430 采用了一个折衷的办法:就是用一个低频晶镇振,将其倍频在高频的工作频率上。一般采用这种技术的实用方法有两种,一个是说、锁相环、 一个是锁频环,而锁相环采用模拟的控制容易引起“失锁”和易引起电容量的改变。而TI 采用的是锁频环技术,它采用数字控制器DCO和频率积分来产 生高频的运行时钟频率。

TIMER_A有多个捕获比较模块,每个模块都有自己的控制寄存器CCTLx

CAPTMOD1-0 选择捕获模式

00 禁止捕获模式

01 上升沿捕获

10 下降沿捕获

11 上升沿与下降沿都捕获

CCISI1-0 在捕获模式中用来定提供捕获事件的输入端

00 选择CCIxA

01 选择CCIxB

10 选择GND

11 选择VCC

SCS 选择捕获信号与定时器时钟同步、异步关系

0 异步捕获

1 同步捕获

异步捕获模式允许在请求时立即将CCIFG置位和捕获定时器值,适用于捕获信号的周期远大于定时器时钟周期的情况。但是,如果定时器时钟和捕获信号发生时间竞争,则捕获寄存器的值可能出错。

在实际中经常使用同步捕获模式,而且捕获总是有效的。

SSCIx 比较相等信号EQUx将选择中的捕获、比较输入信号CCIx(CCIxA,CCIxB,Vcc和GND)进行锁存,然后可由SCCIx读出。

CAP 选择捕获模式还是比较模式。

0 比较模式

1 捕获模式

注意:同时捕获和捕获模式选择

如果通过捕获比较寄存器CCTLx中的CAP使工作模式从比较模式变为捕获模式,那么不应同时进行捕获;否则,在捕获比较寄存器中的值是不可预料的,推荐的指令顺序为:[1]修改控制寄存器,由比较模式换到捕获模式。

[2]捕获

OUTMODx 选择输出模式

000 输出

001 置位

010 PWM翻转/复位

011 PWM置位/复位

100 翻转/置位

101 复位

110 PWM翻转/置位

111 PWM复位/置位

CCIx 捕获比较模的输入信号

捕获模式:由CCIS0和CCIS1选择的输入信号通过该位读出。

比较模式:CCIx复位。

OUT 输出信号

0 输出低电平

1 输出高电平

如果OUTMODx选择输出模式0(输出),则该位对应于输入状态。

COV 捕获溢出标志

0 输出低电平

1 输出高电平

[1]当CAP=0时,选择比较模式。捕获信号发生复位,没有使COV置位的捕获事件。

[2]当CAP=1时,选择捕获模式,如果捕获寄存器的值被读出再次发生捕获事件,则COV置位。程序可检测COV来断定原值读出前是否又发生捕获事件。读捕获寄存器时不会使溢出标志复位,须用软件复位。

CCIFGx 捕获比较中断标志

捕获模式:寄存器CCRx捕获了定时器TAR值时置位。

比较模式:定时器TAR值等于寄存器CCRx值时置位。

#include

void main(void)

{

WDTCTL = WDTPW + WDTHOLD; //停止看门狗定时器

P1DIR |= 0x01; // 设P1.0为输出

TACTL = TASSEL_1 + MC_2 + TAIE; // ACLK, 定时器A计数模式,且开中断功能

_BIS_SR(LPM3_bits + GIE); //进入LPM3 低功耗模式和开总中断允许

}

// Timer_A3中断向量(TAIV)处理程序

#pragma vector=TIMERA1_VECTOR

__interrupt void Timer_A(void)

{

switch( TAIV ) //应用switch语句来处理多中断源的向量

{ //向量列表通过case语句来分多中断源的入口

case 2: break; // CCR1比较/捕获寄存器的中断入口,

//本例子未用到。

case 4: break; // CCR2比较/捕获寄存器的中断入口,

电子发烧友App

电子发烧友App

评论