赛灵思可编程器件含有数百万个逻辑单元 (LC),集成了当前越来越多的复杂电子系统。《UltraFAST 高层次生产力设计方法指南》为广大开发者提供了在短设计周期内开发此类复杂系统的一套最佳做法。

这种方法以下列概念为重点:

对宝贵的差异化逻辑使用并行开发流程,实现您的产品在市场上的差异化,且 shell 可用于将 IP 与生态系统的其它部分集成。

广泛使用基于 C 语言的 IP 开发流程开发差异化逻辑,让仿真速度相对于 RTL 仿真成倍增长,并且能提供时序准确和得到优化的 RTL。

使用现有的预验证、块和组件级 IP 来快速构建 shell,将差异逻辑封装在系统中。

使用脚本,针对从准确设计验证直至编程 FPGA 的流程实现高度自动化。

本指南中的建议是来自多位专家级用户多年的经验总结。与传统的 RTL 设计方法相比,该指南提供了下列改进:

设计开发时间加快 4 倍;

衍生设计开发时间加快 10 倍;

结果质量 (QoR) 提高 0.7 倍到 1.2 倍。

虽然本指南以大型复杂设计为重点,但所讨论的实践也适用于且已被成功地应用到各种类型的设计中,包括:

数字信号处理:图像处理 |视频 |雷达 |汽车

处理器加速

无线

存储

我是分割线

目 录

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

控制系统

+关注

关注

41文章

6986浏览量

114372 -

赛灵思

+关注

关注

33文章

1798浏览量

133643 -

可编程

+关注

关注

2文章

1332浏览量

41540

发布评论请先 登录

相关推荐

热点推荐

Vivado 高层次综合

感谢你对Vivado HLS也就是XILINX’s 高层次综合解决方案有兴趣,这个解决方案综合c,c++和系统c代码成Verilog和VHDL RTL结构。

发表于 04-25 08:59

•3191次阅读

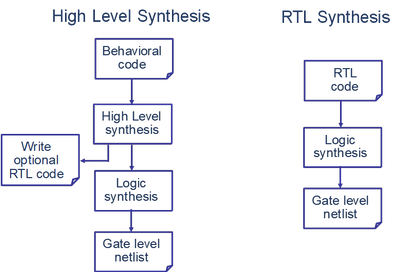

高层次综合工作的基本流程

下图揭示了高层次综合工作的基本流程,以及它于传统的RTL综合流程的对比。接下来将对行为描述,行为综合,分析与优化三个主要子流程详细描述。 1、行为描述 当我们把HLS技术的起点立为一种

发表于 01-06 17:52

SOC设计中高层次功耗估算和优化技术

在高层次对系统进行功耗佑算和功耗优化是soc设计的关健技术本文首先给出soc设计的特点和流程,然后综述目前高层次功耗估算和功耗优化的常用方法和技术,重点论述寄存器传输级和

发表于 12-27 16:42

•46次下载

使用Vivado高层次综合 (HLS)进行FPGA设计的简介

Introduction to FPGA Design with Vivado High-Level Synthesis,使用 Vivado 高层次综合 (HLS) 进行 FPGA 设计的简介

发表于 01-06 11:32

•65次下载

Vivado Design Suite HLx 版本 2016.4 现已发布

最新 UltraFast™ 设计方法指南 和 UltraFast 高层次生产力设计方法

发表于 11-10 14:49

•1266次阅读

了解最新的UltraFast设计方法窍门与技巧

更新版 UltraFast™ 设计方法指南 提供的最新内容可加速提升您的生产力,包括:源文件管理与版本控制建议、 I/O 计划设计流程与电路板/器件规划,以及时序收敛及实现

发表于 02-08 20:43

•324次阅读

Xilinx发布唯一SoC增强型Vivado设计套件,可大大提高生产力

All Programmable SoC 的生产力带来重大突破。伴随此款最新版Vivado 设计套件推出的还包括其内含的 Vivado 高层次综合(HLS)和IP集成器的增强功能,以及最新性能监控

发表于 09-06 16:07

•2078次阅读

揭示高层次综合技术工作的基本概念

是:由更高抽象度的行为描述生产电路的技术。高层次的概念代表的是硬件描述语言里面较高的抽象层次,只是随着软件硬件语言的共同发展,这样的高抽象度的行为描述语言来到了C/C++/System C 这样的

高层次综合技术原理浅析

说起高层次综合技术(High-level synthesis)的概念,现在有很多初学者简单地把它理解为可以自动把c/c++之类地高级语言直接转换成底层硬件描述语言(RTL)的技术。其实更准确的表述是:由更高抽象度的行为描述生产电路的技术。

发表于 01-28 09:11

•3次下载

【开源硬件】从PyTorch到RTL - 基于MLIR的高层次综合技术

01 演讲题目 ✦ 开源硬件系列02期: 从PyTorch到RTL - 基于MLIR的高层次综合技术 02 演讲时间 ✦ 2022年11月27日 上午 10:00 03 内容简介 ✦ 为了解

使用Vivado高层次综合(HLS)进行FPGA设计的简介

电子发烧友网站提供《使用Vivado高层次综合(HLS)进行FPGA设计的简介.pdf》资料免费下载

发表于 11-16 09:33

•0次下载

《UltraFAST 高层次生产力设计方法指南》简介

《UltraFAST 高层次生产力设计方法指南》简介

评论