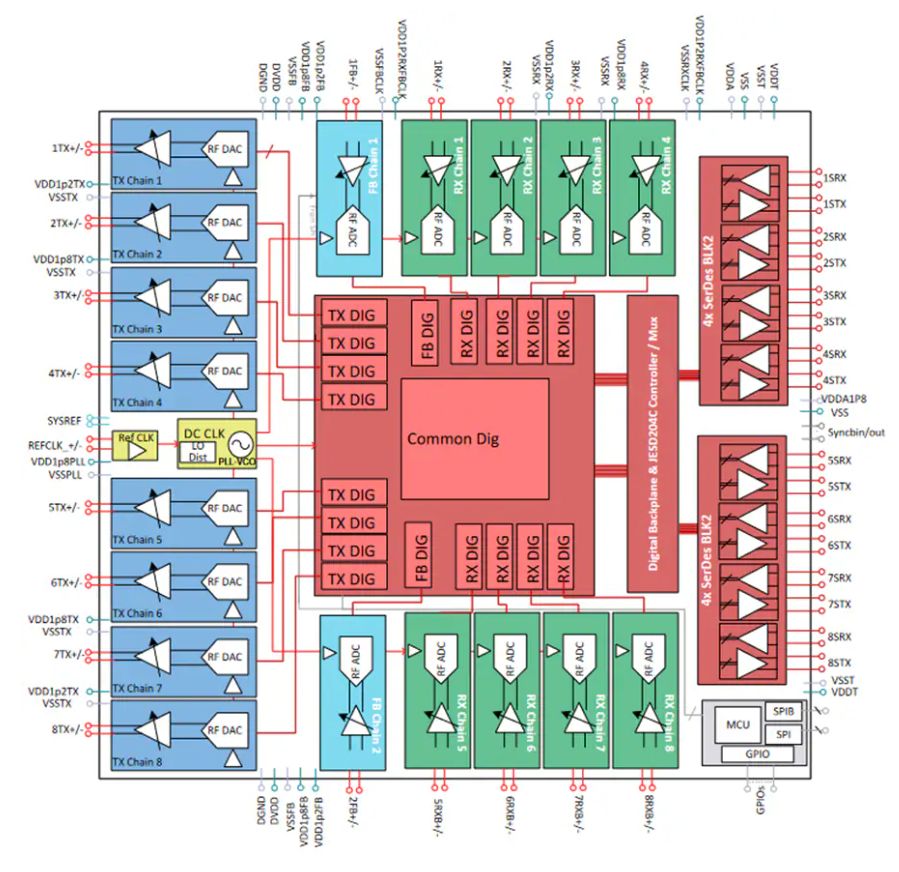

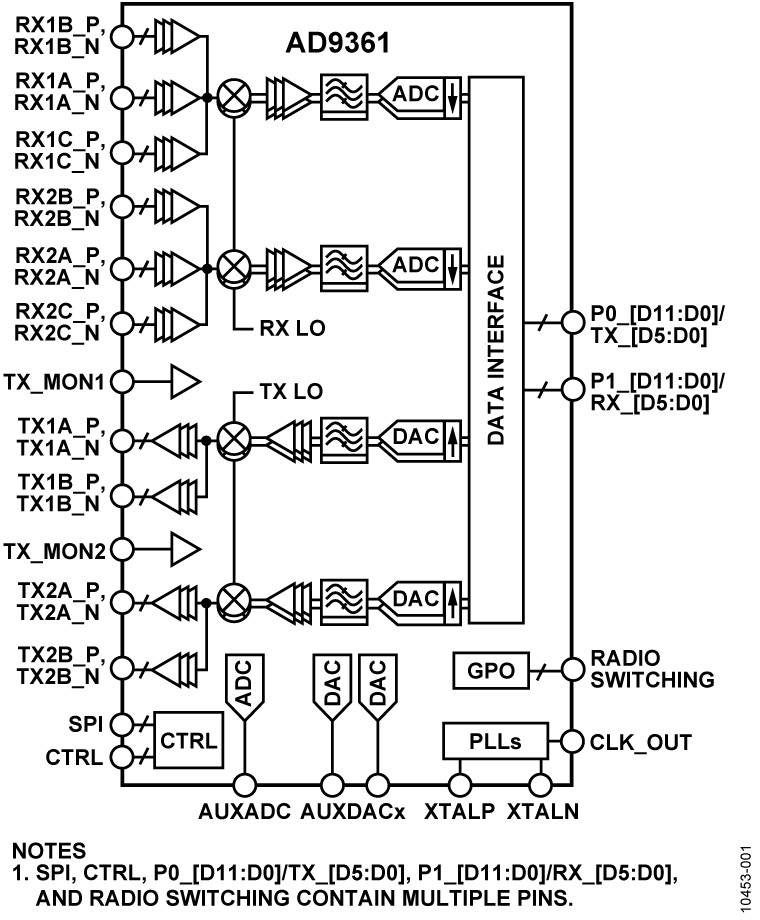

AD9361是一款面向3G和4G基站应用的高性能、高集成度的射频(RF)Agile Transceiver™捷变收发器。该器件的可编程性和宽带能力使其成为多种收发器应用的理想选择。该器件集RF前端与灵活的混合信号基带部分为一体,集成频率合成器,为处理器提供可配置数字接口,从而简化设计导入。AD9361接收器LO工作频率范围为70 MHz至6.0 GHz,发射器LO工作频率范围为47 MHz至6.0 GHz,涵盖大部分特许执照和免执照频段,支持的通道带宽范围为200 kHz以下至56 MHz。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

收发器

+关注

关注

10文章

3794浏览量

110556 -

接收器

+关注

关注

15文章

2637浏览量

76298 -

RF

+关注

关注

66文章

3196浏览量

171030

发布评论请先 登录

相关推荐

热点推荐

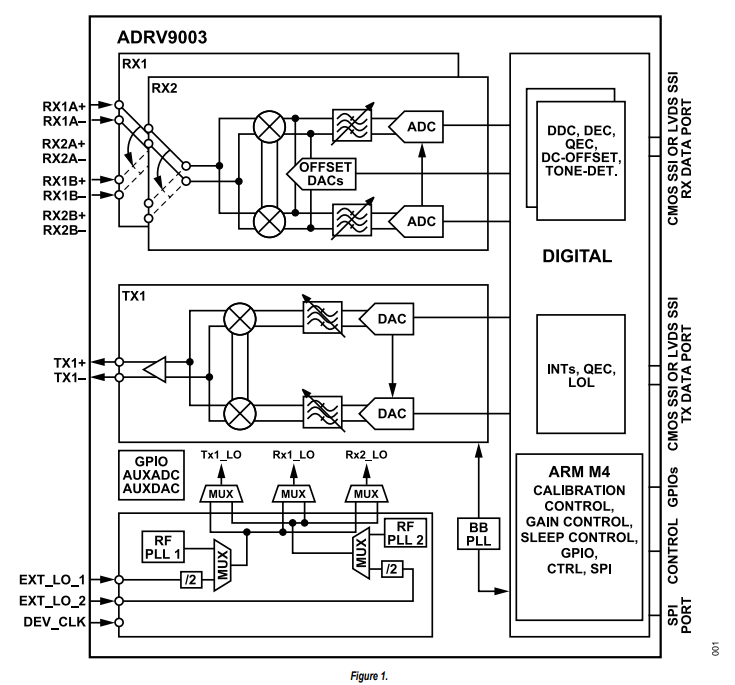

国内唯一,对标ADI!这家芯片公司发布零中频射频捷变收发器

10月14日晚间,成都华微披露了发布两收两发射频捷变收发芯片的公告。公告称,公司研发的HWD9361型射频收发芯片是一款两收两发、最大带宽5

发表于 10-15 13:49

•906次阅读

软件无线电-AD9361 璞致 PZSDR 软件无线电系列板卡之PZ-FL9361(FMCOMMS3)使用说明

ADI-AD936X系列包含AD9361、AD9364和AD9363三款高性能射频收发器,支持70MHz-6GHz频段和200kHz-56MHz带宽,适用于多种通信标准。FMCOMMS3

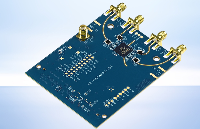

AFE8092八通道RF收发器技术解析与应用指南

Texas Instruments AFE8092八通道RF收发器是一款高性能、高带宽、多通道收发器,集成了八个RF采样发送器链、八个

德州仪器AFE80xx系列RF采样收发器技术解析与应用设计指南

Texas Instruments AFE80xx RF采样收发器是高性能、宽带宽多通道收发器系列,集成了多达八个RF采样DAC和十个RF采

【PZSDR AD9361】——璞致PZ-FL9361 软件无线电模块:工业级射频解决方案的技术标杆

璞致电子推出PZ-FL9361软件无线电模块,搭载ADI AD9361射频芯片,实现70MHz-6GHz宽频覆盖与56MHz可调带宽,支持2T2R架构与工业级环境应用。模块兼容主流FPGA平台与开源

CAN收发器:总线信号的“翻译官”

在CAN总线通信中,CAN收发器(Transceiver)扮演着至关重要的角色——它就像一位“翻译官”,负责将微控制器(MCU)的数字信号转换为总线上的差分信号,同时把总线信号翻译回MCU能理解

AD9361

我使用AD9361芯片,参考时钟为10MHz,鉴相频率为20MHz,设置BBPLL频率为800MHz,ADC_CLOCK为BBPLL的2分频,为400MHz,clock_OUT为ADCclock的8

发表于 06-25 15:02

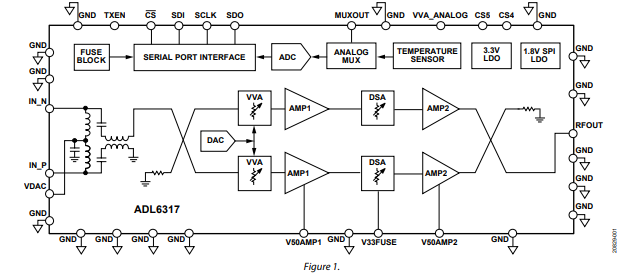

ADL6317用于RF DAC和收发器的发射VGA技术手册

ADL6317 是一款发射可变增益放大器 (VGA),它可提供从射频数模转换器 (RF DAC)、收发器和片内系统 (SoC) 到功率放大器的接口。集成式平衡/不平衡转换器和混合耦合

光纤收发器与IO-Link收发器的区别

在工业自动化和通信领域,光纤收发器和IO-Link收发器都是关键的通信组件,它们在数据传输、网络扩展和设备连接方面发挥着重要作用。然而,两者在设计、功能、应用场景以及技术特性上存在显著差异。本文将

无线收发器工作原理,无线收发器怎么使用

无线收发器作为现代通信技术的重要组成部分,广泛应用于各个领域,包括无线通信、物联网、远程控制和无线传感器网络等。本文将深入探讨无线收发器的工作原理,同时提供详细的使用方法。

高速接口7系列收发器GTP介绍

1. 前言 最近在做以太网相关的东西,其中一个其中想要使用MAC通过光电转换模块来完成数据的收发。在Artix7系列FPGA当中,有GTP这个高速收发器。我手上的板子上的核心芯片是ZYNQ7015

AD9361 RF捷变收发器,评估套件和开发资源

AD9361 *附件:AD9361_cn 中文数据手册.pdf 是一款面向3G和4G基站应用的高性能、高集成度的射频(RF)Agile Transceiver™捷

影响光纤收发器性能的三大因素

光纤收发器作为现代通信网络的重要组成部分,发挥着关键的作用。通过有效地解决连接器的脏污或损坏、信号衰减以及过热等问题,可以很大程度上提升光纤收发器的稳定性和性能,确保网络的高速、稳定运行。定期维护和检查设备,以及采用适当的技术手

AD9361 RF捷变收发器的应用分析

AD9361 RF捷变收发器的应用分析

评论