静态随机存取存储器(Static Random-Access Memory,SRAM)是随机存取存储器的一种。所谓的“静态”,是指这种存储器只要保持通电,里面储存的数据就可以恒常保持。相对之下,动态随机存取存储器(DRAM)里面所储存的数据就需要周期性地更新。然而,当电力供应停止时,SRAM储存的数据还是会消失(被称为volatile memory),这与在断电后还能储存资料的ROM或闪存是不同的。

SRAM不需要刷新电路即能保存它内部存储的数据。而DRAM(Dynamic Random Access Memory)每隔一段时间,要刷新充电一次,否则内部的数据即会消失,因此SRAM具有较高的性能,但是SRAM也有它的缺点,即它的集成度较低,功耗较DRAM大 [1] ,相同容量的DRAM内存可以设计为较小的体积,但是SRAM却需要很大的体积。同样面积的硅片可以做出更大容量的DRAM,因此SRAM显得更贵。

一种是置于cpu与主存间的高速缓存,它有两种规格:一种是固定在主板上的高速缓存(Cache Memory);另一种是插在卡槽上的COAST(Cache On A Stick)扩充用的高速缓存,另外在CMOS芯片1468l8的电路里,它的内部也有较小容量的128字节SRAM,存储我们所设置的配置数据。还有为了加速CPU内部数据的传送,自80486CPU起,在CPU的内部也设计有高速缓存,故在Pentium CPU就有所谓的L1 Cache(一级高速缓存)和L2Cache(二级高速缓存)的名词,一般L1 Cache是建在CPU的内部,L2 Cache是设计在CPU的外部,但是Pentium Pro把L1和L2 Cache同时设计在CPU的内部,故Pentium Pro的体积较大。Pentium Ⅱ又把L2 Cache移至CPU内核之外的黑盒子里。SRAM显然速度快,不需要刷新操作,但是也有另外的缺点,就是价格高,体积大,所以在主板上还不能作为用量较大的主存。

SRAM主要用于二级高速缓存(Level2 Cache)。它利用晶体管来存储数据。与DRAM相比,SRAM的速度快,但在相同面积中SRAM的容量要比其他类型的内存小。

SRAM芯片时字操作大同小异,在这里总结一一些它们共性的东西,也提一些用Verilog简单的快速操作SRAM的技巧。

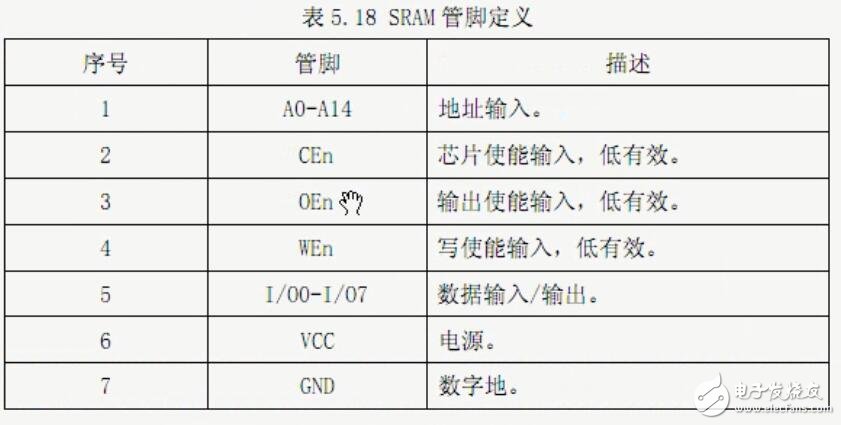

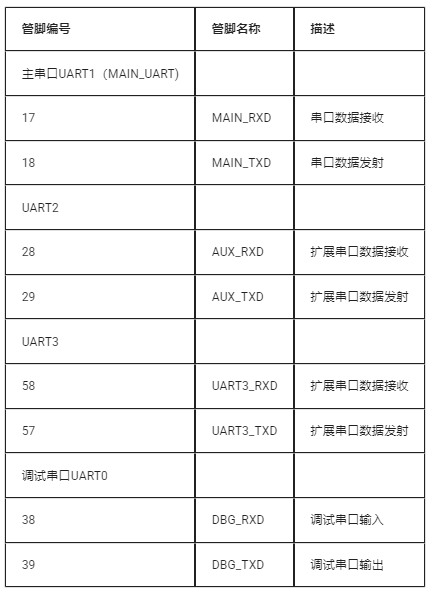

这里就以本实验使用的IS62LV256-70U为例进行说明。其管脚定义如表所示。

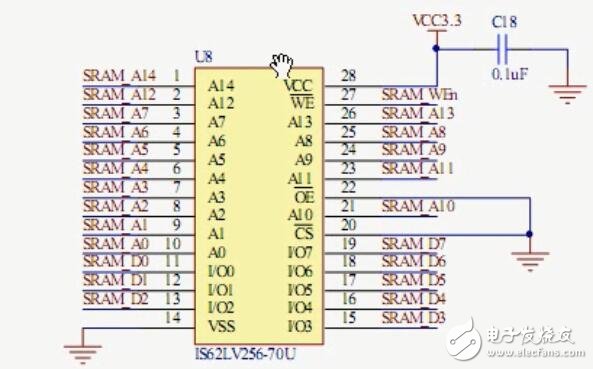

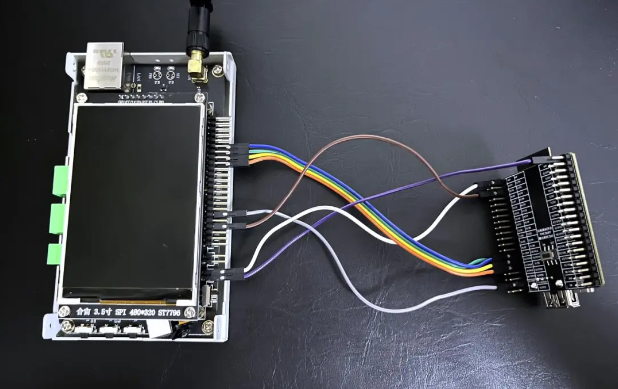

具体在硬件连接的时候,其实很多人喜欢直接把输出使能信号0En和片选信号CEn接地,这样一-来不仅节省了处理器和SRAM连接的管脚数,而且在读写SRAM的时候其实只要对写使能信号WEn操作就可以了,简化了代码部分。本设计的硬件原理图如图所示。

关于更多BJ-EPM240学习板之SRAM读写实验请看视频。

-

存储

+关注

关注

13文章

4693浏览量

89569 -

sram

+关注

关注

6文章

808浏览量

117220

发布评论请先 登录

AT32F系列 使用DMA将数据从FLASH传输到SRAM

高速数据存取同步SRAM与异步SRAM的区别

外置SRAM与芯片设计之间的平衡

DMA硬件实现——读写实现

如何利用Verilog HDL在FPGA上实现SRAM的读写测试

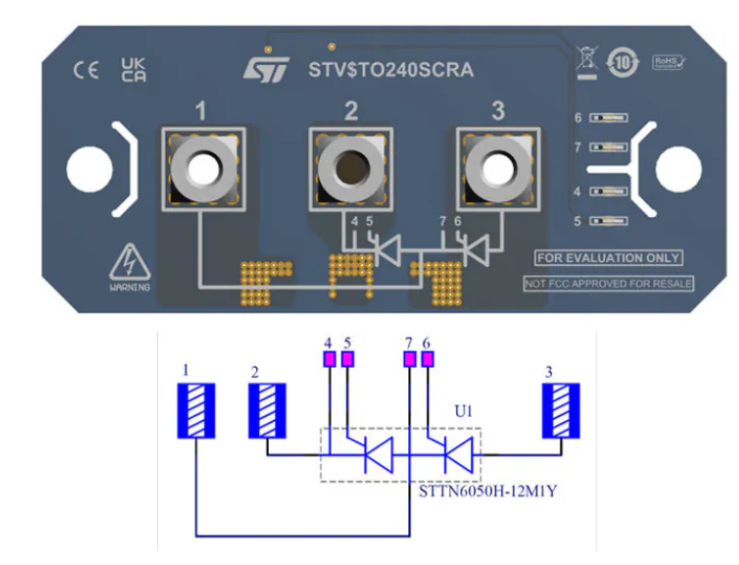

STEVAL-TO240SCR评估板技术解析与应用指南

全网首发!基于RV1126BJ设计的工规型号核心板EAI1126B-Core-TI正式发布啦

基于RV1126BJ设计的工规型号核心板EAI1126B-Core-TI正式发布啦!

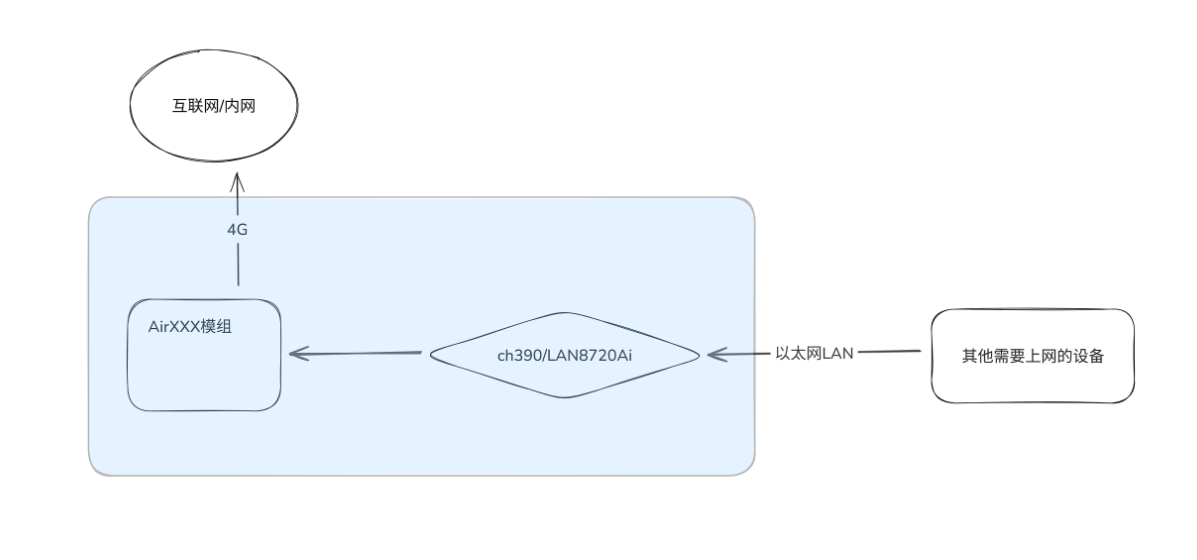

实战Air780EPM:构建4G共享网关,服务WiFi与有线设备!

基于ZYNQ的创世SD NAND卡读写TXT文本实验

F429同时使用SDRAM和SRAM?

【RK3568+PG2L50H开发板实验例程】FPGA部分 | DDR3 读写实验例程

Air8101多网融合战略升级:Air780EPM模块助力4G联网落地

深度解析——使用Luatools工具烧录一个具体的项目到Air780EPM核心板中!

Air780EPM 模块串口电路设计硬件指导

BJ-EPM240学习板之SRAM读写实验

BJ-EPM240学习板之SRAM读写实验

评论