在本视频中,将了解Artix-7 FPGA的整体系统功耗和成本。 我们将快速回顾一下Artix-7 FPGA架构,逻辑架构,第四代DSP48E1片,6.6 Gbps GTP收发器,PCIe Gen2硬块,存储器接口。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

dsp

+关注

关注

559文章

8214浏览量

363832 -

FPGA

+关注

关注

1655文章

22281浏览量

630051 -

赛灵思

+关注

关注

33文章

1797浏览量

133132

发布评论请先 登录

相关推荐

热点推荐

请问如何将蜂鸟E203移植到Xilinx NEXYS A7 FPGA 开发板上?

如何将蜂鸟E203移植到Xilinx NEXYS A7 FPGA 开发板上?有参考教程吗?小白求教

主要是引脚分配,我这边有移植到Xilinx Artix-7 系列XC7A100T-f

发表于 11-11 07:44

如何不用olimex ARM-USB-TINY-H debugger实现调试?

我用的板子是Nexys4 DDR,也就是Artix-7 100T,具体型号是xc7a100ticsg324-1L。

我到e200_opensource/fpga/artydevkit/script

发表于 11-10 08:15

一代蜂鸟E203移植普通Artix7核心板中IDE的cfg配置文件修改

大家好,本次我们团队想要分享的是如何将一代蜂鸟E203移植入自己的FPGA并协同NucleiStudio进行Debug时,其中cfg配置文件的修改;

首先我们使用的是Xilinx Artix-7

发表于 10-29 06:45

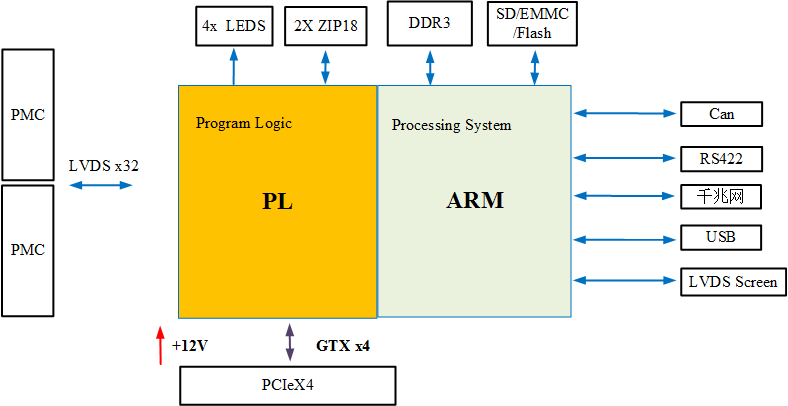

PCIe接口卡设计原理图:124-基于XC7Z015的PCIe低速扩展底板

板卡由SoC XC7Z015芯片来完成卡主控及数字信号处理,XC7Z015内部集成了两个ARM Cortex-A9核和一个Artix 7的FPGA

fpga开发板 璞致Artix-7系列之PA-Starlite Artix7 A735T 75T 100T 200T开发板用户手册-学习板

Artix-7系列开发板是一款基于Xilinx XC7A35T/75T/100T/200T芯片的低成本FPGA开发平台。该系列开发板具有功耗低、体积小(90x60mm)、外设丰富等特点

美乐威利用AMD FPGA打造最新USB视频采集棒

美乐威正采用 AMD Artix UltraScale+ FPGA 同时实施 USB 物理及数字层,消除了对外部控制器的需求。

是否需要买一个fpga开发板?

纠结要不要买个 FPGA 开发板?真心建议搞一块,尤其是想在数字电路、嵌入式领域扎根的同学,这玩意儿可不是可有可无的摆设。入门级的选择不少,全新的像 Cyclone IV、Artix 7 系列,几百块就能拿下,要是去二手平台淘淘

TLV3501输出有毛刺,有什么办法减少?

我采用TLV3501将混频后的50Hz正弦波变成方波,然后送入FPGA,对方波信号进行检测,发现方波信号有有毛刺导致FPGA误触发,有什么办法减少方波的毛刺呀

发表于 05-28 10:31

Xilinx Ultrascale系列FPGA的时钟资源与架构解析

Ultrascale是赛灵思开发的支持包含步进功能的增强型FPGA架构,相比7系列的28nm工艺,Ultrascale采用20nm的工艺,主要有2个系列:Kintex和Virtex

Altera Agilex 7 M系列FPGA正式量产出货

近日,全球 FPGA 创新技术领导者 Altera 宣布, Agilex 7 M 系列 FPGA 正式量产出货,这是现阶段业界领先的集成高带宽存储器,并支持 DDR5 和 LPDDR5 存储器技术

推荐一款MIP超低功耗显示屏1.28寸/LS013B7DH03 工作功耗低至50µW

LS013B7DH03是日本厦普SHARP推出的一款1.28寸超低功耗黑白显示屏(MIP),它在每个像素点嵌入了存储体,来存储图形数据,因此静止的图像不需要连续刷新,与传统TFT显示屏相比,减少

发表于 04-01 10:23

ADS7263功耗问题如何解决

,是12.0mA+1.1mA=13.1mA,而我实际测试的功耗在55mA,不知道是否正确,感觉有些大了。

我测试功耗的方法如下:

我的电路原理基本是,用FPGA驱动ADS7263,来采集模拟信号,ADS7263采集后将

发表于 01-20 09:07

使用IP核和开源库减少FPGA设计周期

/prologue-the-2022-wilson-research-group-functional-verification-study/),70% 的 FPGA 项目落后于计划,12% 的项目落后计划 50% 以上。 为此,很多FPGA厂商都在自己EDA工具里嵌入I

【米尔-Xilinx XC7A100T FPGA开发板试用】测试一

感谢米尔电子和电子发烧友提供的米尔-Xilinx XC7A100T FPGA开发板。

MYD-J7A100T用的 FPGA 为 XILINX 公司

发表于 12-08 08:48

将AFE7769DEVM与Hitek Agilex eSOM7 FPGA连接

电子发烧友网站提供《将AFE7769DEVM与Hitek Agilex eSOM7 FPGA连接.pdf》资料免费下载

发表于 12-05 13:51

•1次下载

如何使用Artix-7 FPGA减少功耗

如何使用Artix-7 FPGA减少功耗

评论