在电力系统中,感应耐压是考核变压器、电抗器和电压互感器等电气设备绝缘强度的一项重要功能测试,在DL/T474.4-2006《现场绝缘试验实施导则》中明确规定互感器、变压器除了做主绝缘之外,还应该对互感器、变压器的匝间、层间、断间等纵绝缘的绝缘性能试验,可以有效检查绕组线圈的完好性!

感应耐压试验方法

感应耐压不同于工频耐压,工频耐压是在一次侧施加工频高压,而感应耐压是在变压器或者互感器的低压侧施加比额定电压高一定倍数的倍频电压,依靠变压器自身的电磁感应在高压绕组上得到所需的试验电压来检验变压器的纵绝缘性能,特别是对中性点分级绝缘的变压器,由于不能采用外施高压进行工频交流耐压试验,其主绝缘和纵绝缘均由感应耐压试验来考核,感应耐压的测量应使用符合国家标准的SFQ-H电子式多倍频发生器或者是简易版的三倍频电源发生器进行测量。

感应耐压与工频耐压的区别

工频交流耐压试验只检查了绕组主绝缘的电气强度,即高压、中压、低压绕组间和对油箱、铁芯、外壳等接地部分的绝缘,而感应耐压是检查匝间、层间、断间等纵绝缘的绝缘性能试验,它们之间是相互补充,但不可相互代替的功能。

感应耐压有以下作用

(1) 考核全绝缘变压器,半绝缘互感器、全绝缘互感器的纵绝缘;

(2)考核分级绝缘变压器的部分主绝缘和纵绝缘。

作者:鼎升电力 www.kv-kva.com 转载请注明

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

发布评论请先 登录

相关推荐

热点推荐

RDMA设计1:开发必要性1之设计考虑

。

一. 选择 RDMA IP 开发必要性

为了满足大批量数据的采集、 存储与传输需求, 如机器学习、 雷达、 ⾦融⻛控、 航空航天等, 如何在 FPGA 上实现高带宽、 低延时的数据传输以

发表于 11-19 14:30

嵌入式软件测试与专业测试工具的必要性深度解析

系统化解决方案,其必要性体现在多个维度:满足行业合规要求汽车电子ISO 26262、航空DO-178C等标准强制要求代码覆盖率指标达到C1(分支覆盖)≥100%、MC/DC(修正条件判定覆盖)≥100

发表于 09-28 17:42

数据中台对接MES系统的必要性体现在哪方面

数据中台对接MES(制造执行系统)的必要性体现在 数据整合与共享、生产过程透明化、决策支持智能化、系统协同与效率提升、灵活性与可扩展性 等多个层面,能够打破数据孤岛、挖掘数据价值,推动制造业向智能化

利用传感器强化基坑安全监测的必要性

在城市化向纵深发展的今天,基坑变形安全监测已非锦上添花,而是工程安全与城市运行的刚性需求,其必要性源于多重现实挑战:工程风险与日俱增:规模与深度挑战:现代基坑日益呈现“大、深、近、杂”的特点——规模

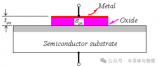

半导体硅表面氧化处理:必要性、原理与应用

特性。本文从半导体硅表面氧化的必要性出发,深入探讨其原理、方法、优势以及在集成电路、微电子器件等领域的广泛应用,旨在揭示表面氧化处理在推动半导体技术发展中的重要作

直流SPD系统中后备保护器(SCB)的必要性及行业应用方案

的核心区别在于:直流故障电流不存在自然过零点,一旦SPD因过载或老化发生短路故障,故障电流会持续存在且难以通过传统断路器切断,可能引发火灾或设备损毁。因此,在直流SPD前端加装SCB(Surge Protective Device Circuit Breaker)后备保护器具有以下必要性:

高考考场引入身份证人脸识别终端考务通的必要性

终端这一先进的身份验证技术。下面,我们将详细探讨高考考场使用身份证人脸识别终端的必要性。首先,使用身份证人脸识别身份核验终端、刷脸核验一体机或人证对比终端可以大大

构建智慧校园建设的必要性

智慧校园建设本质上是一场以信息技术为核心的教育革命,其技术架构的先进性与创新性直接决定了校园数字化转型的深度与广度。从底层基础设施到上层应用服务,智慧校园构建了一个完整的技术生态系统。 一、物联网

汉思新材料:国际关税贸易战背景下电子芯片胶国产化的必要性

国际关税贸易战背景下电子芯片胶国产化的必要性分析一、引言近年来,中美关税贸易战持续升级,双方在半导体、电子设备等关键领域展开激烈博弈。美国通过加征关税(如对华商品最高税率达145%)、限制技术出口

国电西高无局放感应耐压及交流耐压试验装置顺利验收

近日,湖北大客户采购国电西高的GDYT-300kW/2600KVA/500KV无局放感应耐压及交流耐压试验装置顺利完成现场验收!

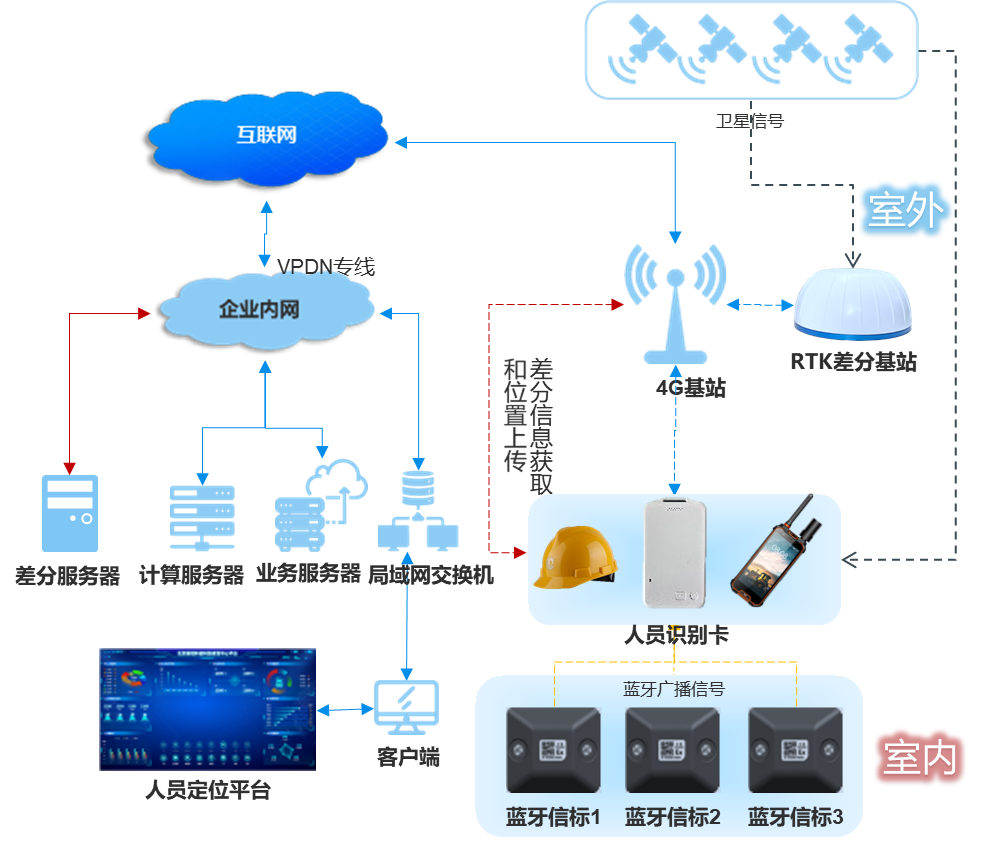

石油开发企业部署人员定位系统的必要性及方案解析

开发企业而言,这更是一项具有战略意义的举措。本文将以新锐科创的RTK+蓝牙+4G融合定位系统为范例,深入阐释石油开发企业部署人员定位系统的必要性及该系统的卓越性能。 一、石油开发企业面临的定位困境 恶劣自然环境阻碍定位

DBF系列多倍频感应耐压装置产品说明

变压器和互感器的感应耐压试验是保证变压器质量符合国家标准的一项重要试验。变压器绕组的匝间、层间、段间及相间绝缘的纵绝缘感应耐压试验,是变压器绝缘试验中的重要项目。基于纵绝缘试验中的特殊

发表于 03-11 15:11

•0次下载

感应耐压的必要性

感应耐压的必要性

评论