三分频扬声器系统分频器电感的精确设计,Coil design

关键字:分频器电感设计,音响分频器设计

三分频扬声器系统分频器电感的精确设计

1 引言

扬声器系统的分频器分为前级分频和功率分频2类。前级分频是前级电路中由电子元件产生的分频,再由各自的功放分别驱动高﹑中﹑低音扬声器系统,如图(1a)所示,属于小信号有源分频。而功率分频则是由电感、电容、电阻元件构成的位于功放与扬声器之间的无源分频电路,如图(1b)所示。

采用功率分频的扬声器系统结构简单、成本低,而且又能获得很高的放音质量,因而在现代高保真放音系统中应用最为普遍。其性能的好坏与扬声器的各项指标以及分频电路、电感元件的性能、精度有密不可分的关系,精确计算电感参数便是成功的关键。

2 对分频器电路、元件的要求

(1)电路中电感元件直流电阻、电感值误差越小越好。而且为使频响曲线平坦最好使用空心电感。

(2)电路中电容元件损耗尽可能小。最好使用音频专用金属化聚丙烯电容。

(3)使各扬声器单元分配到较平坦的信号功率,且起到保护高频扬声器的作用。

(4)各频道分频组合传输功率特性应满足图2所示特性曲线的要求(P0为最大值,P1为对应分频点f1、f2的值)。分频点处的功率与功率最大值之间幅度应满足P1(=0.3~0.5)P0的范围。

(5)整个频段内损耗平坦,基本不出现“高峰”和“深谷”。

3 分频电感电容参数值的计算

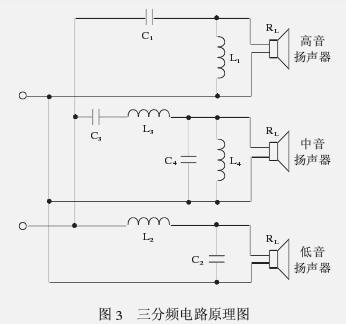

下面以三分频分频器为例说明其参数的计算,如图3所示。

(1)计算分频电感L1,L2,L3,L4和分频电容C1,C2,C3,C4。

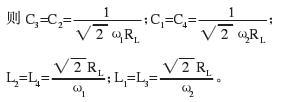

为了得到理想的频谱特性曲线,理论计算时可取:C1=C4,C3=C2,L1=L3,L4=L2,分频点频率为f1,(f2见图2),则分频点ω1=2πf0,ω2=2πf2。并设想高、中、低扬声器阻抗均相同为RL。每倍频程衰减12 dB。

(2)实验修正C1,C2,C3,C4,L1,L2,L3,L4的值

为精确起见,可用实验方法稍微调整C1,C2,C3,C4,L1,L2,L3,L4的值,以满足设计曲线﹙见图2﹚的要求。即通过实验描绘频响曲线,从而得到C1,C2,C3,C4,L1,L2,L3,L4的最佳值。如果没有实验条件,这一步也可不做。求出电容电感的值后就可计算电感值了。

4 最佳结构电感的作用

4.1最佳结构电感的提出

空心分频电感(简称电感)的基本参数是电感量和直流电阻。一般来说,电感量不准会导致分频点偏离设计要求并可能影响扬声器系统的频响,大家都比较重视。然而其直流电阻不宜过大,否则会对音质产生影响。通常人们对此电阻在电路中的影响及其定量要求不甚了解,因此未引起足够重视,对此特作以下简要分析。

以图3的分频网络为例,由于低音单元的分频电感L2与负载R(L低音单元额定阻抗)相串联,因此若L2的阻抗过大,功放输出功率在其上的损耗将增大。同时,功放内阻对低音单元的阻尼作用也将大大减弱。前者影响功放的有效输出功率,后者对音质的影响却无可挽回。由于分频网络中L2的电感量最大,且随分频点的降低而增大,所以L2的直流电阻的影响相当突出。

至于高音单元的分频电感L1,因它未与负载串联,就不存在L2那样的功耗和阻尼问题。但是仍希望其阻抗尽可能小些。因为它与负载并联,起着旁路来自C1的残余低音频成分的作用。若阻值过大,就会影响高音分频网络对低音频的衰减陡度。

综上所述,电感直流电阻的数值在理论上是越小越好,实际应用中对电感直流电阻数值的要求,应从减小它对电路的影响方面去考虑。具体说又分2种情形,对与负载串联的电感(如L2),应从允许的功率损耗和有足够的阻尼两方面去考虑;对与负载并联的电感(如L1),则主要从具有足够的旁路作用去考虑。

对L2电阻影响功率损耗和L1电阻影响旁路作用的处理原则相同,即应使L1和L2的阻抗R远小于扬声器的额定阻抗R(L即R<

对同一电感量,其绕组结构可任意多。因此空心电感线圈必然存在一个最佳结构尺寸,它应使电感量L对其电阻R之比L/R达到最大值。即可找出一套合理绕制空心电感线圈的经验计算公式,与其它方法得出的结构尺寸相比,相同的电感值具有最小的阻抗值。

其实电感结构是否最佳很容易从其外形判别。如果绕组截面大致呈正方形,且绕组内径为绕组宽度(即绕组高度)的4倍,那么基本上属于最佳结构。

结构最佳的电感线圈应该用料省、体积小,并可使电感量和电阻同时满足预先给定的数值。

由于对每一电感值和电阻值均有一个最佳结构尺寸,因此应舍弃传统的计算方法求取、制作电感。因为传统方法不经测试修正难以满足最佳要求。

下面介绍改用经验公式的计算方法,此方法能满足最佳要求。而且它对一些特殊结构尺寸的电感计算精确度也很高。

4.2最佳结构电感的计算

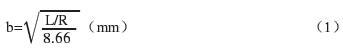

设所需电感量为L(μH),其阻抗值为R(Ω),先求出绕组的结构参数

参数b是绕组的高度(宽度),决定了绕组的内径和外径。所以求得b后即可按图4制作绕组骨架,其中骨架外径适当加大10%左右,然后求取

其中,N为绕组匝数,d为导线铜芯直径,i为导线总长度,w为导线总重量。

根据铜芯直径d从线规表中选取对应的标称直径,由导线总重量可选购足够用量的高强度漆包线。

采用该计算方法绕制的电感经与实验对比,误差一般小于5%,绕制后是否测量已无关紧要了,基本上能满足直接应用的要求。

由于以上绕制方法中,实际使用导线铜芯直径D总是选得比计算直径d大一些,从而造成绕制后的电感量总比计算值低些,显然,加长绕制导线长度,即多绕几匝就可使实际电感量更接近计算值。实际绕制导线的总长度可由

k=0.4[(D/d)-i] (6)

I(=i+k)i (7)

求出。其中k为实际导线的加长系数,I为实际绕制导线总长度,把长度I全部绕入骨架即可。D为实际导线直径。

如计算1 mH、电阻值为0.8Ω的空心电感线圈的最佳结构尺寸及绕制参数。将数值代入式(1)~式(5)得

骨架的中心轴外径取2b=24 mm,骨架两夹板间距为b=12 mm,骨架夹板外径取4b=48 mm,(实际制作时可加大10%)。计算结果如下

b=12 mm;2b=24 mm;N=181.5匝;d=0.75 mm;i=20.52 m;w=81 g。

如果采用导线直径实际为D,则用k=0.4([D/d)-i],I(=i+k)i进行修正。采用该方法计算出L1,L2,L3,L4的值,照图装配即可。

作为计算验证,笔者按Hi-Vi S8 plus扬声器系统分频器的参数制作了一个家用扬声器系统。其中2只0.55 mH和0.18 mH的电感按上述结果计算制作,实测电感值为0.565 mH和0.187 mH。误差不超过5%。说明此法绕制的电感量准确。通常该计算法即使没有电感表测量,电感误差也不超过5%。

将该计算法与以往的图表法比较,还可体会出该方法的优点:用料省、体积小、不需绘制图表、误差小。

发布评论请先 登录

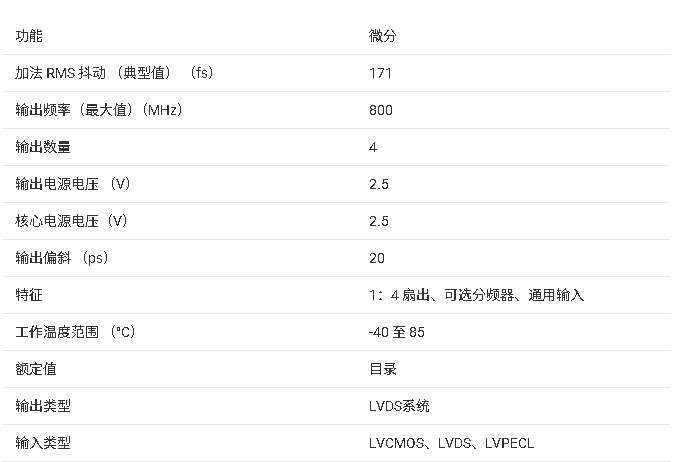

高频分频器/PLL 合成器 ADF4007:技术剖析与应用指南

SN74LS292和SN74LS294可编程分频器与数字定时器的技术解析

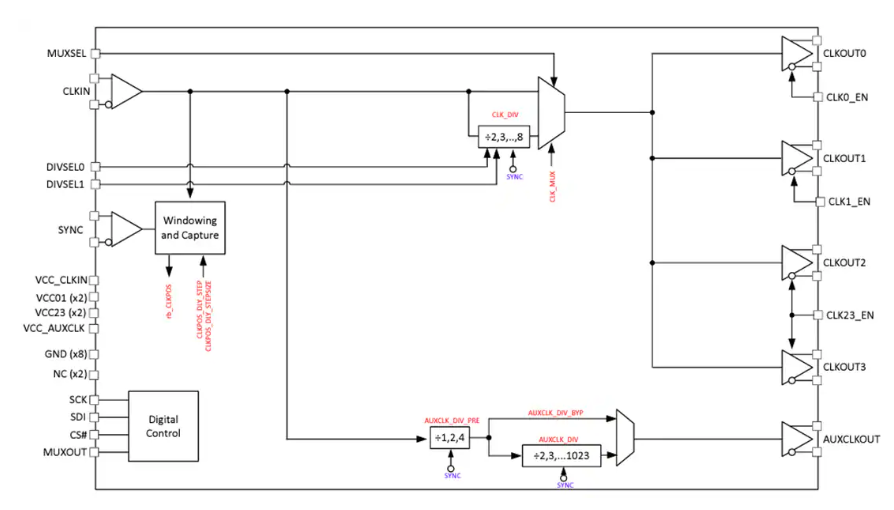

CDC5801A:低抖动时钟倍频器与分频器的卓越之选

LMX1214:高性能低噪声时钟缓冲及分频器的技术剖析

LMX1204:低噪声、高频JESD缓冲器/倍增器/分频器的卓越之选

LMX1214:高性能低噪声时钟缓冲与分频器的深度解析

CDCLVD1213 1:4低附加抖动LVDS缓冲器带分频器 技术文档摘要

德州仪器LMX1214射频缓冲器与分频器技术解析

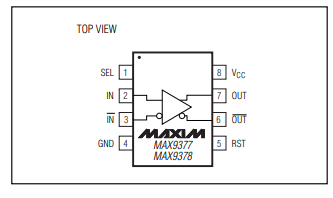

MAX9377/MAX9378任意逻辑至LVPECL/LVDS转换器,引脚可设置四分频电路技术手册

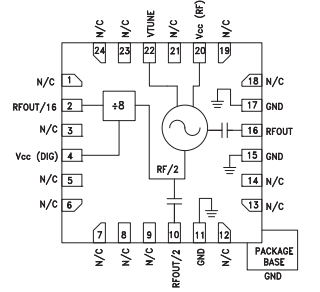

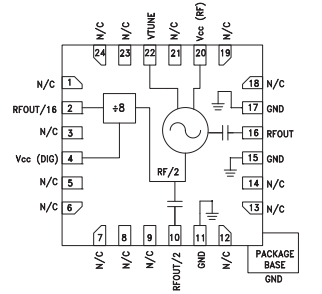

HMC739LP4/739LP4E具有半频输出和16分频的MMIC VCO,23.8-26.8GHz技术手册

HMC738LP4/738LP4E具有半频输出和16分频的MMIC VCO,20.9-23.9GHz技术手册

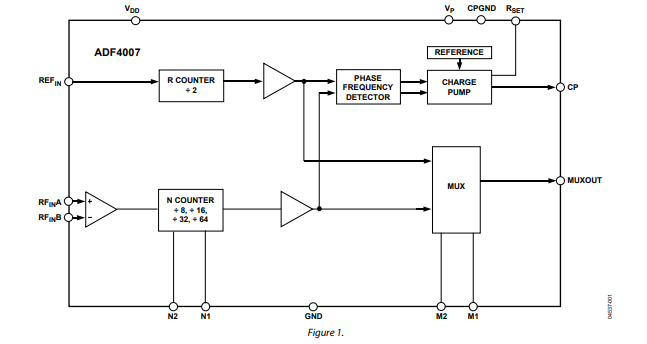

ADF4007高频分频器/PLL频率合成器技术手册

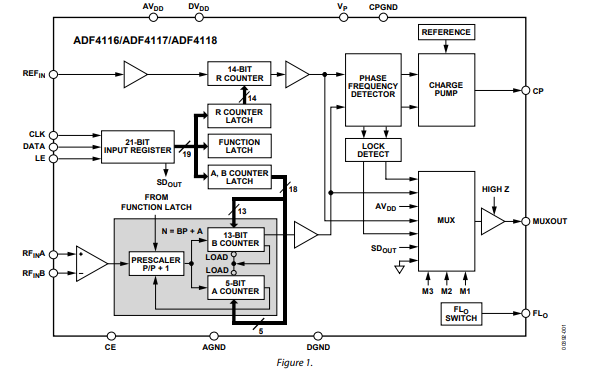

ADF4116/ADF4117/ADF4118单通道、整数N分频550MHz PLL技术手册

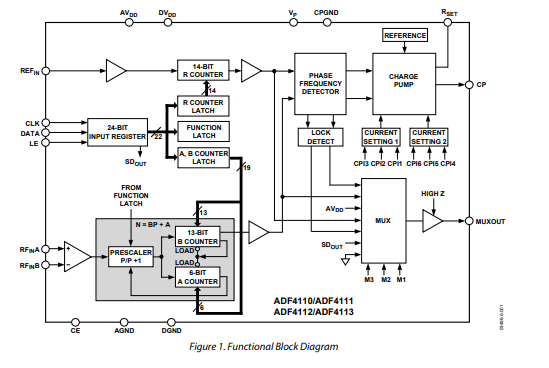

ADF4110/ADF4111/ADF4112/ADF4113单通道、整数N分频、550 MHz PLL,内置可编程预分频器和电荷泵技术手册

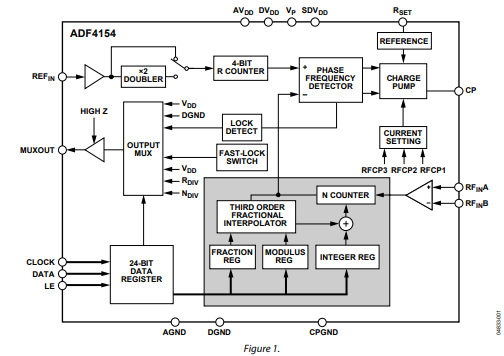

ADF4154小数N分频频率合成器技术手册

三分频扬声器系统分频器电感的精确设计,Coil design

三分频扬声器系统分频器电感的精确设计,Coil design

评论