引 言

SoPC可编程片上系统是一种特殊的嵌入式微处理器系统。首先,它是片上系统(SoC),即由单个芯片完成整个系统的主要逻辑功能;其次,它是可编程系统,以FPGA为硬件基础,具有灵活的设计方式,可裁减、可扩充、可升级,并具备软硬件系统在线可编程的功能。

IP(Intellectual Property)知识产权是SoC设计中非常重要的内容。资源复用(IP Reuse)是指在集成电路设计过程中,通过继承、共享或购买所需的部分或全部知识产权内核(IP Core)进行设计、综合和验证,从而加速流片设计过程的设计方法。IP技术包含两个方面的内容:IP核的生成和IP核的重用。本设计中采用VHDL语言,构建一个功能强大的完整DDS模块,并根据IBM CoreConnect总线连接规范,在DDS模块外面添加OPB(On?chip Peripheral Bus)片上外设总线接口,封装为自定义IP,添加到硬件系统中。

对于本设计来说,利用SoPC和IP的优势是可以利用最少的元器件,创建一个易配置、易扩展、易修改并且易于继承使用的集成系统。该系统的创建是基于Xilinx公司提供的嵌入式开发工具包EDK(Embedded Development Kit)来实现的。EDK自带了MicroBlaze软核和PowerPC硬核微处理器及大量免费IP,有利于构建简易系统。针对MicroBlaze及PowerPC提供的C语言编译器,可使系统的功能实现更加简易。对基于MicroBlaze的系统,MicroBlaze通过OPB总线与外设IP及外部存储器控制接口相连接,通过LMB(Local Memory Bus)总线与FPGA片上块存储器BRAM(Block RAM)相连接,还可以通过EMC(External Memory Control)等存储器控制IP扩展片外RAM或ROM。

1 系统的架构

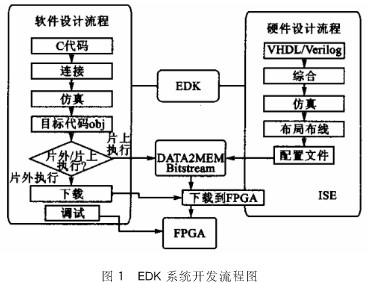

本设计采用SoPC可编程片上系统的思想,利用Xilinx的Spartan3系列XC3S400 FPGA,通过EDK开发工具包的集成开发环境XPS(Xilinx Platform Studio)完成了FPGA硬件系统设计及基于此硬件系统的软件开发。图1是基于EDK的系统开发设计流程图,设计分为硬件设计和软件设计两部分。硬件设计符合基于HDL硬件描述语言的EDA开发流程,是根据硬件系统合理使用总线IP和外设IP,并为各个实例定义地址范围以及输出端口和时钟,经过综合及布线后形成硬件配置文件。软件设计与传统的嵌入式软件开发设计类似,是在硬件设计的基础上根据处理器所支持的指令集以及编译环境编写程序代码,然后对代码编译烧写及调试。

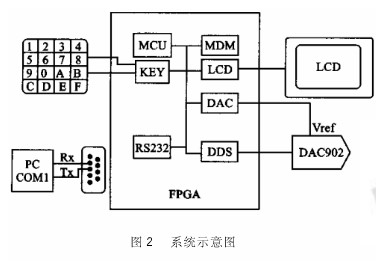

该设计通过FPGA实现所有数字部分。系统的示意图如图2所示。

在FPGA内部,以MicroBlaze为控制核心,以DDS IP为波形发生功能实现核心,同时加入了其他的IP核,诸如调试用的MDM(Microprocessor Debug Module),用于与PC进行通信的UART(Universal Asynchronous Receiver & Transmitter)通用异步传输模块,以及LCD显示和4×4按键控制模块,实现了系统的高度集成。FPGA硬件系统为数字系统产生数字量,外围电路加上高速数模转换器件DAC902,把波形数据转换为模拟波形,即实现了完整的可编程片上系统的波形发生器。

2 硬件系统的具体实现

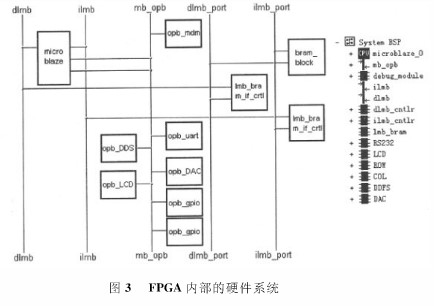

本设计以32位MicroBlaze软核处理器为系统的核心部分,负责指令的执行。各种IP包括自主编写的以及EDK自带的,使用XPS下的ADD/Edit Cores工具,通过相应类型的总线连接到MicroBlaze上。其中UART、LCD、GPIO和自主编写的DDS的IP都是通过OPB(On?chip Peripheral Bus)片上外设总线连接到处理器上的。程序存储器RAM则是由FPGA内部的BRAM实现,并通过LMB(Local Memory Bus)本地存储器总线与MicroBlaze相连接。自主编写的IP与总线间的接口符合CoreConnect规范,实现了IP间的无缝结合,方便了数据的读写及时序控制。图3给出了在FPGA内部由各种IP组合成的可编程硬件系统。

硬件系统所包含的器件如图3右部分所示。Microblaze_0是该系统的CPU,其中的debug_module为调试模块,dlmb_cntlr和 ilmb_cntlr为片上BRAM控制器。Lmb_bram为片上BRAM,它通过LMB总线与 BRAM控制器相连,接受CPU的读写访问。DDFS是为实现DDS编写的IP模块。RS232为UART模块,用于与其他设备的通信以及程序调试。LCD IP负责128×64点阵液晶的显示控制。 COL和ROW是例化后的GPIO接口,用于连接4×4键盘。

2.1 MicroBlaze软核处理器

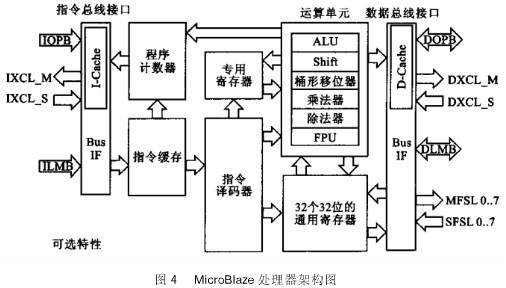

MicroBlaze是Xilinx提供的32位微处理器IP核,是哈佛结构的RISC微处理器,有较高的性能。它可以在性价比很高的SpartanIII系列FPGA上实现。EDK为其提供了MBGCC,支持C及C++语言。 MicroBlaze架构如图4所示。

该处理器含有32个32位的通用寄存器,2个专用寄存器,独立的32位数据和指令总线,并与IBM的OPB总线完全兼容,具有32位的指令宽度支持三个操作数和两种寻址模式,以及可选的硬件乘除法及浮点运算单元。

2.2 DDS IP的实现

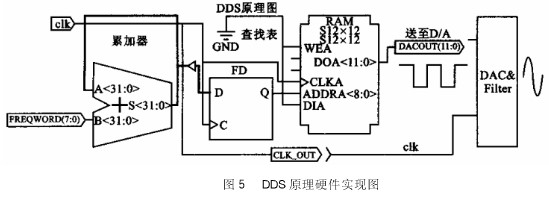

数字直接频率合成技术(Direct Digital Frequency Synthesis,简称DDS或DDFS)的基本原理是利用采样定理,通过查表法产生波

形,其基本电路原理如图5所示。

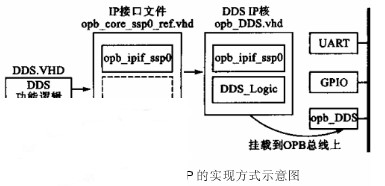

DDS的频率及步进容易控制,且合成的频率取决于累加器及查找表的速度,采用FPGA可以很好的发挥这项优势,获得精细的步进及宽频带。使用HDL硬件描述语言,可以很方便的描述出DDS的FPGA硬件实例。在基本的DDS模块上,添加相应的控制寄存器,通过向不同的寄存器内写入相应的控制字,实现频率以及幅度的可控性。最后通过IBM CoreConnect技术,在DDS模块外面添加总线接口,作为自定义IP,成功地将其挂载到系统总线上,便可以方便的对其进行读写操作,实现DDS模块与MicroBlaze的通信。图6是从用户逻辑到成为符合IBM CoreConnect技术规范的DDS IP的实现过程。

DDS的VHDL代码作为子模块与opb_core_ssp0_ref.vhd模块共同构成opb_DDS IP Core,其中ipif(IP InterFace )符合IBM CoreConnect规范,负责DDS逻辑与OPB总线之间的通信。在EDK中,通过Create/Import IP工具把opb_DDS添加到系统中,并为其分配地址,建立端口连接,之后就可以使用该IP了。DDS IP配合控制程序可产生各种波形,并对频率、幅度进行精确的控制。

2.3 其余部分

系统所需要的LCD显示、DAC控制等模块,均通过与生成DDS IP相同的方式,编写为符合IBM CoreConnect总线规范的IP,以供使用。

在硬件系统构建完毕之后,使用Platgen工具生成网表文件和Bitgen工具生成相应的硬件配置文件。若将工程导入到ISE软件中,可以进行优化设置,还可以将工程导入到其他的综合工具如Synplify Pro进行实现。IP核的编写是在ISE中完成的。无论对于整个系统还是一个单独的IP,都可以利用Modelsim工具进行行为及时序仿真。最后,为此系统描写XBD(Xilinx Board Description)板级描述文件,通过此文件,EDK可以通过BSB(Base System Builder)模式自动生成基本的硬件系统,并对所添加的端口进行约束,这样可以实现资源的继承性使用。

3 软件系统的实现

EDK提供了免费的GNU C Compiler,可以支持标准C。同时,EDK为多种IP以API的形式提供了驱动函数,有利于程序的开发。XPS所集成的软件工程管理工具允许在一个硬件平台上同时开发多个软件工程。完成软件代码的编写后,使用EDK集成的XMD和GDB调试器对代码进行仿真和调试,也可以配合ChipScope(片内逻辑分析仪)进行硬件及软件的协同调试。XMD通过MDM模块和JTAG口连接目标板上的CPU,GDB可以对程序进行单步调试或断点设置。针对本设计及应用,编写了系统控制及液晶显示程序。程序编译后生成为elf文件,通过Update bitstream工具把程序同硬件配置文件合成为Download.bit文件,把此文件下载到目标板后,FPGA首先根据硬件配置信息建立硬件系统,并把程序代码映射到片内BRAM中,最后启动MicroBlaze,运行程序。

4 总结

本系统基于FPGA,以MicroBlaze为核心,加入具有良好特性的DDS IP,并辅以必要的外围电路,构成了高度集成化的系统。另外,SoPC系统的柔性配置,使得可以基于此系统扩展片外存储器,并可以实现RTOS操作系统的移植,以实现更丰富的功能和完成更复杂的任务。

-

集成电路

+关注

关注

5446文章

12468浏览量

372687 -

操作系统

+关注

关注

37文章

7328浏览量

128632 -

波形发生器

+关注

关注

3文章

313浏览量

32557

发布评论请先 登录

手机应用中的可编程片上系统器件

MicroBlaze处理器的PetaLinux操作系统怎么移植?

可编程SoC(SoPC),什么是可编程SoC(SoPC)

基于片上可编程系统解决方案实现视频编解码IP核的设计

在SoPC可编程片上系统上实现RTOS操作系统的移植

在SoPC可编程片上系统上实现RTOS操作系统的移植

评论