任意波形发生器(ArbitraryWaveGenerator,以下简称AWG)在通信系统、测试系统等方面得到广泛应用。本文利用自主研制的150MSPS(MillionSamplingPerSecond)12位DAC(DigitalAnalogConverter)和300MSPS12位DAC,基于CPLD技术,设计了一种AWG。要产生的波形通过上位机软件设置,然后将波形数据下载到AWG,AWG在CPLD的高速控制电路下将波形数据送高速DAC进行转换形成所要的波形。下面先分析AWG的硬件结构。

任意波形发生器的硬件结构

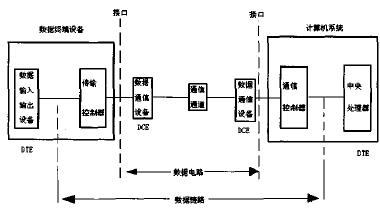

AWG的工作过程是,首先接收上位机送来的波形数字信号存储到SRAM,然后启动控制电路从SRAM取出数据送DAC进行数摸转换,转换后的模拟信号送低通滤波器形成波形。如果DAC工作在150MSPS的速度下,可以以150MHz的频率送数据到DAC进行转换,微控制器的晶振输入一般工作在40MHz以下,没有这么高的速度送出数据到DAC,所以考虑采用CPLD构建硬件控制电路。数据首先传送到SRAM,然后在CPLD硬件控制电路的控制下,以150MHz的频率从SRAM中取数送DAC转换。其体系结构如图一所示。如果要形成正弦周期信号,每周期4个点就可以合成一个波形,此时可以输出约38MHz的高频信号。

CPLD(ComplexProgrammableLogicDevice,复杂可编程逻辑器件)是在传统的PAL、GAL基础上发展而来的,具有多种工作方式和高集成、高速、高可靠性等明显的特点,在超高速领域和实时测控方面有非常广泛的应用。与FPGA相比,CPLD比较适合计算机总线控制、地址译码、复杂状态机、定时/计数器、存储控制器等I/O密集型应用,且无须外部配置ROM、时延可预测等。目前的CPLD普遍基于E2PROM和Flash电可擦技术,可实现循环擦写。Altera公司的MAX7000CPLD配置有JTAG口,支持ISP编程。用VHDL或VerilogHDL(HardwareDescriptionLanguage,硬件描述语言)设计的程序,借助EDA工具经过行为仿真、功能仿真和时序仿真后,通过综合工具产生网表,下载到目标器件,从而生成硬件电路。

本装置中,CPLD采用Altera公司的EPM7128AE,其最高工作频率达200MHz。微控制器采用Atmel公司AVR微控制器AT90S8515,其主要特征有:增强型RISC体系结构CPU,8KFlash,512字节EEPROM,512字节InternalSRAM,UART,SPI,宽电压范围:2.7-6.0V。SRAM选用64Kx16的CY7C1021V。

下面对CPLD控制电路进行分析。

CPLD电路设计

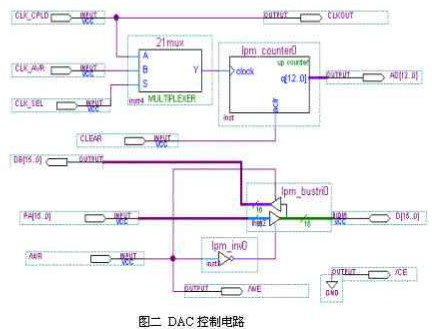

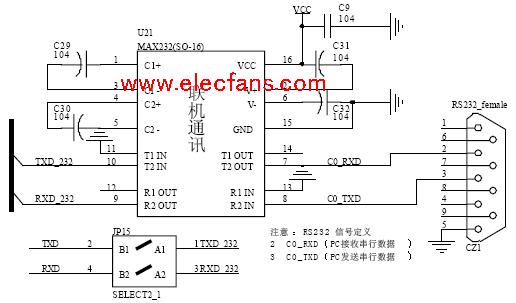

CPLD主要负责以高速率(150MHz)从SRAM中取数到DAC,其核心电路是一个13位的计数器。波形数据文件的大小为8Kbytes。如果要扩大波形文件的大小,可以根据需要增加CPLD的地址计数器容量。在CPLD内部构造的DAC控制电路如图二所示,下面对其控制流程进行分析。

PA[15:0]接AT90S8515的2个8位并行口;D[15:0]接SRAM的数据线D0-D15;AD[12:0]接SRAM的地址线A0-A12;DB[15:0]接DAC的D0-D11(D12-D15不用);CLK_SEL选择计数器的时钟输入方式;CLK_AVR接MCU的一个I/O端,通过软件编程在CLK_AVR输出脉冲信号作为计数器的时钟;CLK_CPLD接150MHz时钟信号;/WR和/WE接MCU的I/O端。

当PC机下载数据时,其控制流程如下:

①CLK_SEL=0,选择软件时钟

②复位地址计数器

③MCU送数据到PA[15:0]

④/WR从0变到1,打开从MCU到SRAM的数据缓冲器将数据写入SRAM

⑤给CLK_AVR一个脉冲,让计数器增1从而指向SRAM的下一个接收地址单元。

当数据下载完成后,启动CPLD从SRAM取数据到DAC,其控制流程如下:

①WE=1,打开从SRAM到DAC的缓冲器。

②CLK_SEL=1,计数器的输入时钟选择150MHz的外部时钟,

③复位地址计数器,外部高速时钟的驱动下地址计数器开始计数,从SRAM中取出数据送到DAC进行数据转换。

CPLD的编程在QuartusII5.0环境下进行,Quartus的设计输入支持AHDL、VHDL、VerilogHDL等硬件描述语言的程序输入和图形输入,这里采用图形输入的方式。完成设计输入后,依次进行编译、功能仿真、时序仿真。下图三是CPLD取数据到DAC进行转换的时序仿真结果。图中CPLD的工作频率为125MHz,实际工作中最高工作在200MHz,从图中可以看出,每来一个时钟,CPLD从SRAM中取出一个数据送DAC进行A/D转换。最后将结果下载到CPLD内部运行。

软件设计

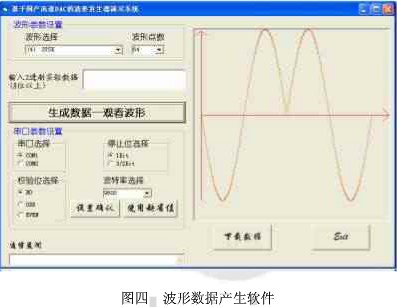

AWG的软件采用CodeVisionAVRC编写,AT90S8515支持ISP(InSystemProgramming,在系统编程),程序编译后经JTAG口下载到AT90S8515中。为配合该装置的使用,我们在VB开发环境下设计了上位机软件,其运行界面如图四所示,在该软件中选择要产生的波形,然后下载到AWG。

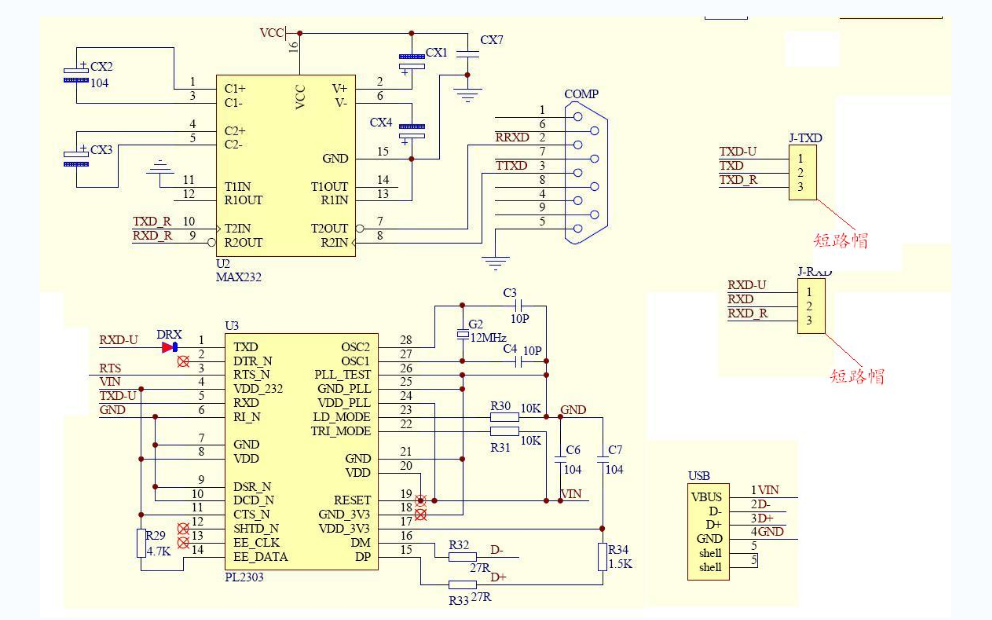

AWG和PC机采用RS-232串口通信,上电运行后等待PC传送波形,接收完波形数据后,启动CPLD从SRAM中取出数据送DAC进行D/A转换,经低通滤波器形成输出波形。

结语

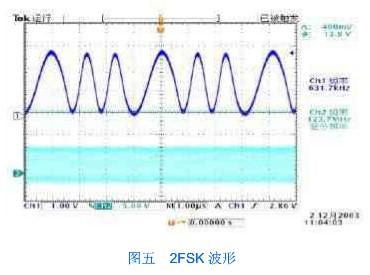

AWG和PC机通过RS232串口连接后,运行PC机软件,在PC机上选择要生成的波形,生成波形数据下载到AWG,可以选择线性调制技术的绝对相移键控(BPSK)、相对相移键控(DPSK)、四相相移键控(QPSK)、交错正交相移键控(OQPSK)、π/4偏移差分相移键控(π/4—DQPSK),恒包络调制的二进制频移键控(FSK)、最小频移键控(MSK)、高斯滤波最小频移键控(GMSK),混合线性和恒包络调制技术的M相相移键控(MPSK)、多进制正交幅度调制(QAM)、多进制频移键控(MFSK)等波形,下载到AWG生成所要的波形。下图五是DAC工作在125MHz下合成的2FSK(FrequencyShiftKey)波形。

-

cpld

+关注

关注

32文章

1259浏览量

173289 -

通信

+关注

关注

18文章

6316浏览量

139546 -

计数器

+关注

关注

32文章

2306浏览量

97563

发布评论请先 登录

在计算机应用3种扩展出RS-232串口的方法介绍

计算机扩展RS-232串口的三种方法和区别及应用

实现RS232串口通信的资料合集

基于CPLD技术与RS-232串口通信实现任意波形发生器的连接设计

基于CPLD技术与RS-232串口通信实现任意波形发生器的连接设计

评论