引言

在当今的电子技术领域,模拟 - 数字转换器(ADC)扮演着至关重要的角色。它们是连接现实世界模拟信号与数字系统的桥梁,广泛应用于通信、雷达、测试测量等众多领域。TI公司的ADC11C125就是一款高性能的11位A/D转换器,它以其卓越的性能和丰富的特性,为工程师们提供了一个强大的工具。今天,我们就来深入剖析这款ADC11C125,了解它的技术特点、应用场景以及设计要点。

文件下载:adc11c125.pdf

一、产品概述

ADC11C125是一款高性能的CMOS模拟 - 数字转换器,能够以高达125兆样本每秒(MSPS)的速率将模拟输入信号转换为11位数字字。它采用了差分流水线架构,结合数字误差校正和片上采样保持电路,在降低功耗和外部组件数量的同时,提供了出色的动态性能。其独特的采样保持级实现了1.1 GHz的全功率带宽,使其适用于多种高频应用场景。

(一)主要特性

- 高带宽:全功率带宽达到1.1 GHz,能够处理高频输入信号。

- 低功耗:典型功耗为608 mW,并且支持掉电和睡眠模式,进一步降低功耗。

- 内部参考:具备内部精密1.0V参考,也可使用外部参考。

- 灵活的时钟模式:支持单端或差分时钟模式,以及时钟占空比稳定器。

- 多种输出格式:提供偏移二进制或2的补码输出数据格式。

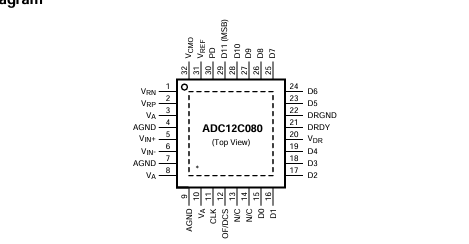

- 引脚兼容:与ADC14155、ADC12C170、ADC11C170引脚兼容。

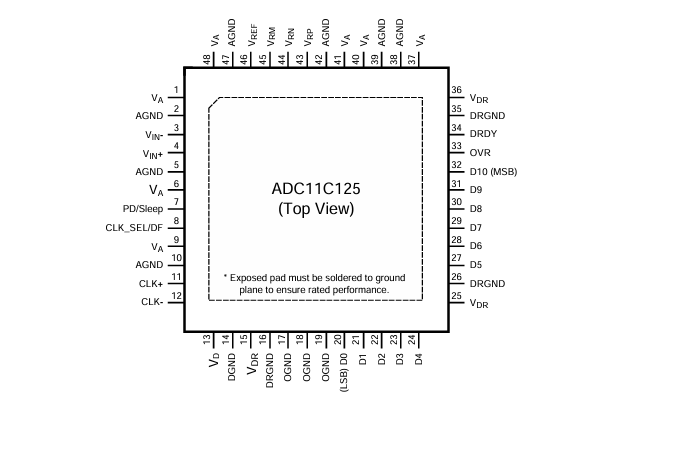

- 小型封装:采用48引脚WQFN封装(7x7x0.8mm,0.5mm引脚间距)。

(二)应用领域

- 高IF采样接收器:用于处理高频中频信号的采样。

- 无线基站接收器:提高基站接收信号的处理能力。

- 功率放大器线性化:优化功率放大器的性能。

- 多载波、多模式接收器:适应复杂的通信环境。

- 测试和测量设备:提供高精度的信号采集。

- 通信仪器:保障通信系统的稳定运行。

- 雷达系统:实现雷达信号的准确处理。

二、关键规格参数

(一)基本参数

- 分辨率:11位

- 转换速率:125 MSPS

- 信噪比(SNR):在$f_{IN}=70 MHz$时,典型值为65.5 dBFS

- 无杂散动态范围(SFDR):在$f_{IN}=70 MHz$时,典型值为88.2 dBFS

- 有效位数(ENOB):在$f_{IN}=70 MHz$时,典型值为10.5位

- 全功率带宽:典型值为1.1 GHz

- 功耗:典型值为608 mW

(二)静态特性

| 参数 | 条件 | 典型值 | 极限值 | 单位 |

|---|---|---|---|---|

| 分辨率(无缺失码) | - | 11位(最小) | - | - |

| 积分非线性(INL) | 满量程输入 | ±0.25 |

-0.83 LSB(最小) 0.83 LSB(最大) |

LSB |

| 差分非线性(DNL) | 满量程输入 | ±0.20 | -0.55 LSB(最小) | LSB |

| 正增益误差(PGE) | - | +1.1 |

-1.8 %FS(最小) 4.0 %FS(最大) |

%FS |

| 负增益误差(NGE) | - | -0.77 |

-3.7 %FS(最小) 2.2 %FS(最大) |

%FS |

| 增益误差温度系数(TC GE) | -40°C ≤$T_{A}$ ≤ +85°C | TBD | - | ppm/°C |

| 偏移误差(VOFF) | $V{IN+} = V{IN-}$ | -0.11 |

-1.03 %FS(最小) 0.78 %FS(最大) |

%FS |

| 偏移误差温度系数(TC VOFF) | -40°C ≤$T_{A}$ ≤ +85°C | TBD | - | ppm/°C |

| 欠量程输出码 | - | 0 | 0 | - |

| 过量程输出码 | - | 2047 | 2047 | - |

(三)动态特性

| 参数 | 条件 | 典型值 | 极限值 | 单位 |

|---|---|---|---|---|

| 全功率带宽(FPBW) | -1 dBFS输入,-3dB转角 | 1.1 | - | GHz |

| 信噪比(SNR) | $f_{IN}=10 MHz$ | 65.7 | 64.5 | dBFS |

| $f_{IN}=70 MHz$ | 65.5 | - | dBFS | |

| $f_{IN}=146 MHz$ | 65.4 | - | dBFS | |

| $f_{IN}=220 MHz$ | 64.9 | - | dBFS | |

| $f_{IN}=398 MHz$ | 64.5 | - | dBFS | |

| 无杂散动态范围(SFDR) | $f_{IN}=10 MHz$ | 87.1 | 76.0 | dBFS |

| $f_{IN}=146 MHz$ | 83.4 | - | dBFS | |

| $f_{IN}=220 MHz$ | 84.9 | - | dBFS | |

| $f_{IN}=398 MHz$ | 75.7 | - | dBFS | |

| 有效位数(ENOB) | $f_{IN}=70 MHz$ | - | 10.4 | 位 |

| $f_{IN}=146 MHz$ | - | 10.4 | 位 | |

| $f_{IN}=220 MHz$ | - | 10.4 | 位 | |

| $f_{IN}=10 MHz$ | 10.6 | - | 位 | |

| $f_{IN}=398 MHz$ | 10.3 | - | 位 | |

| 总谐波失真(THD) | $f_{IN}=10 MHz$ | -83.3 | - | dBFS |

| $f_{IN}=70 MHz$ | -85.7 | - | dBFS | |

| $f_{IN}=146 MHz$ | -79.5 | -76.4 | dBFS | |

| $f_{IN}=220 MHz$ | -81.8 | - | dBFS | |

| $f_{IN}=398 MHz$ | -74.1 | - | dBFS | |

| 二次谐波失真(H2) | $f_{IN}=10 MHz$ | -97.7 | - | dBFS |

| $f_{IN}=146 MHz$ | -83.4 | - | dBFS | |

| $f_{IN}=220 MHz$ | -98.0 | - | dBFS | |

| $f_{IN}=398 MHz$ | -82.2 | - | dBFS | |

| 三次谐波失真(H3) | $f_{IN}=10 MHz$ | -88.2 | - | dBFS |

| $f_{IN}=70 MHz$ | -90.8 | - | dBFS | |

| $f_{IN}=146 MHz$ | -85.8 | - | dBFS | |

| $f_{IN}=220 MHz$ | -84.9 | - | dBFS | |

| $f_{IN}=398 MHz$ | -75.7 | - | dBFS |

三、功能描述

(一)工作原理

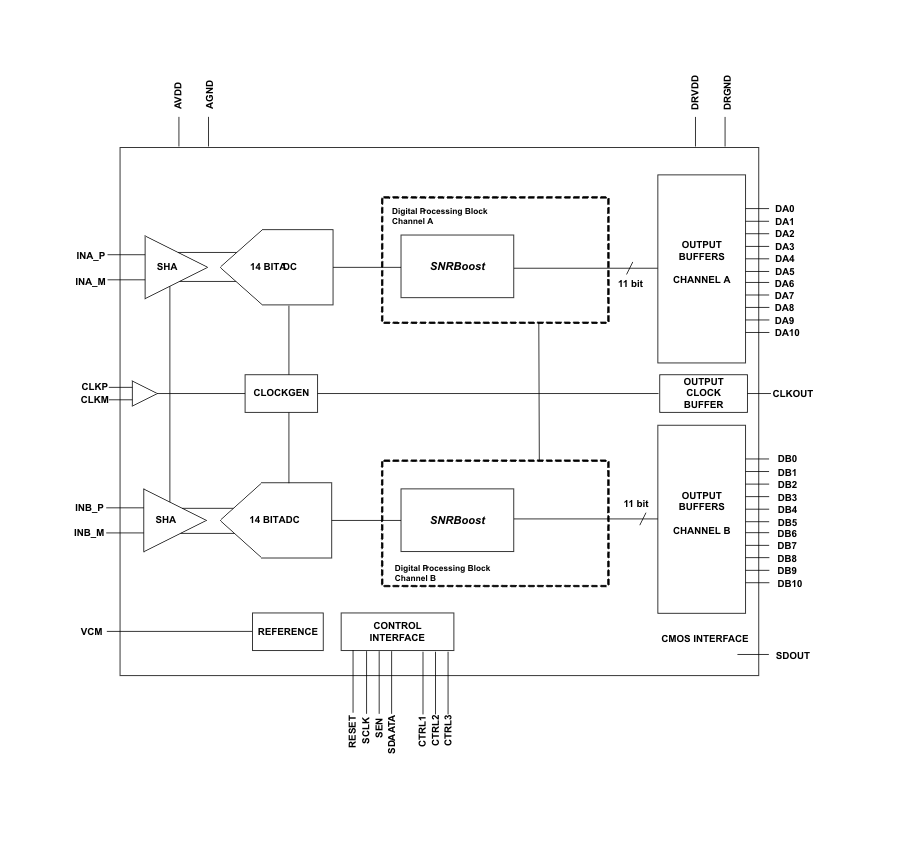

ADC11C125采用差分流水线架构,结合数字误差校正和片上采样保持电路。在采样阶段,模拟输入信号通过NMOS开关连接到采样电容,电容跟踪输入信号的变化。当时钟从高电平变为低电平时,进入保持阶段,模拟输入与采样电容断开,采样电容上的电压被保持并送入ADC核心进行转换。转换结果以11位数字字的形式输出,输出格式可以是偏移二进制或2的补码。

(二)时钟与数据输出

时钟信号控制采样过程,模拟输入在时钟的下降沿被采集。用户可以通过CLK_SEL/DF引脚选择单端或差分时钟模式,以及输出数据格式。数字输出是CMOS兼容信号,由同步数据就绪输出信号(DRDY)进行时钟控制,数据在DRDY信号的下降沿输出,并延迟7个时钟周期。数据应在DRDY信号的上升沿进行捕获。

(三)功率管理

通过PD/Sleep引脚可以选择掉电或睡眠模式。当PD/Sleep引脚为高电平时,除电压参考电路外的所有电路都被禁用,功耗降至5 mW。当PD/Sleep引脚偏置为$V_{A} / 2$时,芯片进入睡眠模式,除电压参考电路及其片上缓冲器外的所有电路都被禁用,功耗降至50 mW。正常操作时,PD/Sleep引脚应连接到模拟地(AGND)。

四、应用设计要点

(一)模拟输入

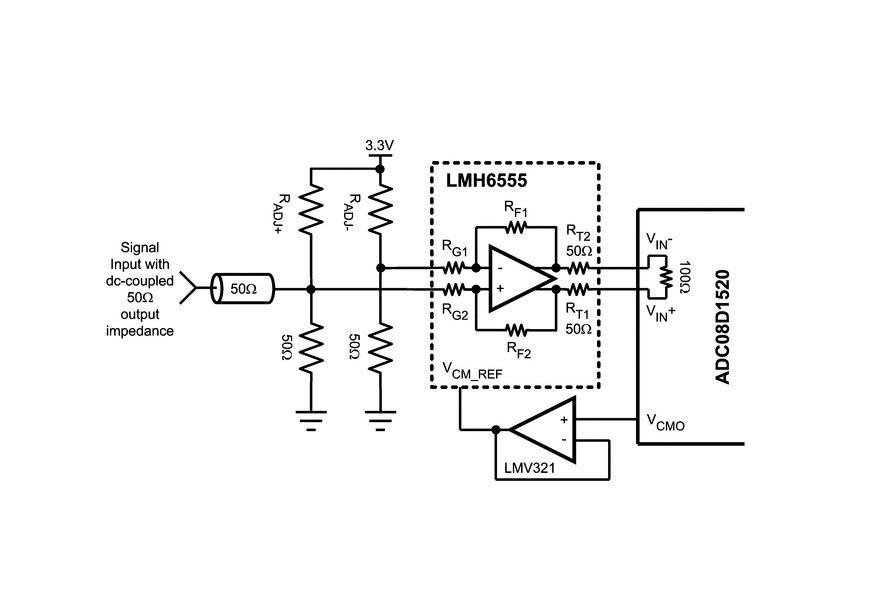

- 信号输入:ADC11C125有一对差分模拟输入引脚$V{IN}+$和$V{IN}-$,输入信号应满足一定的幅度和相位要求。建议使用源阻抗小于100Ω的信号源驱动模拟输入,并匹配差分输入的源阻抗,以提高偶次谐波性能。

- 采样保持电路:模拟输入引脚的电容在采样和保持阶段会发生变化,采样阶段约为9 pF,保持阶段约为6 pF。在设计时需要考虑这种电容变化对信号的影响,确保采样电容能够在时钟信号变低之前稳定充电,以避免影响SFDR性能。

- 单端转差分转换:对于单端输入信号,可以使用变压器或差分放大器进行转换。变压器适用于高频输入信号,但低频性能较差;差分放大器适用于低频应用,需要能够快速从采样保持操作引起的充电毛刺中恢复。

- 输入共模电压:输入共模电压$V{CM}$应在1.4V至1.6V之间,建议使用$V{RM}$(引脚45)作为输入共模电压,以确保模拟信号的峰值不超过地或2.6V。

(二)参考引脚

ADC11C125可以使用内部1.0V参考或外部参考,外部参考电压范围为0.9V至1.1V。$V_{REF}$引脚应始终通过一个0.1 µF电容旁路到地。较低的参考电压会降低ADC的信噪比,而高于1.1V的参考电压可能会在满量程输入时降低THD,特别是在较高输入频率下。所有与参考电压和模拟输入信号相关的接地应在一个安静的单点连接到接地平面,以减少接地路径中的噪声电流影响。

(三)时钟输入

- 时钟模式选择:通过CLK_SEL/DF引脚可以选择单端或差分时钟模式,以及输出数据格式。在差分时钟模式下,两个时钟信号应相差180°且幅度相同;在单端时钟模式下,时钟信号应连接到CLK+输入,CLK - 输入应连接到AGND。

- 时钟信号质量:为了获得最佳的噪声性能,时钟输入应使用稳定、低抖动的时钟信号,并且具有较短的过渡区域。可以通过高速缓冲门对低抖动正弦时钟源进行处理来实现。时钟线应尽可能短,避免与其他信号线路交叉。

- 时钟线终端匹配:时钟线应在其源端进行特性阻抗终端匹配,以保持时钟线阻抗的恒定。如果时钟源驱动多个设备,每个驱动引脚应通过串联RC到地进行交流终端匹配,以减少反射和干扰。

- 时钟占空比:ADC11C125具有占空比稳定器,能够在30%至70%的时钟占空比范围内保持性能稳定。

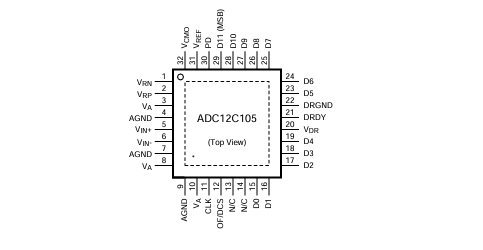

(四)数字输出

- 输出信号:ADC11C125的数字输出包括11个数据输出位(D0 - D10)、数据就绪信号(DRDY)、过范围指示(OVR)和三个输出接地引脚(OGND)。数据应在DRDY信号的上升沿进行捕获和锁存。

- 负载电容:驱动高电容总线时需要特别小心,因为输出驱动器需要为每个转换充电的电容越大,瞬时数字电流就越大,可能会导致片上接地噪声并耦合到模拟电路中,降低动态性能。应确保输出电容不超过指定的5 pF/引脚,以避免影响$t_{OD}$和动态性能。

- 噪声抑制:为了减少输出开关引起的噪声,应尽量减少数字输出的负载电流。可以使用可编程逻辑器件(PLD)进行电平转换,将ADC输出数据从1.8V转换为3.3V。每个输出引脚应只连接一个负载,并在数字输出端插入约22Ω的串联电阻,以限制输出电流。

(五)电源供应

- 电源旁路:每个电源引脚应通过一个0.1 µF电容和一个0.01 µF陶瓷芯片电容进行旁路,优先选择无铅芯片电容,以降低串联电感。

- 电源噪声:ADC11C125对电源噪声敏感,模拟电源引脚的噪声应保持在100 mVP - P以下。在电源开启和关闭过程中,要特别注意避免引脚电压超过电源电压。

- 输出驱动器电源:$V{DR}$引脚为输出驱动器提供电源,电压范围为1.6V至2.0V。较低的$V{DR}$电压可以降低功耗和噪声耦合,但会增加$t_{OD}$。如果需要将ADC11C125的数字输出信号与非1.8V CMOS设备接口,可能需要使用电平转换器。

(六)布局和接地

- 分区布局:将电路板分为模拟和数字区域,ADC11C125应位于这两个区域之间。所有模拟电路应放置在模拟区域,所有数字电路和动态I/O线应放置在数字区域。

- 接地处理:数据输出的接地返回(DRGND)应避免与ADC11C125的其他接地引脚在近距离连接到系统地,以防止输出电流的高瞬变对转换过程产生噪声影响。所有与参考电路和输入信号链连接到地的组件应通过短走线连接在一起,并在一个安静的单点进入接地平面。

- 信号布线:模拟和数字线路应尽量避免交叉,时钟线应尽可能短,并与所有其他线路隔离,包括其他数字线路。电感和变压器应避免并排放置,以防止磁耦合。模拟输入应与噪声信号迹线隔离,外部组件应连接到接地平面的干净点。

五、动态性能优化

为了实现最佳的动态性能,驱动CLK输入的时钟源必须具有尖锐的过渡区域和无抖动。可以使用缓冲器将ADC时钟与任何数字电路隔离,如时钟树所示。时钟树中使用的门必须能够在比实际使用频率高得多的频率下工作,以防止引入额外的抖动。与差分时钟相比,单端驱动输入可以获得更好的性能。

六、总结

ADC11C125是一款功能强大、性能卓越的11位A/D转换器,适用于多种高频、高性能应用场景。在设计应用时,需要充分考虑其模拟输入、参考引脚、时钟输入、数字输出、电源供应、布局和接地等方面的要求,以确保其能够发挥最佳性能。通过合理的设计和优化,ADC11C125可以为工程师们提供一个可靠的解决方案,满足各种复杂应用的需求。

希望本文能够对广大电子工程师在使用ADC11C125进行设计时有所帮助。如果你在实际应用中遇到任何问题,欢迎在评论区留言讨论。让我们一起探索电子技术的无限可能!

-

CMOS

+关注

关注

58文章

6184浏览量

241539 -

带宽

+关注

关注

3文章

1029浏览量

43019 -

A/D转换器

+关注

关注

1文章

142浏览量

11593 -

数字转换器

+关注

关注

0文章

331浏览量

28624 -

输入信号

+关注

关注

0文章

549浏览量

13106

发布评论请先 登录

ADC11C125,pdf datasheet (11-Bi

AD9752:12位、125 MSPS高性能TxDAC<sup>®</sup>D/A转换器产品手册

AD9754:14位、125 MSPS高性能TxDAC<sup>®</sup>D/A转换器产品手册

ADC11C170CISQ 11位模数带宽A/D转换器的规格参数

ADS5517高性能11位、200 MSPS A/D转换器数据表

ADS5510高性能、11位、125 MSPS模数转换器(ADC)数据表

深入剖析ADC12C170:高性能12位A/D转换器的技术解析

深度剖析ADC11C125:高性能11位A/D转换器的技术与应用

深度剖析ADC11C125:高性能11位A/D转换器的技术与应用

评论