在当今数字化的时代,图像信号处理技术在众多领域发挥着至关重要的作用,无论是数字彩色复印机、扫描仪,还是其他图像处理应用,都对图像信号处理器提出了更高的要求。今天,我们就来深入探讨一款备受瞩目的产品——LM98620 10 - Bit 70 MSPS 6 通道成像信号处理器。

文件下载:lm98620.pdf

一、LM98620 概述

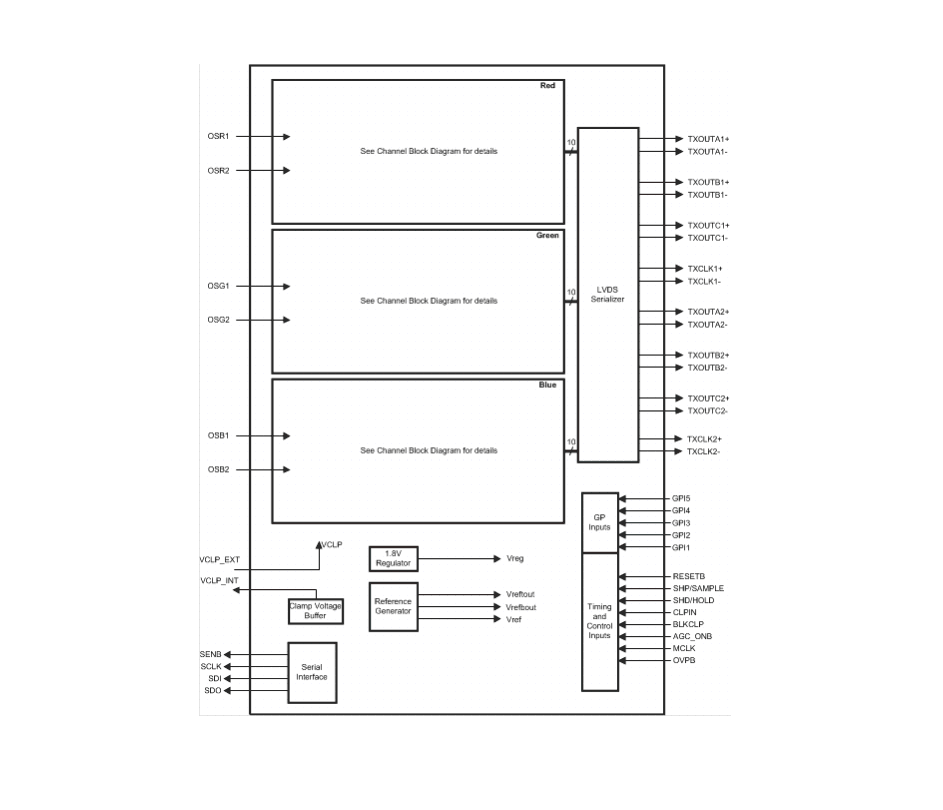

LM98620 是一款专为高性能数字彩色复印机、扫描仪及其他图像处理应用而设计的全集成式解决方案。它采用 10 - Bit 分辨率和 70 MSPS 的信号处理速度,凭借创新的六通道架构,结合相关双采样(CDS)或采样保持(SH)类型的采样技术,实现了高速信号处理。

1.1 关键特性

- 单电源供电:支持 3.3 V 单电源运行,简化了电源设计。

- 高通道速率:每个通道的速率可达 35 MHz,确保了高速的数据处理能力。

- ESD 保护增强:在时序、控制和 LVDS 引脚处采用了增强的 ESD 保护,提高了设备的可靠性。

- 低功耗设计:采用低功耗 CMOS 设计,降低了系统的功耗。

- 独立增益和偏移校正:每个通道都有独立的 1x 到 10x(8 位)可编程增益放大器(PGA)和 ±4 位粗调和 ±10 位细调的模拟偏移校正 DAC,可实现精确的增益和偏移调整。

- 数字校准功能:具备数字白电平自动校准和数字黑电平自动校准功能,可自动设置 PGA 值和偏移校正值,以达到选定的目标电平。

- LVDS 输出:提供 12 至 16 端子(可选)的 LVDS 串行数据输出,支持 4 线串行接口。

1.2 应用领域

- 数字彩色复印机和扫描仪:为这些设备提供高质量的图像信号处理,确保清晰、准确的图像复制和扫描。

- 其他图像处理应用:如工业检测、医疗成像等领域,也能发挥其高性能的优势。

二、详细技术分析

2.1 输入处理

许多传感器输入信号的共模电压与 LM98620 输入电路的共模电压不同,因此在应用中常采用交流耦合来阻断源与 AFE 输入之间的直流电压差。输入钳位电路用于将 AFE 输入设置在合适的共模电压上。

- 初始粗调钳位:可使用 PIB(无源输入偏置)和/或 AIB(有源输入偏置)电路进行初始粗调钳位。设置 PIB 使能位可将 1 kΩ 上拉和下拉电阻连接到输入,使其快速充电至 $V_{DDA} / 2$;设置 AIB 位可通过低阻抗开关将 VCLPEXT 参考电压连接到输入。但在正常操作期间,必须禁用 AIB 和 PIB。

- 图像捕获期间的黑电平钳位:在图像捕获期间,通过低阻抗开关将输入引脚连接到内部参考电压进行黑电平钳位。钳位会定期开启,以校正直流输入电压的任何下降,并最小化转换误差。钳位开关会在输入信号的“黑”部分开启,此时输入处于已知电压电平。钳位将输入连接到约 1.65 V 的参考电平,也可在 VCLPEXT 引脚施加客户提供的参考电压。

2.2 增益和偏移控制

- 增益控制:PGA 提供 1x 到 10x 的增益范围,分辨率为 8 位,增益曲线为 $Gain = 283 / (283 - M)$,其中 M 是 8 位增益设置值(0 到 255)。此外,CDS/SH 阶段提供 1x 或 2x 的增益,使整体通道增益达到 1x 到 20x(0 dB 到 26 dB)。

- 偏移控制:在 ADC 之前提供模拟偏移校正,使用两个偏移 DAC 提供粗调(CDAC)和细调(FDAC)偏移。偏移 CDAC 提供 ±280 mV 的范围,分辨率为 ±4 位;偏移 FDAC 提供 ±110 mV(大 FDAC 范围)或 ±59.5 mV(小 FDAC 范围)的范围,分辨率为 ±10 位。

- 黑电平校准:可通过手动或自动两种方法进行黑电平校正。手动方法适用于处理系统中所需的黑电平校正环在 LM98620 外部的情况,由外部处理器控制黑电平偏移寄存器;自动方法则通过启用黑电平偏移自动校准位,使用 CDAC 和 FDAC 来使输出收敛到所需的黑电平目标。

- 白电平校准:白校准环允许 LM98620 自动设置增益,以达到所需的最大 ADC 输出。通过数字输入引脚或配置寄存器位启动循环,处理定义的白像素范围内的输出数据。在处理过程中,执行移动窗口平均,并将窗口平均值与先前的峰值白值进行比较,更新峰值白值。如果 AGC_ONB 输入被脉冲触发,白校准环将在扫描开始时运行固定数量的行。

2.3 功能模式

LM98620 有多种功能模式,不同模式下的输入信号组合和处理方式有所不同。

- AFEPHASEn 与输入信号的组合:在 SHP/SHD 输入模式下,SHP 和 SHD 输入分别与选定的 AFEPHASEn 信号进行与运算,生成内部 CLAMP 和 SAMPLE 信号;在 SAMPLE 和 HOLD 输入模式下,SAMPLE 和 HOLD 输入生成的采样控制脉冲由 AFEPHASEn 信号的低电平周期进行门控,生成内部使用的 SAMPLE 信号。

- 6 通道和 3 通道模式:在 6 通道模式下,每个传感器像素周期有两个完整的 ADCCLK 周期,允许两个 AFE 通道复用至单个 ADC,有 4 种可能的 AFEPHASEn 时序;在 3 通道模式下,每个像素周期只有一个 MCLK 和 ADCCLK 周期,因此只有 2 种 AFEPHASEn 选择。

- 同步模式:LM98620 有三种主要的操作模式,在 6 通道模式使用 ADC 速率 MCLK 时,需要 CLPIN 输入信号与 MCLK 结合,以确保内部采样相位与像素速率输入信号同步。

2.4 编程与寄存器配置

编程对于 LM98620 的正常运行至关重要,需要对多个寄存器进行初始化和配置。

- 使用黑像素平均值:在大多数应用中,应设置黑像素平均值位。在白环操作期间,从 ADC_MAX 中减去黑像素平均值,得到当前的白值,用于与目标白像素值进行比较。在启动白环之前,需要初始化多个寄存器,如 PK_DET_ST、PKDET_WID、AGCDuration、AGCTarget 等。

- 采样时序控制:采样时序通过内部 AFEPHASEn 信号和编程的内部采样时序信号进行控制,也可使用外部采样时序信号。不同的输入时序模式由寄存器 0x00、0x02、0x04 和 0x05 中的位进行选择。

- DLL 基于的采样时序设置:内部 DLL 设置确定内部生成的采样脉冲的位置,仅适用于 SH2b 时序模式。通过设置寄存器位选择采样模式,AFEPHASE 寄存器设置粗采样时序框架,Sample Trailing Edge Position 寄存器设置采样脉冲的结束位置。

- 外部采样时序输入:不同模式下,内部采样或钳位和采样时序信号的生成方式不同。在 SH1a 和 CDSa 模式下,由选定的 AFEPHASEn 信号生成;在 SH1b 和 CDSb 模式下,输入信号由内部 AFEPHASEn 信号进行门控;在 SH2 模式下,SAMPLE 和 HOLD 时序信号直接输入到 AFE 的采样阶段;在 SH3 模式下,SAMPLE 和 HOLD 时序信号不仅直接输入到 AFE 的采样阶段,还用于设置后续阶段的内部 AFEPHASE 时序。

- LVDS 数据输出:AFE 数据通过串行化的 LVDS 接口输出,有多种串行化模式可供选择,如 6 对模式可使用标准的 DS90CR218A 或 DS90CR364 解串器 IC,5 对模式可使用单个 5 通道解串器,可通过断开未使用的数据对和 TXCLK 对来降低功耗和成本。

- 输出数据测试模式:可生成四种基本类型的测试模式,包括固定模式、水平渐变模式、垂直渐变模式和晶格模式。通过设置多个寄存器,如 PK_DET_ST、PK_DET_WID、PATSW、PATMODE 等,可控制测试模式的输出。

- 串行接口:串行控制接口基于常见的 Microwire 接口,有特定的时序细节。在设备上电并施加稳定的 MCLK 后,必须将串行接口模式(寄存器 0x01,位 3)设置为 1 以进行正常操作。串行写和读操作有各自的命令格式和时序要求。

三、应用与实现

3.1 应用信息

白环提供二进制搜索和增量搜索两种收敛到目标值的技术。二进制搜索算法旨在快速收敛到目标值,在初始操作期间允许通道增益有较大变化,后期切换到增量搜索模式以实现低误差;增量或线性搜索算法旨在提供低误差,但收敛速度较慢,通道增益的变化始终以 1 lsb 为增量,以实现低过冲和高收敛精度。

3.2 典型应用设计

- 设计要求:所有电源供应电压应来自干净的线性稳压器输出,避免使用开关电源。在 RxIN+/- 引脚附近放置 100 Ω 终端电阻。

-

详细设计步骤

- 电源供应:为模拟、数字和 LVDS 电源提供 3.3 V 电源,建议使用通用的 LDO 稳压器,并使用 EMI 滤波设备和专用去耦电容来隔离总线之间的噪声。

- 输入时序信号:提供多种输入时序信号,如 MCLK、CLPIN、BLKCLP、AGC_ONB、SHP/SAMPLE 和 SHD/HOLD 等,用于控制输入钳位、指示黑像素开始、启动白校准等操作。

- 通用逻辑输入:可选的通用逻辑输入可用于从成像板向数据处理模块传输低速数字状态信息。

- CCD 信号:CCD 信号通过 0.1 uF 电容交流耦合到 AFE 输入。

- 串行控制接口:数据处理模块通过串行控制接口与 LM98620 通信,包括 SENB、SCLK、SDI 和 SDO 等信号。

- LVDS 数据连接:串行化的 LVDS 数据对连接到 FPGA 或 LVDS 解串器芯片。

- 寄存器配置:根据需要调整和重新配置配置寄存器设置。

四、电源供应与布局建议

4.1 电源供应建议

OS 输入在芯片未供电或刚上电时,通过 PMOS 器件钳位到 VBSSAB,以防止传感器电路的瞬态损坏。通过将高电平施加到 OVPB 输入引脚并将 OVP 使能位设置为默认状态 0,可禁用保护钳位电路。

4.2 布局指南

- 使用推荐的电源配置图为设备供电。

- 在每个电源引脚旁边放置去耦电容,并靠近接地平面。

- 使用多层电路板,以方便布线并提供低电感接地平面。

- 注意过孔电感,必要时增加过孔数量和/或直径以降低电感。

- 在敏感节点下方使用接地平面“禁止区域”,以最小化寄生电容。

五、总结

LM98620 作为一款高性能的图像信号处理器,凭借其丰富的功能、卓越的性能和灵活的配置选项,为数字彩色复印机、扫描仪及其他图像处理应用提供了强大的支持。在实际应用中,我们需要根据具体需求合理选择功能模式、进行寄存器配置,并遵循电源供应和布局建议,以确保设备的稳定运行和最佳性能。希望本文能为电子工程师们在设计和应用 LM98620 时提供有价值的参考。你在使用 LM98620 过程中遇到过哪些问题呢?欢迎在评论区分享你的经验和见解。

-

接口

+关注

关注

33文章

9443浏览量

156108 -

pga

+关注

关注

1文章

113浏览量

42287 -

信号处理器

+关注

关注

1文章

262浏览量

26111 -

串行数据

+关注

关注

0文章

68浏览量

16901 -

图像信号处理

+关注

关注

0文章

20浏览量

7642

发布评论请先 登录

lm98620在正常工作模式下,出现读出数据全都是0的情况,为什么?

LM98620的offset寄存器值什么情况下起作用?

LM98620把寄存器设置好之后,AFE没有输出是怎么回事?

LM98620,pdf datasheet (10-bit

信号处理器(DSP),信号处理器(DSP)是什么意思

基于LM98503的摄像机信号处理器

AD9826原文资料数据手册PDF免费下载(成像信号处理器)

LM98620 具有 LVDS 输出的 10 位 70 MSPS 6 通道成像信号处理器

AD9923A: CCD 信号处理器,内置垂直驱动器和Precision Timing发生器 数据手册

LM98620具有LVDS输出的10位70 MSPS 6通道图像信号处理器数据表

LM98519 10位65 MSPS 6通道成像信号处理器数据表

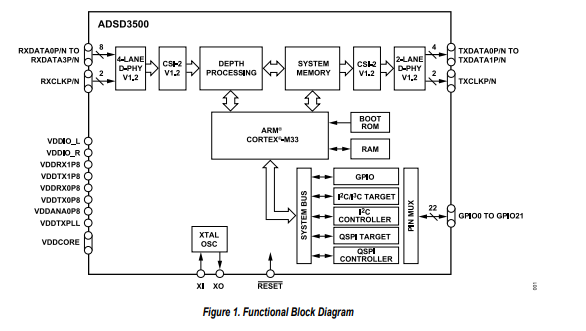

ADSD3500飞行时间深度成像信号处理器技术手册

LM98620成像信号处理器数据手册

LM98620成像信号处理器数据手册

评论