声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

LabVIEW

+关注

关注

2022文章

3689浏览量

349062 -

NI

+关注

关注

19文章

1126浏览量

105146 -

程序

+关注

关注

117文章

3849浏览量

85542 -

状态机

+关注

关注

2文章

501浏览量

29384

发布评论请先 登录

相关推荐

热点推荐

MTK Android 13状态栏耳机图标“失踪”?这个SystemUI配置修改帮你找回

在 Android ROM 定制或设备调试中,SystemUI(系统界面)的配置修改往往直接影响用户对设备的视觉感知 —— 比如状态栏图标显示 / 隐藏、通知样式、导航栏布局等。今天我们就以 MTK

条件判断法来实现状态机

。

「示例程序:」

switch(StateVal)

{

case S0:

switch(EvntID)

{

case E1:

action_S0_E1(); /*S0 状态下 E1

发表于 12-09 08:18

一个面向单片机、事件驱动的嵌入式开发平台介绍

易用,是进行线程(状态机)间同步或者通信的主要手段,也是对EventOS分布式特性和跨平台开发进行支持的唯一手段。事件支持广播发送,或者发布-订阅机制两种方式(二选一)。

2、全局事件队列,摒弃每个

发表于 12-05 06:26

睿远研究院丨IO-Link规范解读(十一):ISDU状态机与EVENT事件

上篇我们介绍了ISDU的典型编码格式和应用案例,本篇我们就来详细介绍下,ISDU的状态机,并把EVENT事件的逻辑,给大家好好解析下。 1主站ISDU状态机 如上图所示,ISDU的状态机的核心

嵌入式开发为何经常用到状态机架构

一个管脚电平跳变或者一个串口数据,让整个程序都不动的情况也让我非常纠结,如果事件一直不发生电平跳变,你要等到世界末日么?

如果应用状态机编程思想,程序只需要用全局变量记录下工作状态,就

发表于 11-25 07:08

睿远研究院丨IO-Link规范解读(八):M-Sequence Type 与消息处理状态机

丢弃,减少后端工作量。 那么今天我们就来深入研究下,消息处理模块中提到的各类M-Sequence,以及主从站的消息处理状态机! 1 M-Sequence Type 上回讲到主站发出来的MC和CKT

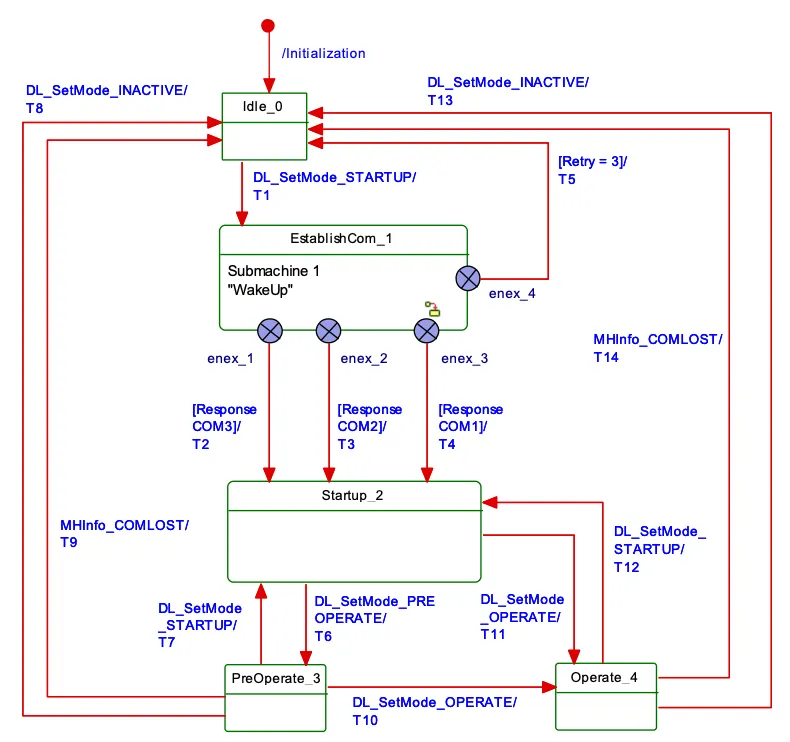

睿远研究院丨IO-Link规范解读(六):主从站状态机解析

前言 书接上文,今天我们就来好好聊聊主从站的DL-Mode状态机,还请各位童鞋前排坐好! 1主站状态机解析 主站的DL-Mode状态机有5个大状态,也是我们很熟悉的 建立通信、开始、预

蜂鸟SOC的SPI外设:如何修改SPI的时钟相位和时钟极性

:

更改状态机,使结束时间多半拍:

spi_master_rx/rx中的done信号等需要改变:

2. 我们仿真通过,并且下板测试与采样模块交互成功

发表于 10-20 09:36

JTAG标准的状态机实现

JTAG作为一项国际标准测试协议(IEEE1149.1兼容),主要用于芯片内部测试和调试。目前的主流芯片均支持JTAG协议,如DSP、FPGA、ARM、部分单片机等。标准的JTAG接口是20Pin,但JTAG实际使用的只有4根信号线,再配合电源、地。

请问如何在FX10上使用GPIF III状态机 *.h 文件?

LVCMOS 2 位 SlaveFIFO GPIF III 状态机的演示中有一个 cy_gpif_header_lvcmos.h 文件。

我想知道如何使用.h文件,只需放入.h文件放入 FX10 项目?

您有它的用户指南文档吗?

发表于 07-16 08:17

NVMe高速传输之摆脱XDMA设计之十:NVMe初始化状态机设计

1为NVMe配置初始化状态机状态转移图。各状态的说明如下:

图1NVMe初始化状态转移图

IDLE:空闲状态,复位后的初始

发表于 07-05 22:03

NVMe高速传输之摆脱XDMA设计之八:PCIe初始化状态机设计

初始化是PCIe总线正常进行数据传输的前提,图1为PCIe配置初始化状态机状态转移图。

图1 PCIe配置初始化状态机状态转移图

各

发表于 07-05 22:00

有可能在 FX3 GPIF2 中创建两个独立的状态机吗?

我想,如果我想通过 FX3 GPIF2 创建两个独立的传输流接口,我需要在 GPIF2 设计器中创建两个独立的状态机,我是否有可能在 GPIF2 设计器中创建两个独立的状态机?

发表于 05-20 06:14

如何对状态机的程序进行灵活修改

如何对状态机的程序进行灵活修改

评论