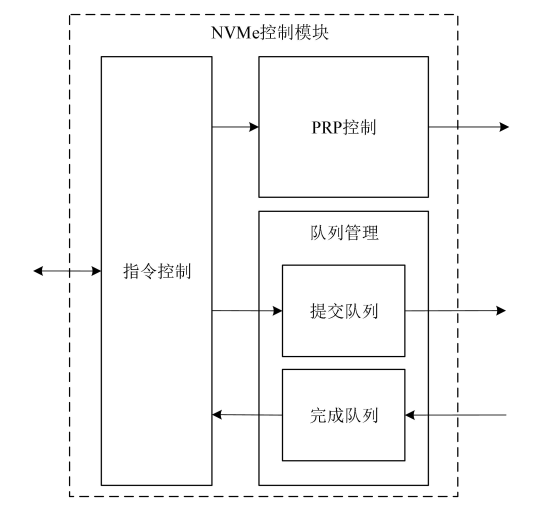

完成信息解析模块用于解析NVMe命令执行完成后返回的信息。该模块首先提取完成信息中的Status Field字段和ID号。通过检查Status Field字段,判断NVMe命令是否成功执行。若命令成功执行,则释放对应ID号的SQ中的缓存空间,以便新的NVMe提交命令使用。若命令执行失败,则将Error信号被拉高,并将该ID号反馈给队列管理模块,以便重新发送该命令。

为了提升系统传输效率,将NVMe命令执行流程中的中断步骤取消,不通过中断的方式来通知Host检查完成信息,而是利用硬件电路的并行特点,实时对完成信息进行检测。并通过添加一级寄存器来提高效率,可以不间断的接收完成信息,其工作流程为:

(1)接收128bit的完成信息,并将Status Field字段、ID字段、SQ Head Pointer字段和CQ Tail Pointer字段提取出来;

(2)判断Status Field字段的值是否为000000000000000b,若是则将done信号拉高,同时将ID字段传输至队列管理模块,否则将Error信号拉高。

审核编辑 黄宇

-

FPGA

+关注

关注

1655文章

22283浏览量

630173 -

控制器

+关注

关注

114文章

17638浏览量

190218 -

nvme

+关注

关注

0文章

287浏览量

23716

发布评论请先 登录

NVMe高速传输之摆脱XDMA设计30: NVMe 设备模型设计

NVMe高速传输之摆脱XDMA设计20: PCIe应答模块设计

NVMe高速传输之摆脱XDMA设计17:PCIe加速模块设计

NVMe高速传输之摆脱XDMA设计14: PCIe应答模块设计

NVMe高速传输之摆脱XDMA设计之十:NVMe初始化状态机设计

NVMe协议简要分析

NVMe控制器IP设计系列之接口转换模块

NVMe控制器之完成信息解析模块

NVMe控制器之完成信息解析模块

评论