概述

ADF4196频率合成器可以用来在无线接收机和发射机的上变频和下变频部分实现本振(LO),其结构专门设计用来满足基站的GSM/EDGE锁定时间要求,其快速建立功能则使ADF4196非常适合脉冲多普勒雷达应用。

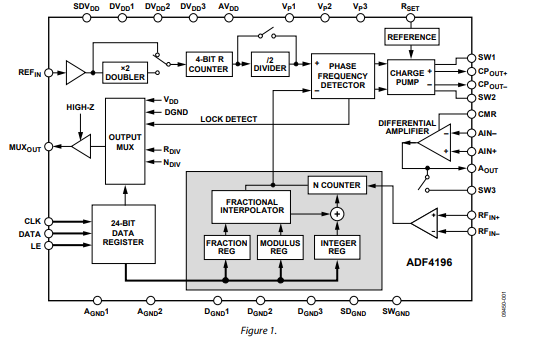

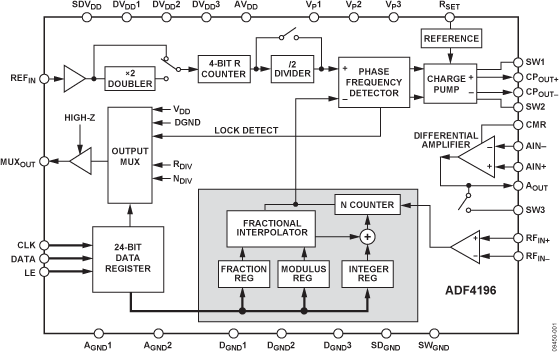

ADF4196由低噪声数字鉴频鉴相器(PFD)和精密差分电荷泵组成。还有一个差分放大器,用来将电荷泵的差分输出转换为外部电压控制振荡器(VCO)的单端电压。Σ-Δ型小数插值器与N分频器一起使用,能够实现可编程模数小数N分频。此外,4位参考(R)分频器和片内倍频器允许PFD输入端的参考信号(REFIN)频率为可选值。

如果频率合成器与外部环路滤波器和VCO一起使用,则可以实现完整的锁相环(PLL)。开关结构确保PLL能在GSM时隙保护期间内建立,而无需第二PLL及相关的隔离开关。与以前的乒乓式GSM PLL结构相比,这种结构能节省成本,降低复杂度,减小PCB面积,并减少屏蔽和特性测试工作。

数据表:*附件:ADF4196低相位噪声,快速解决6GHz锁相频率合成器技术手册.pdf

应用

- GSM/EDGE基站

- PHS基站

- 脉冲多普勒雷达

- 仪器仪表和测试设备

- 波束形成/相控阵系统

特性

- 快速建立小数N

分频PLL结构 - 单个PLL可取代乒乓式频率合成器

- 在5 μs内完成整个GSM频段上的跳频,相位建立时间低于20 µs

- 相位误差:1度rms

(4 GHz RF输出) - 数字可编程输出相位

- 数字可编程输出相位

- RF输入范围最高可达6 GHz

- 三线式串行接口

- 片内低噪声差分放大器

- 相位噪声品质因数:–216 dBc/Hz

- 利用ADIsimPLL可实现环路滤波器设计

框图

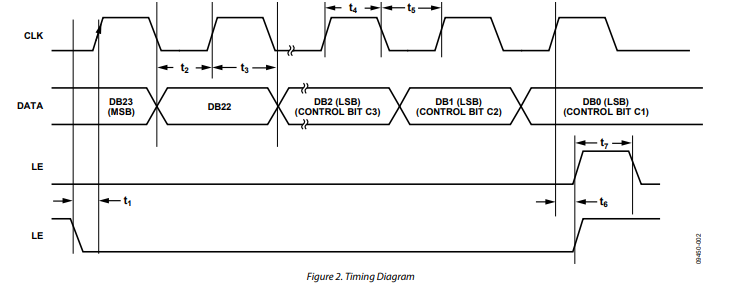

时序图

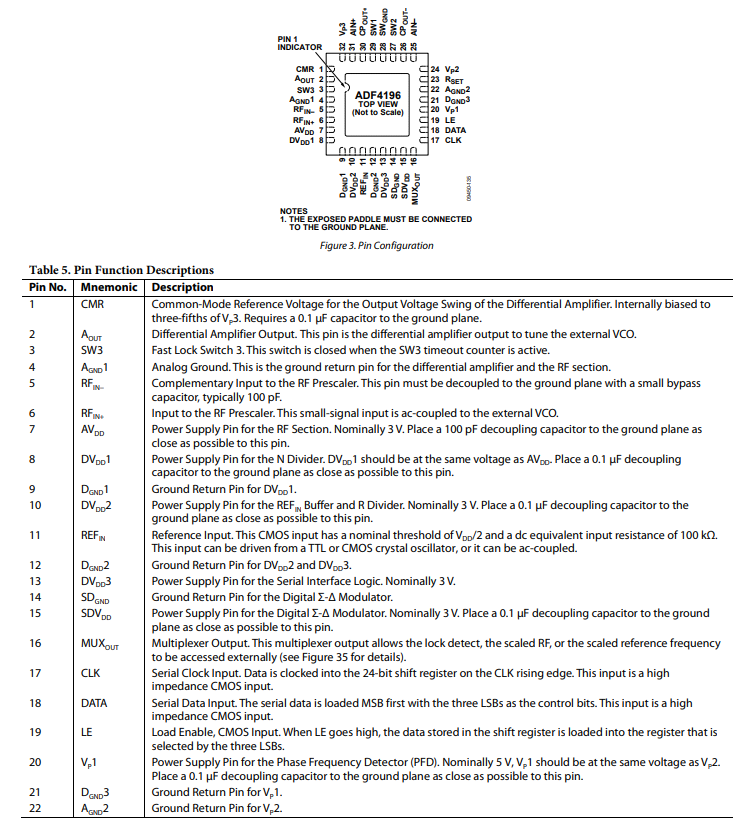

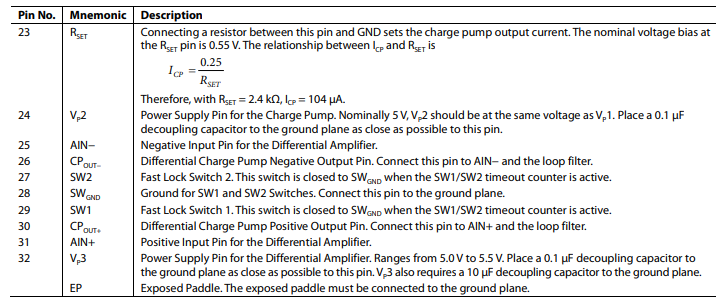

引脚配置描述

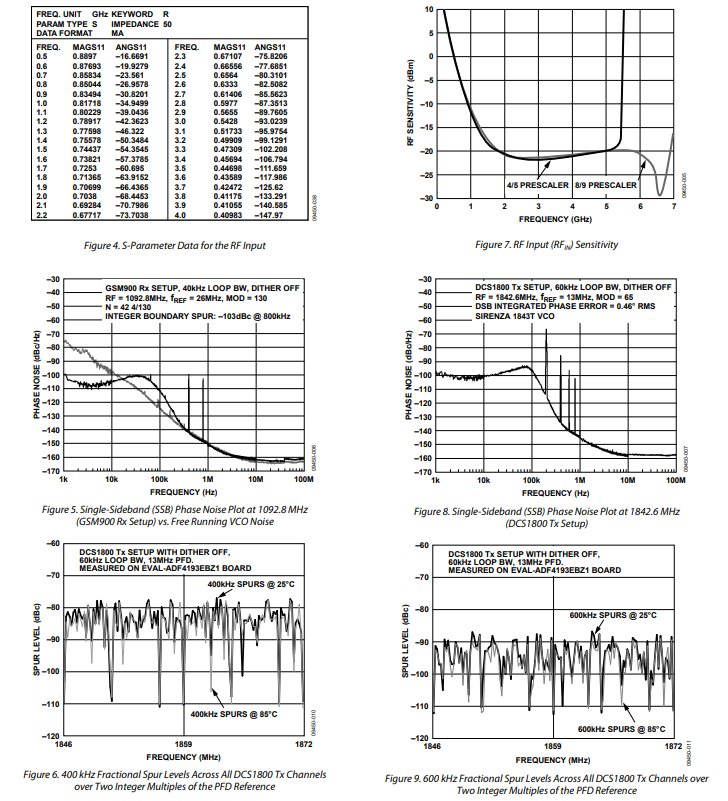

典型性能特征

总体描述

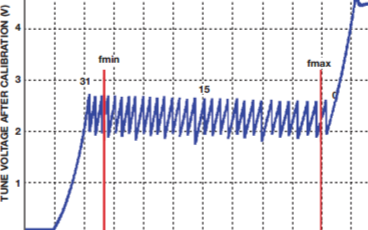

ADF4196专为满足GSM基站要求而设计,特别是针对乒乓解决方案的定时需求。它也可用于多普勒雷达应用。ADF4196基于快速锁定原理工作,使用窄环路带宽进行频率锁定,并在实现频率锁定后采用窄环路带宽。

通过增加电荷泵电流来拓宽环路带宽。为在变化的电荷泵电流下保持稳定性,ADF4196包括用于改变环路滤波器组件值的开关。

窄环路带宽可确保满足相位噪声和杂散规格要求。差分电荷泵和环路滤波器拓扑结构确保在拓宽环路带宽时实现快速锁定,并且在环路恢复到窄带宽模式以进行正常操作时,仍能保持快速锁定带来的优势。

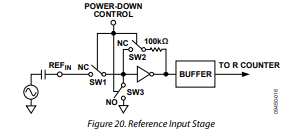

参考输入

参考输入级如图20所示。开关SW1和SW2通常闭合,开关SW3通常断开。掉电时,SW3闭合,SW1和SW2断开,以确保在掉电期间**REF_{IN}**引脚不会有负载。**REF_{IN}**的下降沿是鉴频鉴相器(PFD)正沿触发的有效沿。

R计数器和倍频器

4位R计数器可对输入参考频率进行分频,以产生PFD的参考时钟。可通过触发R计数器的翻转 - 翻转功能实现额外的二分频。使用此选项的额外优势是,PFD参考时钟的间隔比为50/50。该比率可使快速锁定定时器的最大间隔最大化,该定时器由PFD的下降沿生成,上升沿为有效沿。建议对于大于2的偶数R分频值启用此翻转 - 翻转功能。通过对**REF_{IN}**频率进行分频,可将翻转 - 翻转功能的频率提高到120MHz以上。

在4位R计数器之前,可使用一个可选倍频器,用于处理低至20MHz的**REF_{IN}**频率。通过这些可编程选项,**REF_{IN}**与PFD之间的分频比范围为0.5至30。

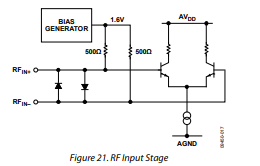

射频输入级

射频输入级如图21所示。其后接两级限幅放大器,用于生成预分频器所需的电流模式逻辑(CML)时钟电平。有两种预分频器选项:4/5和8/9。对于N分频器值大于80的情况,选择8/9预分频器。

图21. 射频输入级

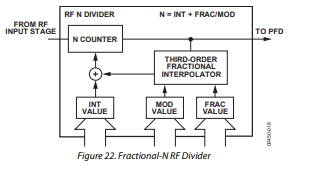

射频N分频器

射频N分频器可在锁相环(PLL)反馈路径中实现分数分频比。分频比中的整数部分和分数部分通过独立寄存器编程,如图22所示,并在“INT、FRAC和MOD关系”部分进行了说明。允许的整数分频比范围为26至511,三阶Σ-Δ调制器可在整数步长之间对分数值进行插值。

INT、FRAC和MOD关系

通过串行接口编程的INT、FRAC和MOD值,能够生成间隔为PFD参考频率分数倍的射频输出频率。N分频器值由以下公式构成,用于计算外部VCO的射频输出频率(RF_{OUT}):

其中:

- **RF_{OUT}**是外部VCO的输出频率。

- **f_{PFD}**是PFD参考频率。

选择MOD的值以获得所需的信道步长与可用参考频率的比值。然后,根据所需的输出频率编程INT和FRAC值。有关更多信息,请参见“应用信息”部分。

-

频率合成器

+关注

关注

5文章

305浏览量

33410 -

ADF4196

+关注

关注

0文章

3浏览量

5732 -

PFD

+关注

关注

0文章

22浏览量

14783

发布评论请先 登录

ADI推出新款PLL频率合成器ADF4151和ADF4196

TI推出LMX2581业界最低相位噪声的频率合成器

ADF4196 低相位噪声,快速解决6 GHz 锁相频率合成器

ADF4196低相位噪声,快速解决6GHz锁相频率合成器技术手册

ADF4196低相位噪声,快速解决6GHz锁相频率合成器技术手册

评论