概述

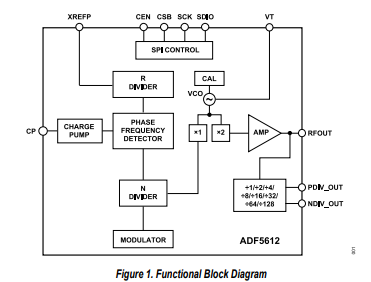

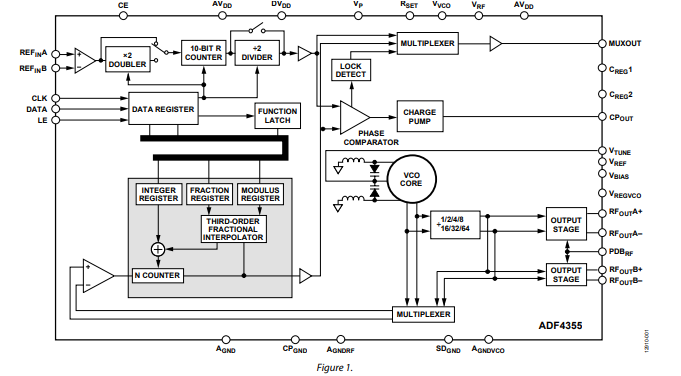

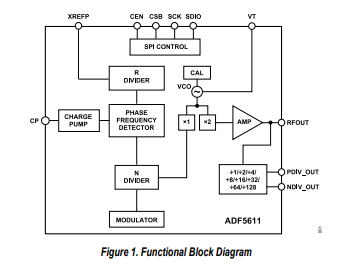

ADF5612 结合外部环路滤波器和外部基准电压源使用时,可实现小数 N 分频或整数 N 分频锁相环 (PLL) 频率合成器。宽带微波压控振荡器 (VCO) 设计允许在单个 RF 输出上实现 7300MHz 至 8500MHz 的频率操作。一系列具有差分频率输出的分频器允许在 57MHz 至 8500MHz 范围内运行。PLL 电路的模拟和数字电源范围为 3.15V 至 3.45V,VCO 电源范围在 4.75V 至 5.25V 之间。

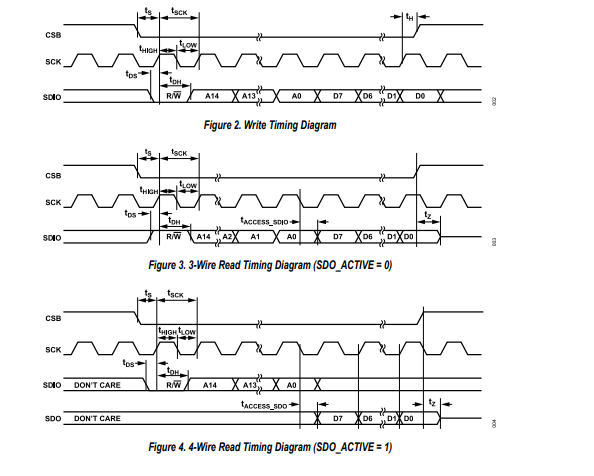

ADF5612 具有集成 VCO,基频为 3650MHz 至 7300MHz。这些频率在内部加倍并路由至 RFOUT 引脚。额外的差分输出允许将加倍的 VCO 频率除以 1、2、4、8、16、32、64 或 128,从而允许用户生成低至 57MHz 的 RF 输出频率。简单的 3 线或 4 线串行端口接口 (SPI) 可控制所有片上寄存器。为了节省电力,当不需要时可以通过 SPI 禁用此分频器模块。同样,单端输出和差分输出的输出功率都是可编程的。

集成的相位检测器和 Δ-Σ 调制器能够在高达 100MHz 的频率下工作,允许宽环路带宽和快速频率调谐,典型杂散电平为 -105dBc。

在 7.3GHz RFOUT 时,VCO 开环相位噪声在 100kHz 偏移处为 −115dBc/Hz。ADF5612 可最大限度地减少阻塞效应,并提高接收器灵敏度和发射器频谱纯度。低相位本底噪声可在变送器应用中消除对调制器和混频器本底噪声的任何影响。

数据表:*附件:ADF5612集成VCO的微波宽带频率合成器技术手册.pdf

应用

- 军事和防务

- 测试设备

- 时钟产生

- 无线基础设施

- 卫星和甚小孔径终端 (VSAT)

- 微波无线电

特性

- RFOUT 输出频率范围:7300MHz 至 8500MHz

- PDIV_OUT 和 NDIV_OUT 频率范围:57MHz 至 8500MHz

- 小数 N 频率合成器和整数 N 频率合成器模式

- 典型 PFD 杂散功率:<−105dBc

- 1kHz 至 100MHz 集成带宽下的 RMS 抖动:<40 飞秒

- 归一化带内相位本底噪声 FOM

- 整数模式:−232dBc/Hz

- 分数模式:−229dBc/Hz

- 在 −40°C 至 +105°C 范围内维持锁频(锁定后即可离开)

- 低开环 VCO 相位噪声

- 100kHz 偏移时典型值为 −115dBc/Hz(RFOUT 为 7.3GHz)

- RFOUT 功率(典型值):6dBm

- 可编程的 1、2、4、8、16、32、64 或 128 分频输出

- 可编程输出功率水平

- 典型功耗:1 瓦

- 48 端子、7 mm × 7 mm LGA 封装:49 mm^2^

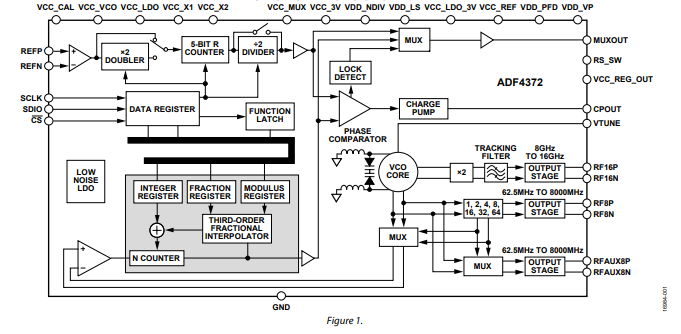

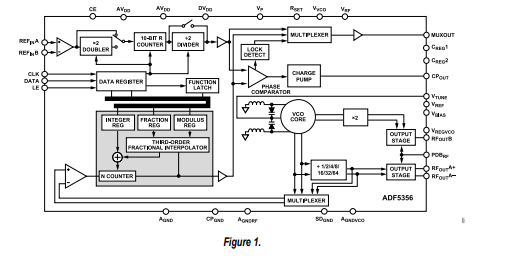

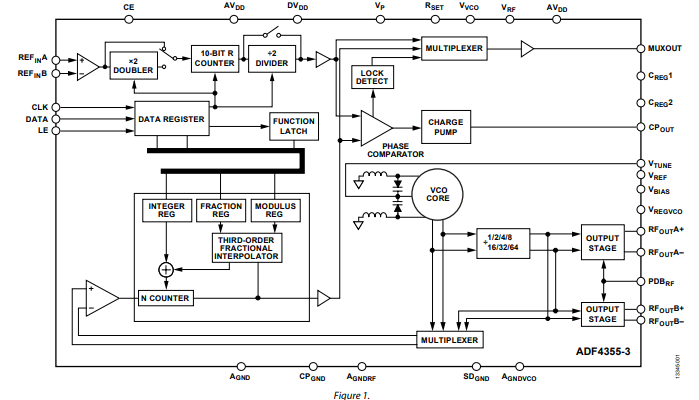

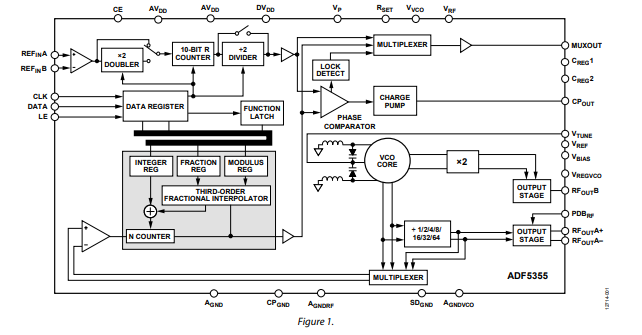

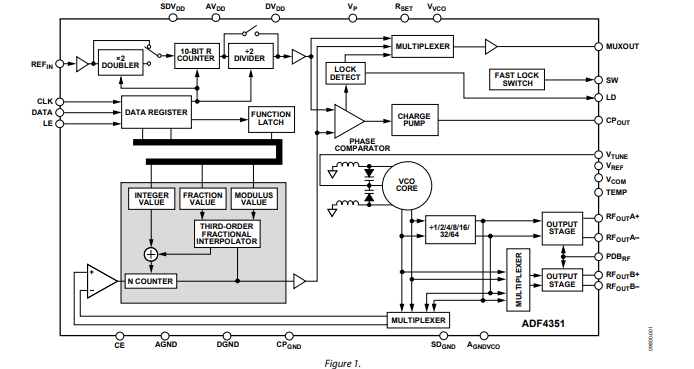

框图

SPI时序图

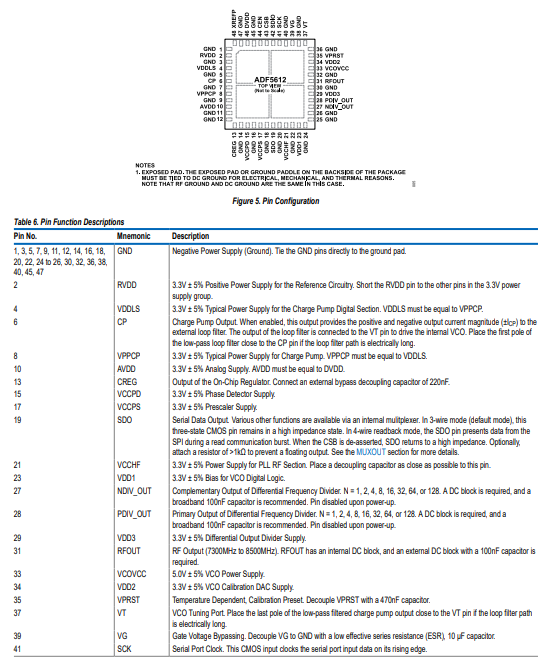

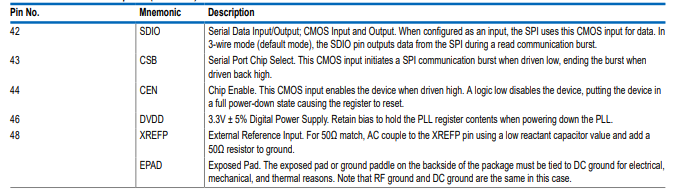

引脚配置描述

典型性能特征

反馈分频器(N)

反馈分频器在锁相环(PLL)反馈路径中提供分频比。该分频比由一个20位的N_INT(寄存器0x010至寄存器0x012)、一个25位的FRACWORD1(寄存器0x012至寄存器0x015)、一个24位的FRACWORD2(寄存器0x017至寄存器0x019)和一个24位的MOD2WORD(寄存器0x01A至寄存器0x01C)组成,其中bit字段[5:0] 。该分频器与固定模数MOD1WORD(2²⁵)共同构成。

参考输入

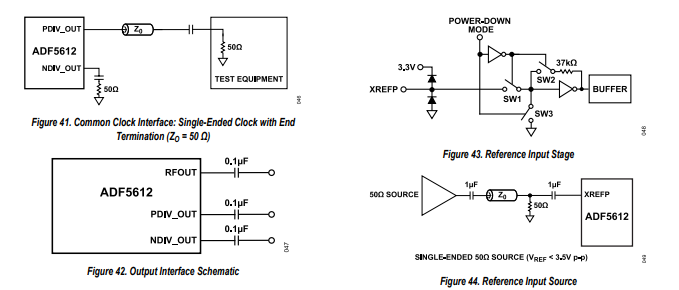

锁相环的参考信号通过XREF输入,它作为单端输入工作。这个高阻抗输入是自偏置的,需要交流耦合(参考图43,获取参考输入级的简化原理图)。通过配置PD_RDIV位(寄存器0x027,bit 6)为0,可以启用该参考输入。在此配置中,SW1和SW2闭合,SW3打开。

输入信号的转换速率对性能有显著影响。该器件在信号峰峰值低至0.4V时仍可工作。然而,为了实现ADF5612的最佳带内相位噪声性能,需应用连续正弦波信号或具有至少500V/μs转换速率的方波信号。实现这种正弦波转换速率,在低频时需要高幅度信号,在10MHz时可能需要方波信号。建议使用具有高转换速率的高性能方波信号作为参考输入信号,以实现最佳性能。有关参考输入信号要求和接口的信息,请参见图44。

参考分频器

参考路径R分频器R_DIV(分别为寄存器0x01F,bit[7:0] )基于一个14位计数器。该分频器用于降低在鉴频鉴相器(PFD)处看到的频率,其分频比(R)可以设置为1到16,383之间的任意整数。使用R_DIV位可直接设置R分频比。

鉴频鉴相器(PFD)

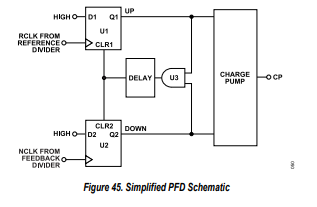

PFD与电荷泵配合,产生与反馈分频器或参考倍频器输出之间的相位差成比例的源电流和灌电流脉冲。因此,需要源电流和灌电流脉冲来锁定环路。PFD的一个输入包含一个固定延迟元件,用于设置反冲脉冲的宽度。该延迟元件可确保PFD传输函数中不存在死区,从而在该器件上提供一致的参考杂散电平。由于压控振荡器(VCO)的正调谐特性,将鉴相器极性设置为正。有关PFD的简化原理图,请参见图45。

掉电模式 :(图中右上角相关电路未详细展开说明其原理,仅呈现电路示意 )

-

滤波器

+关注

关注

162文章

8350浏览量

184724 -

频率合成器

+关注

关注

5文章

305浏览量

33410 -

pll

+关注

关注

6文章

976浏览量

137568

发布评论请先 登录

CDF5356: 微波宽带合成器和集成 VCO 数据表 ADI

ADF4355集成VCO的微波宽带频率合成器技术手册

ADF5612集成VCO的微波宽带频率合成器技术手册

ADF5612集成VCO的微波宽带频率合成器技术手册

评论