1.RDMA 传输系统架构设计目的

随着数据中心对于网络带宽和延迟的要求日益增长,传统的 TCP/IP 网络已无法满足性能要求, RDMA 网络则凭借其高带宽、低延时的特性脱颖而出错误!未找到引用源。相较于传统 TCP/IP 协议, RDMA 具有零拷贝、不需要 CPU 接入、消息基于事务等特点。

该系统架构主要解决适合于FPGA端的RDMA传输。它支持FPGA之间,FPGA与PC之间高速通信。只需一根光纤(当然,PC端需要转接卡,将光纤转入PC端,例如100G的CX455A-ECAT 100Gbe网卡 就可以)。它注重通用性强,性能优越,非私有化协议设计,以便用户后续升级或更换IP。

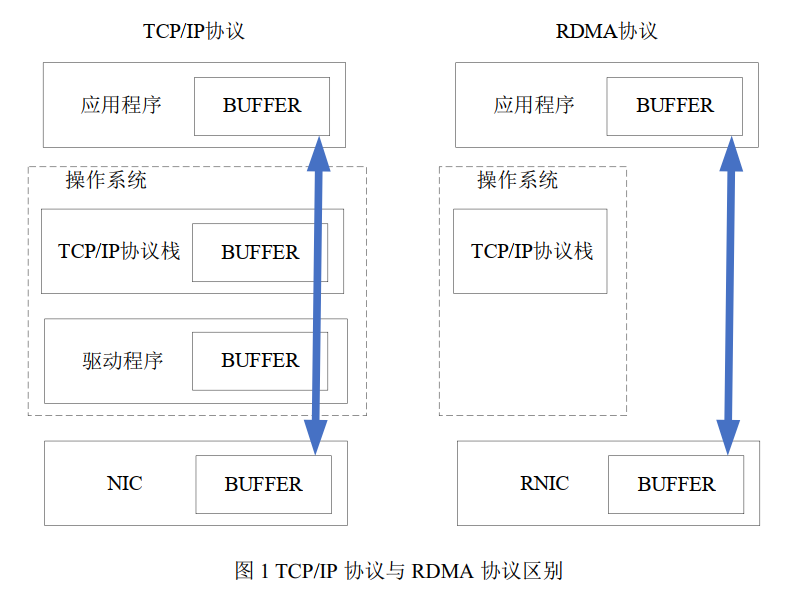

2. RDMA 协议与传统 TCP/IP 协议在通信过程中的区别

如图 1 所示,左侧部分为传统 TCP/IP 协议的通信过程,首先使操作系统进入内核态,而后传输的数据通过 BUFFER 拷贝进 TCP/IP 协议栈进行组包处理,而后通过网卡(NIC)驱动下发到网卡内的 BUFFER。右侧部分则为 RDMA 协议的通信过程,其将 RDMA 协议部署在融合以太网卡(RNIC)上,在对数据包的组装和拆解过程中,不需要 CPU 及操作系统介入干预,也不需要进行内存拷贝操作。当发送数据包时,直接由应用程序通知网卡要发送的数据在内存中的起始地址及数据长度,而后 RNIC 则读取其已经在内存中注册好的区域数据并依照协议规范进行数据包的组装及传输。

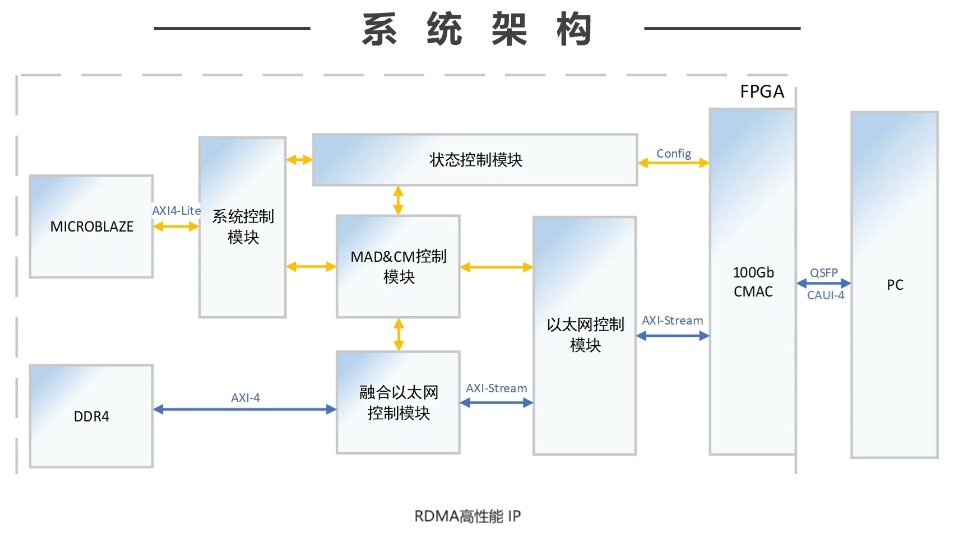

3.系统架构如图2:

图2 系统架构图

对IP的简单控制由Microblaze完成,DDR负责读写等数据缓存。该架构也可以换成zynq的arm控制,便于后续NVMe oF开发。

视频可以搜B站 用户名: 专注与守望

4测试

在xilinx开发平台测试,网卡支持100G,选用的是CX455A-ECAT 100Gbe。该IP支持 RoCE V2。实测数据:

SEND71Gbps

READ91 Gbps(PC端给FPGA发包,受PC性能限制多一点)

WRITE 96 Gbps

审核编辑 黄宇

-

FPGA

+关注

关注

1655文章

22288浏览量

630335 -

内存

+关注

关注

9文章

3173浏览量

76118 -

传输系统

+关注

关注

0文章

164浏览量

38010 -

RDMA

+关注

关注

0文章

85浏览量

9558

发布评论请先 登录

基于DSP与FPGA异构架构的高性能伺服控制系统设计

全球前四!京东云云海AI存储跻身IO500高性能存储榜单

RDMA设计6:IP架构2

RDMA设计5:RoCE V2 IP架构

RDMA设计4:技术需求分析2

RDMA设计3:技术需求分析1

RDMA设计2:开发必要性之性能简介

RDMA设计1:开发必要性1之设计考虑

RDMA over RoCE V2设计1:通用,稳定及高性能!

知合计算:RISC-V架构创新,阿基米德系列剑指高性能计算

RDMA over RoCE V2设计1:通用,稳定及高性能!

SL3065:高性能40V同步降压DC/DC控制器,替代RT7272B

RDMA简介1之RDMA开发必要性

一文详解以太网RDMA技术

高性能 RDMA 传输系统:通用性及高性能架构考虑

高性能 RDMA 传输系统:通用性及高性能架构考虑

评论