概述

AD9546 采用数字化时钟技术,可在系统中高效传输和分配时钟信号。数字化时钟具有设计灵活性,且可使用可扩展的时钟传输系统,并具有良好的相位(时间)对齐控制。这些特性使 AD9546 成为必须满足 ITU-T G.8273.2 D 类的 IEEE^®^ 1588^™^ 边界时钟的同步要求的网络设备设计的首选。数字时钟还与要求将频率和相位精确传输到多个使用端点的应用有关(例如,将同步系统参考 (SYSREF) 时钟分配到 ADC 通道阵列)。

AD9546 支持现有和新兴的国际电信联盟 (ITU) 标准,通过服务提供商分组网络,可交付频率、相位和时刻,这些分组网络包括 ITU-G.8262、ITU-T G.812、ITU-T G.813、ITU-T G.823、ITU-T G.824、ITU-T G.825 和ITU-T G.8273.2。

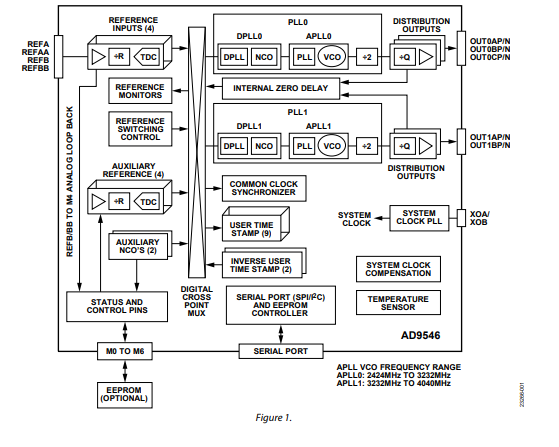

将 AD9546 的 10 个时钟输出同步为多达八个输入基准电压源中的任意一个。数字锁相环 (DPLL) 减少了与外部基准电压源相关的时序抖动,而模拟锁相环 (APLL) 提供了具有低抖动输出时钟的频率转换。数字控制的环路和保持电路即使在所有参考输入失败时仍可持续产生低抖动输出信号。

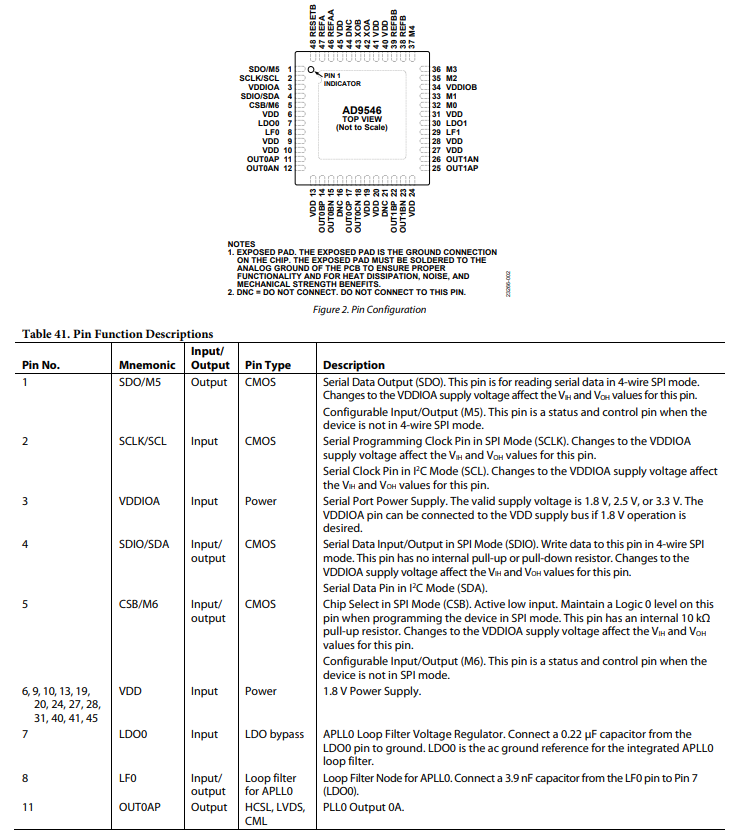

AD9546 提供 48 引脚 LFCSP (7 mm × 7 mm) 封装,可在 −40°C 至 +85°C 的温度范围内工作。

在整个数据手册中,当仅涉及多功能引脚名称的单个功能时(例如,针对SDO/M5 的 M5),可参考该功能。

数据表:*附件:AD9546双DPLL数字时钟同步器技术手册.pdf

应用

- 5G 时序传输高精度同步

- 全球定位系统 (GPS)、精确时间协议 PTP (IEEE 1588) 和同步以太网 (SyncE) 抖动滤除和同步

- 光传送网络 (OTN)、同步数字体系 (SDH) 以及宏基站和小蜂窝基站。小型基站时钟(基带和射频)

- Stratum 2、Stratum 3e 和 Stratum 3 保持、去除信号抖动和相位瞬态控制

- JESD204B 支持模数转换器 (ADC) 和数模转换器 (DAC) 时钟

- 运营商级以太网

特性

- 数字时钟传输子系统

- 9 个独立的 UTS 块(时间戳出口)

- 2 个独立的 IUTS 块(时间戳入口)

- 双 DPLL 可同步 1 Hz 到 750 MHz 物理层时钟,可在提供频率转换的同时去除噪声基准电压源的信号抖动

- 符合 ITU-T G.8262 和 Telcordia GR-253 标准

- 支持 Telcordia GR-1244、ITU-T G.812、ITU-T G.813、ITU-T G.823、ITU-T G.824、ITU-T G.825 和 ITU-T G.8273.2

- 针对低至 50 ppb (5 × 10

−8) 的频率偏移,可进行持续频率监控和基准电压源验证 - 两个 DPLL 都配有带有 24 位可编程模块的 24 位小数分频器

- 可编程数字环路滤波器带宽:0.0001 Hz 至 1850 Hz

- 两个独立的可编程辅助 NCO(1 Hz 至 65,535 Hz,分辨率 < 1.37 pHz),适合 PTP 应用中的 IEEE-1588 第 2 版伺服反馈

- 自动和手动保持和基准电压源切换,实现零延迟、无中断或相位增建

- 基于可编程优先级的基准电压源切换,支持手动、自动可逆和自动不可逆模式

- 5 对时钟输出引脚,每对都可用作差分 LVDS/HCSL/CML 或用作 2 个单端输出(1 Hz 至 500 MHz)

- 2 个差分或 8 个单端输入基准电压源

- 交叉点多路复用器将参考输入与 PLL 互连

- 支持嵌入式(模块化)输入/输出时钟信号

- 快速 DPLL 锁定模式

- 提供内部功能,可兼具晶体谐振器或晶体振荡器的低相位噪声特点,以及 TCXO 或 OCXO 的频率稳定性和精度

- 针对自主初始化提供外部 EEPROM 支持

- 1.8 V 单电源供电,带有内部调节功能

- 内置温度监视器/警报和温度补偿,可增强零延迟性能

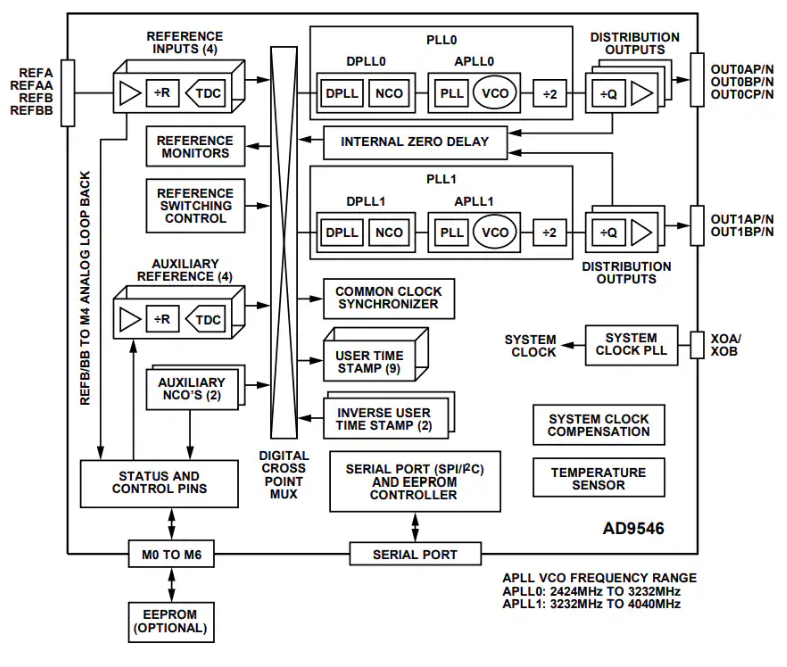

框图

引脚配置描述

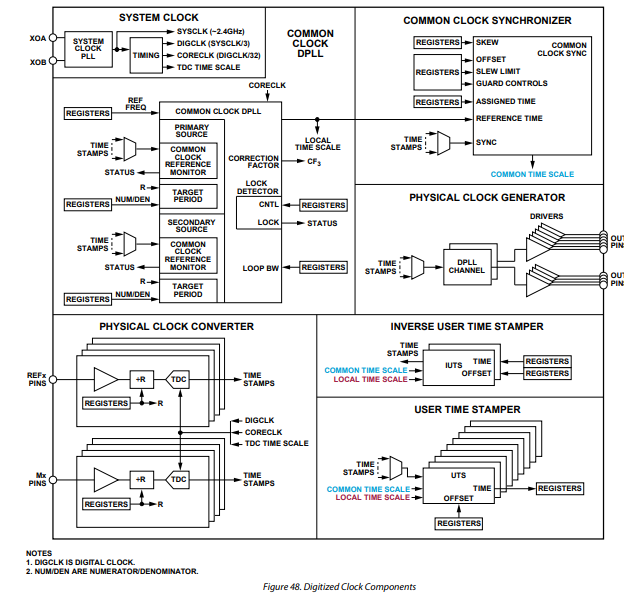

数字化时钟技术可实现精确的定时传输(频率和相位),在空间上分离的设备之间通过数字时间码进行同步(假设所有设备都能访问公共参考时钟信号)。

数字化时钟系统由多个定时节点组成,每个节点依赖于共享的外部时基(公共时钟参考)。由于每个节点共享相同的公共时钟参考,且节点增量以相同速率变化,因此所有节点都具有相同的时间尺度。尽管所有节点都处于同一尺度,但并不能保证它们共享同一时刻。数字化时钟依赖于用户在每个节点设置的同步信号,最终使所有节点实现时间对齐。数字化时钟的一个独特特性是能够通过数字总线在节点之间交换数字时间码,这意味着可以向一个或多个数字总线(时钟聚合)发送多个时钟,以路由多个模拟时钟信号来构建系统。AD9546包含实现数字化时钟节点所需的所有构建模块。

图48展示了AD9546中实现的完整数字化时钟节点的各个组件。这些数字化时钟组件包括:

- 系统时钟PLL,用于生成系统时钟频率,以实现内部定时功能(详见“系统时钟PLL”部分)

- 公共时钟DPLL,用于与参考时基(公共时钟参考)进行锁相,并维持本地时间尺度

- 物理时钟转换器,用于将系统时钟的时间戳转换为物理时钟

- 物理时钟发生器,用于将从公共时间尺度导出的时间戳转换为物理时钟输出信号

- ACCS,通过为本地时间尺度分配时刻来创建公共时间尺度

- UTS,用于将内部时间戳转换为基于公共时间尺度的时间码,并将这些时间码提供给用户用于外部使用

- IUTS,用于将用户提供的基于公共时间尺度的一系列时间码转换为内部时间戳

图48展示了多种时间戳源。某些数字化时钟组件需要能够连接到任意一个时间戳源,这就是为什么这些组件在其输入处包含时间戳选择多路复用器。

系统时钟PLL组件

系统时钟PLL通常使用外部晶体谐振器作为频率源,这往往能提供最佳的整体相位噪声性能。系统时钟PLL从外部频率源(约2.4GHz)合成高频内部系统时钟信号,为设备提供基本的内部定时。设备使用系统时钟来生成时间戳(详见“时间数字转换器(TDC)”部分)。

请注意,内部系统时钟信号是公共时钟DPLL组件用于生成本地时间尺度的两个频率源之一。

公共时钟DPLL组件

公共时钟DPLL的作用是生成本地时间尺度。公共时钟DPLL使用系统时钟进行内部定时,但其相位锁定到参考时基,即公共时钟参考。公共时钟DPLL的输出是本地时间尺度,它累积了公共时钟参考的周期,并为数字化时钟组件提供内部时间感知。

公共时钟DPLL固有的闭环架构意味着其运行会产生误差,校正因子3(CF3)有效地补偿了系统时钟的波动。请注意,CF3信号可用于AD9546的系统时钟补偿功能模块(详见“补偿方法3”部分)。

物理时钟转换器

物理时钟转换器有一个输入,用于接收外部时钟信号,提供可选的整数频率分频功能,并将上升沿时钟转换为数字时间戳。然后,这些时间戳可供需要时间戳源的数字化时钟组件使用。

物理时钟发生器

物理时钟发生器利用AD9546的DPLL通道和输出分配驱动器,从时间戳生成模拟时钟输出信号。在数字化时钟应用中,时间戳源自公共时间尺度。由于DPLL可以从这些时间戳中获取其参考输入,因此物理时钟发生器的输出由模拟时钟信号组成。

-

时钟

+关注

关注

11文章

1953浏览量

134552 -

DPLL

+关注

关注

1文章

34浏览量

14332 -

数字化

+关注

关注

8文章

10318浏览量

66555

发布评论请先 登录

DAY-1000数字音频同步器

AD9546: Dual DPLL Digitized Clock Synchronizer Data Sheet

AD9543:四路输入、10路输出、双DPLL/IEEE 1588同步器和抖动清除器

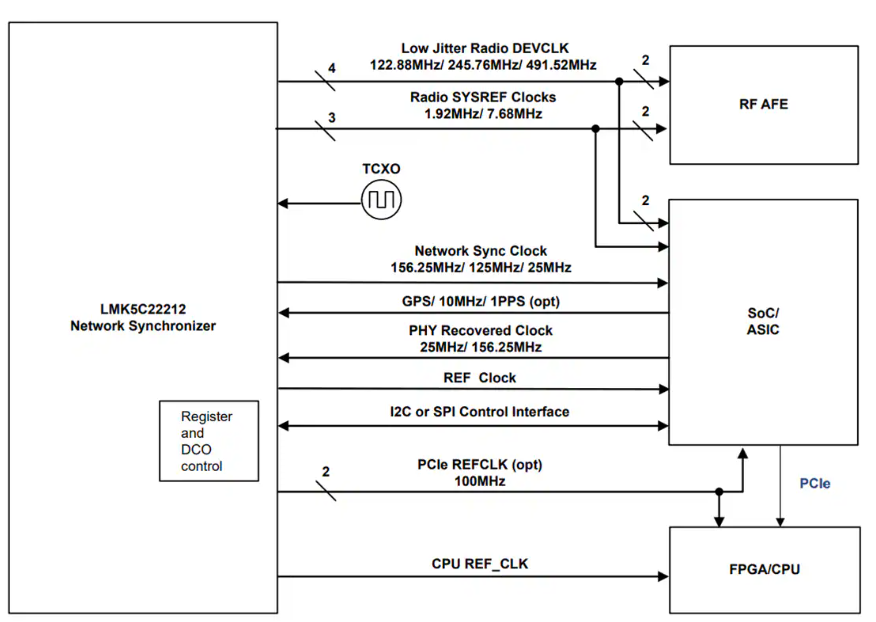

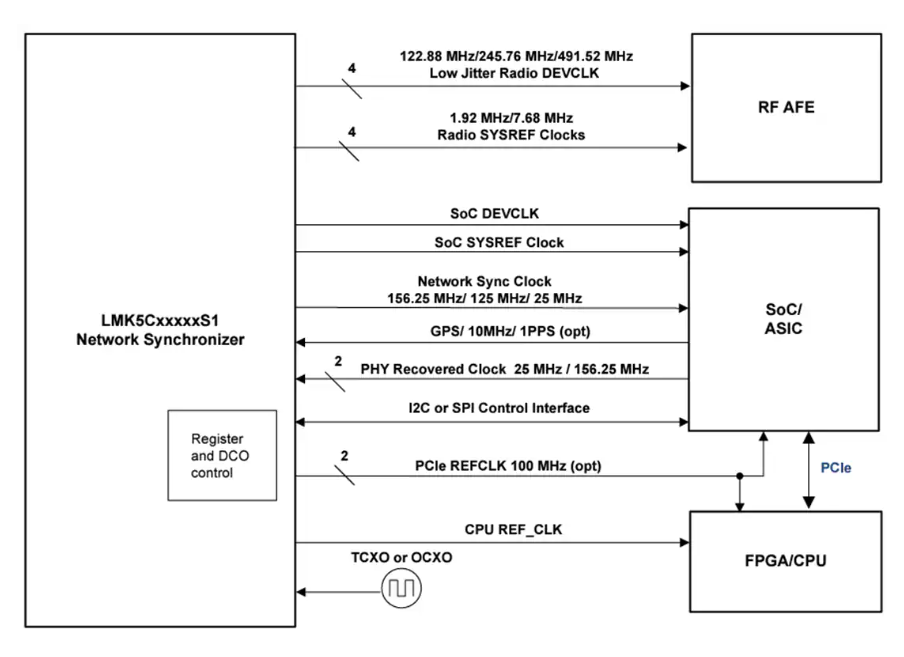

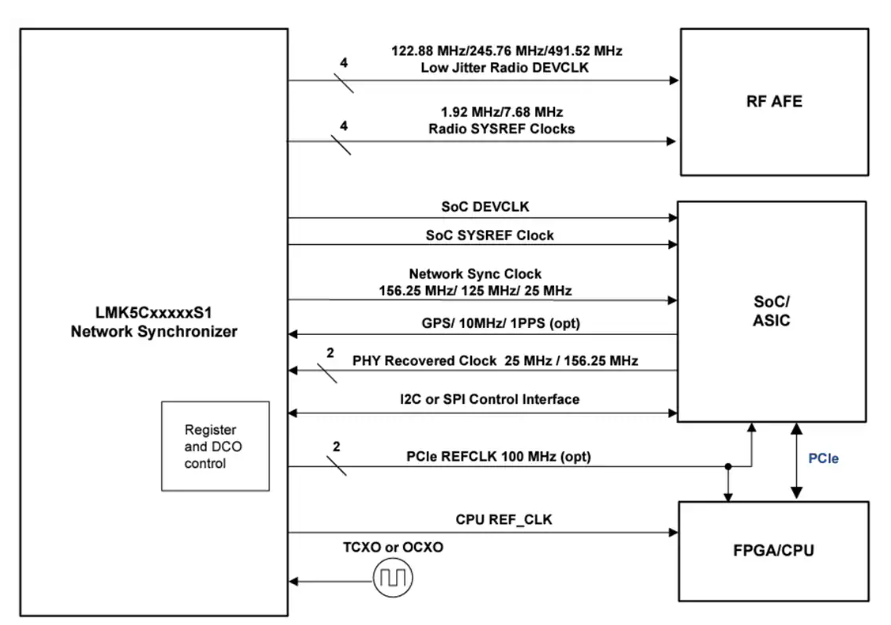

Texas Instruments LMK5C22212AS1网络同步器数据手册

Texas Instruments LMK5C33216AS1网络同步器数据手册

Texas Instruments LMK5C33414AS1网络同步器数据手册

AD9546双DPLL数字时钟同步器技术手册

AD9546双DPLL数字时钟同步器技术手册

评论