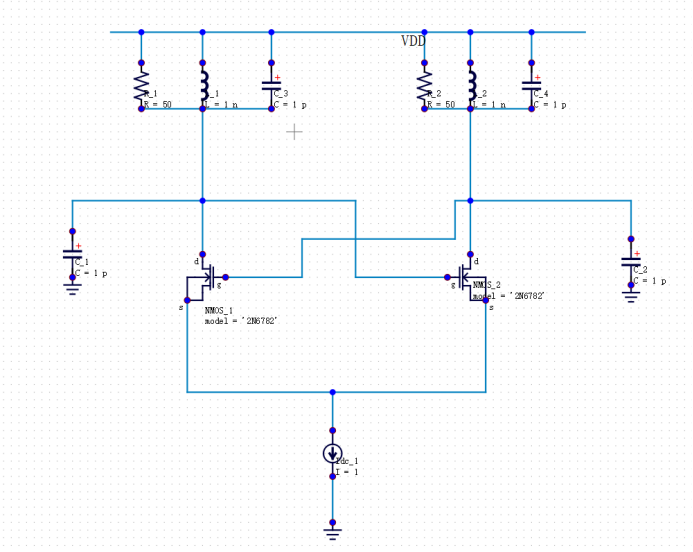

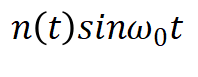

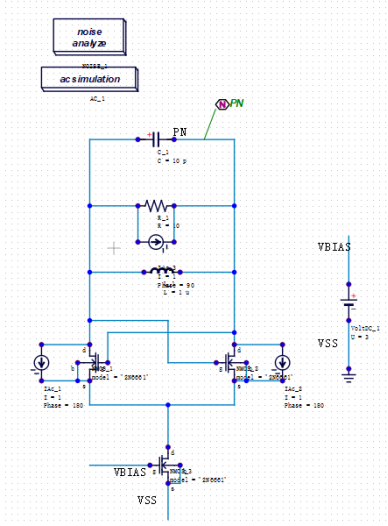

电路示例图

使用巨霖PowerExpert搭建一个交叉耦合震荡器结构示意图,其中电感两侧的电阻和电容作为电感的等效模型,并不真实存在。原理是LC tank并联一个等效负电阻,实现持续震荡。

相位噪声分析

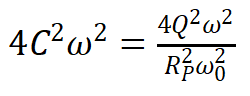

上述LC震荡器的相位噪声共有三个来源:电感(等效电阻Rp),MOS管,尾电流源,现在分析每一部分对总相位噪声的贡献。

理想LC震荡器相位噪声分析

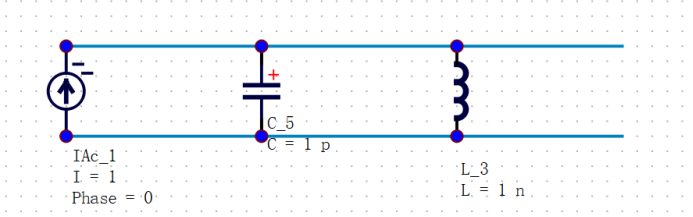

搭建一个理想LC震荡器:

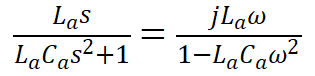

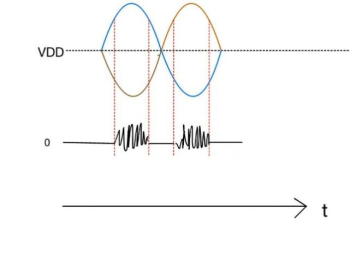

左侧的电流源代表电感的噪声模型,假设电感值为La,电容值为Ca,为了分析相位噪声,假设等效噪声源 是白噪声。上述电路阻抗可以表示为

是白噪声。上述电路阻抗可以表示为

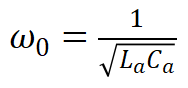

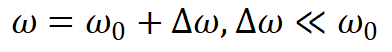

我们关心在震荡频率 附近频率的相位噪声,令

附近频率的相位噪声,令

,电路阻抗为

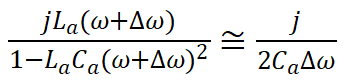

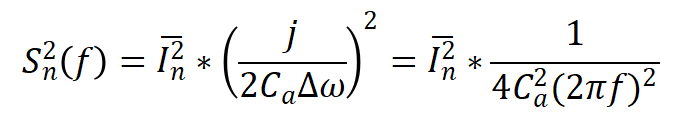

。由此可以得到输出噪声功率谱如下:

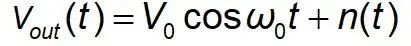

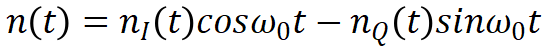

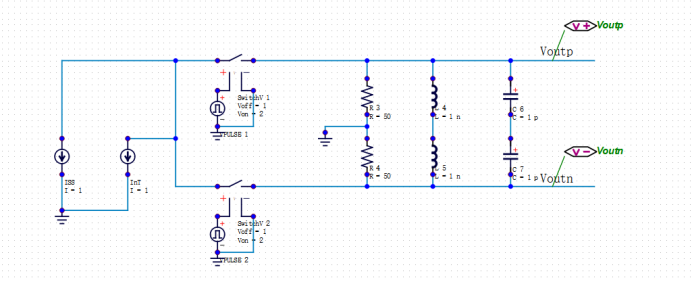

假设输出电压等于 ,n(t)是输出电压的震荡频率附近的噪声分量,其噪声功率谱如上式所示,接下来分析输出电压的噪声分量是如何影响到其相位的:n(t)作为一个带通函数,可以被表示为

,n(t)是输出电压的震荡频率附近的噪声分量,其噪声功率谱如上式所示,接下来分析输出电压的噪声分量是如何影响到其相位的:n(t)作为一个带通函数,可以被表示为 ,其中的

,其中的 和

和 分别表示n(t)幅度和相位的两个正交分量。所以上式可以改写为:

分别表示n(t)幅度和相位的两个正交分量。所以上式可以改写为:

所以输出电压 的频率分量为

的频率分量为

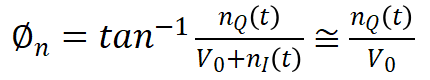

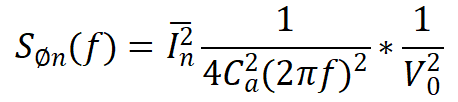

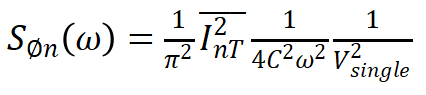

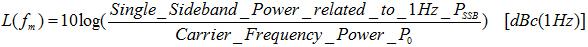

,这个量也代表了输出电压的相位噪声。由此可见,输出电压的相位噪声功率谱可以表示为:

可以注意到,在上面的等式中, 变为了

变为了 ,这是因为噪声分量n(t)转换为

,这是因为噪声分量n(t)转换为 时仅保留了相位。上面推导了输入端噪声是如何转换为输出相位噪声的,而输出相位噪声等式中代表输入噪声的

时仅保留了相位。上面推导了输入端噪声是如何转换为输出相位噪声的,而输出相位噪声等式中代表输入噪声的 被当作了白噪声处理,而在实际电路中两个MOS对管循环开启和关闭,产生的并不是白噪声,所以不能简单带入上式。

被当作了白噪声处理,而在实际电路中两个MOS对管循环开启和关闭,产生的并不是白噪声,所以不能简单带入上式。

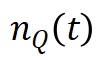

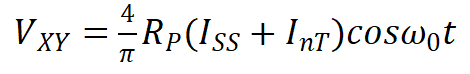

MOS管和电阻Rp对输出相位噪声贡献

输入MOS对管轮流开启,但它们仅在一段时间对输出相位噪声有贡献,这是因为它们的交叉耦合结构等效于“负电阻”,这导致输出电压的摆幅超过VDD,进而导致MOS管在关闭和输出电压最值附近都不会贡献相位噪声,因为等效噪声电流分别为0和被尾电流拉至更低的电位。具体波形如下所示:

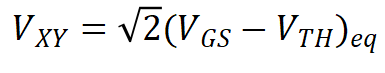

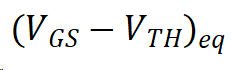

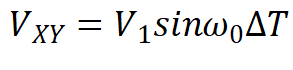

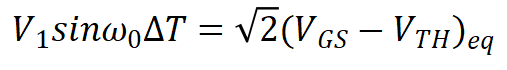

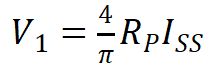

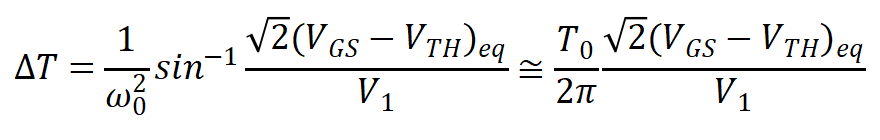

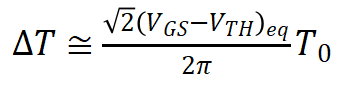

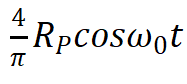

首先需要确定两个MOS管都开启的时间 ,假设输入差分电压是

,假设输入差分电压是 ,当

,当

(其中

代表当 时的过驱动电压)时,一个MOS管会关闭,其中

时的过驱动电压)时,一个MOS管会关闭,其中

,所以可以得到以下等式:

其中 是

是 周期T的角频率,

周期T的角频率,

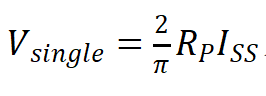

,Rp是电感L的等效电阻,Iss是尾电流值,因此可以求出:

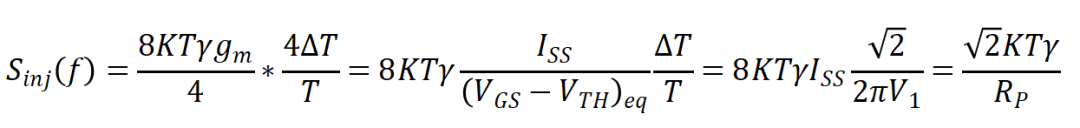

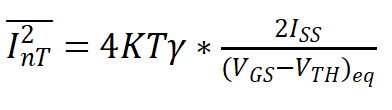

两个输入MOS管的每个周期总计会有 的时间产生相位噪声,MOS管的输入电流热噪声为

的时间产生相位噪声,MOS管的输入电流热噪声为

,其对于整体输出噪声的贡献可以看作

。再引入

可以得出输出噪声频谱为:

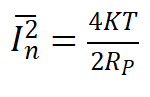

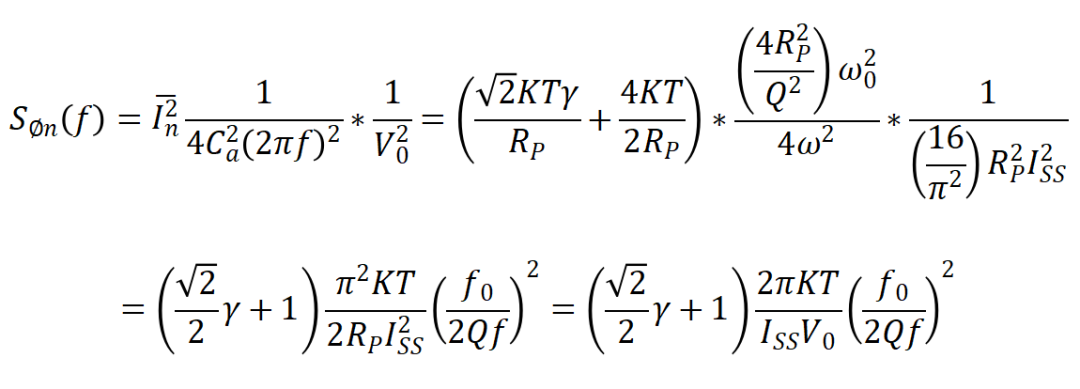

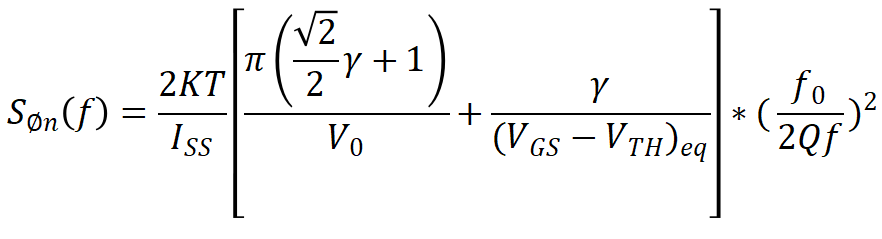

再加入两个等效电阻引入的噪声频谱 ,将两个噪声谱转换为输出相位噪声频谱:

,将两个噪声谱转换为输出相位噪声频谱:

从上式可以直观看出相位噪声和尾电流源大小(功耗)的反比关系。

MOS管和电阻对输出相位噪声贡献

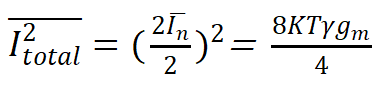

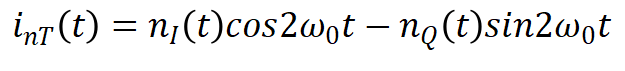

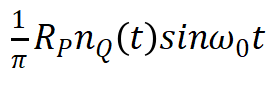

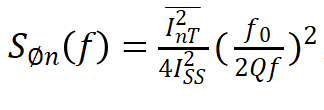

为了研究尾电流源对于相位噪声的贡献,先忽略MOS对管的噪声,上述LC tank的差分输出电压可以表示为

, 为尾电流源的等效噪声模型,传递到输出的噪声转化为相位噪声时仅计算代表相位的正交分量

为尾电流源的等效噪声模型,传递到输出的噪声转化为相位噪声时仅计算代表相位的正交分量 。首先我们需要计算尾电流源的等效输入噪声,将输入MOS对管等效为两个开关,等效电路如下图所示:

。首先我们需要计算尾电流源的等效输入噪声,将输入MOS对管等效为两个开关,等效电路如下图所示:

等效的开关相当于一个乘法器,将高低电平分别为1和0的方波信号与尾电流源相乘,等效于给尾电流源施加一个大小为 的增益,并且添加了一个频域上的分量,最终变为输出电压。注意到上述电路组成了一个带通滤波器,该模型仅考虑二次谐波频率下的输出相位噪声。因为在

的增益,并且添加了一个频域上的分量,最终变为输出电压。注意到上述电路组成了一个带通滤波器,该模型仅考虑二次谐波频率下的输出相位噪声。因为在 频率下,输出电压的波形在VDD附近斜率最大,此时

频率下,输出电压的波形在VDD附近斜率最大,此时 会产生共模噪声,在差模输出时相互抵消,在峰值附近,由于输出电压斜率约为0,故

会产生共模噪声,在差模输出时相互抵消,在峰值附近,由于输出电压斜率约为0,故 不产生输出噪声,而在更高频率下产生的输出噪声过小忽略不计。在

不产生输出噪声,而在更高频率下产生的输出噪声过小忽略不计。在 频率下,输出噪声表达式为

频率下,输出噪声表达式为

,再乘上“增益+相移” ,分解出的正交相位噪声分量为

,分解出的正交相位噪声分量为

,单边的相位噪声等于

,由于单边电压摆幅

,

,所以可以得到

,

。该电路由MOS输入对管、电感等效电阻和尾电流源的热噪声引起的总相位噪声为:

由上式可以看出,由热噪声引起的总相位噪声与 成正比。

成正比。

尾电流源贡献的1/f噪声一般情况下仅会调制输出信号的幅度,所以在理想情况下不会贡献相位噪声,但在MOS管寄生电容存在非线性特性或引起共模电压变化时,1/f噪声也会对相位噪声产生影响,贡献的相位噪声与 成正比,篇幅问题不再推导。

成正比,篇幅问题不再推导。

仿真验证

使用巨霖PowerExpert搭建如下等效LC Tank电路图:

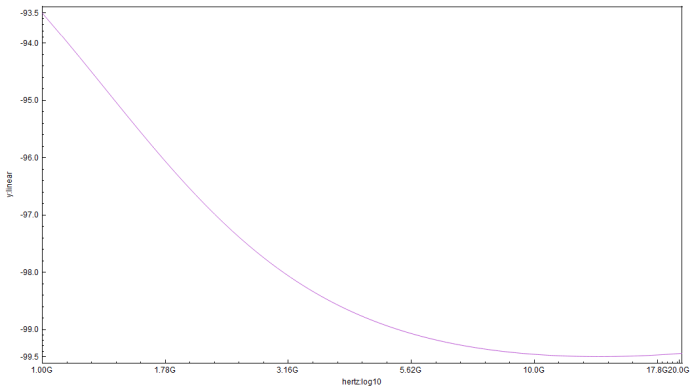

仿真结果如下:

可以看到,上图中起始约-30dB斜率的部分由1/f噪声贡献,中间-20dB斜率部分由电路中的热噪声贡献,最终在高频下逐渐衰减至0,符合理论推导。

欢迎从官网申请试用我们的软件,过程中的任何疑问可联系support技术人员,期待与您的交流!

-

MOS管

+关注

关注

110文章

2752浏览量

74857 -

电感

+关注

关注

54文章

6239浏览量

105936 -

相位噪声

+关注

关注

2文章

190浏览量

23633 -

震荡器

+关注

关注

1文章

14浏览量

8625

原文标题:LC震荡器相位噪声的分析与仿真

文章出处:【微信号:巨霖,微信公众号:巨霖】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

LC震荡器相位噪声的分析与仿真

LC震荡器相位噪声的分析与仿真

评论