“本文探讨了不同地平面情况下的电容耦合及电感耦合,并给出了 PCB 布线时的注意事项。”

普遍认同的观点是,地平面为电流提供了一个低电感和低电阻的返回路径,并且能够防止不同导线之间的串扰(crosstalk)或耦合(coupling)。 地平面通过提供一个与导线物理距离非常接近的电流返回路径来实现这一点。电感和感性耦合取决于形成的回路面积,而地平面通过最小化这个面积来减少电感和感性耦合。在容性耦合的情况下,地平面“短路”了导线之间的电场,从而最小化了相互电容。 在这些基本要点之后,大家开始出现分歧。有些人说地平面应在电路板的两侧,有些人则说只应在一侧。有些人认为地平面应该在电路的不同区域之间分割,而其他人则认为这样做会使情况变得更糟。有人说应该在高速信号之间放置屏蔽线,也有人说不应该。

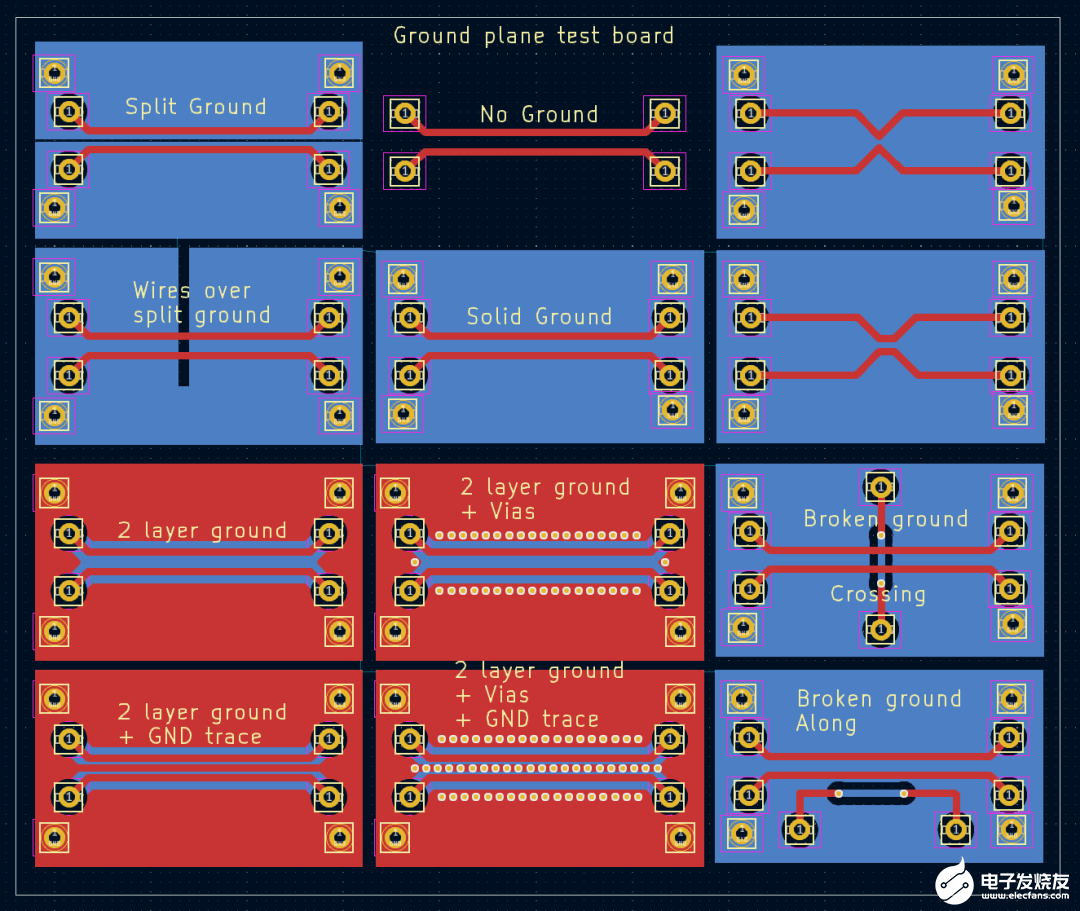

为了测试其中的一些说法,我设计了一块 1.6 mm 厚的电路板,上面有几对 15 mm 长的导线,导线之间有 2 mm 的间隙。无论是电容耦合还是电感耦合,长而平行且靠近的线路都是最糟糕的情况。每根导线的两端都有一个引脚,如果存在地平面,就在导线引脚旁边放置一个地引脚,以保持返回路径尽可能接近:

其中一对没有地平面,另一对只有底层的一个简单的地平面,其余的地平面各有不同:

两个走线之间有分割的地平面。

两个走线穿过分割的地平面的分割处。

有地平面,走线跳转到底层。(一个平行,一个交叉)

两层都有地平面

两层都有地平面,导线旁有过孔。

两层都有地平面,带有屏蔽线

两层都有地平面,带有屏蔽线,且屏蔽线上和走线旁都有过孔。

我用 50 MHz 正弦波(10ns 上升/下降时间)进行了测试,这应该能代表典型的业余项目,但不适用于微波范围的测试(所使用的波长比走线大得多)。

电容耦合

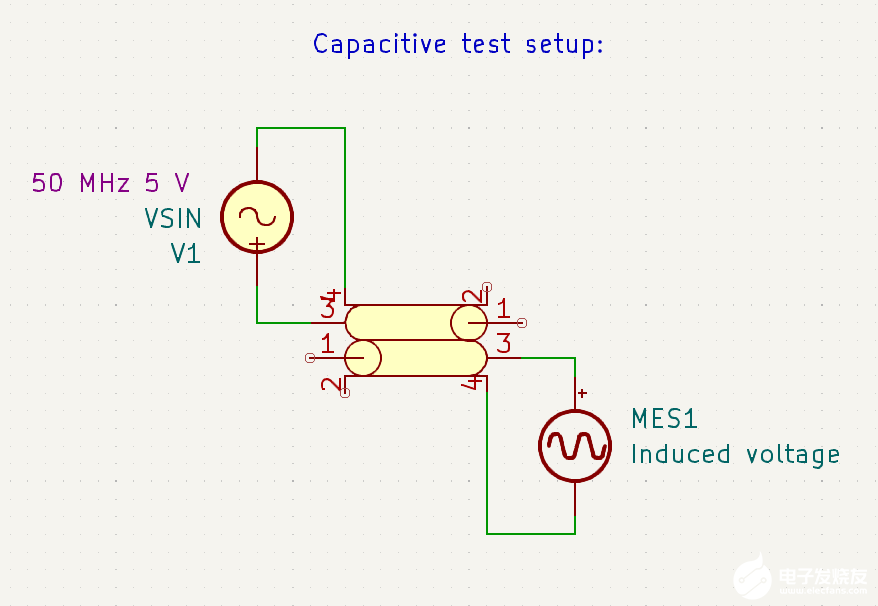

实验目的:测量电容耦合

实验设备:

函数发生器(Function generator):用于产生一个 5V 的 50MHz 正弦波信号。

示波器(Scope):用于测量和显示信号。

实验步骤:

将函数发生器的输出连接到一根导线的一端。

将示波器的探头连接到另一条导线的另一端,用于测量信号。

在进行有地平面的测试时,移除了示波器探头的标准地线(ground lead),并使用一根短于2厘米的导线,将探头的地环(ground ring)连接到地平面上。

在没有地平面的测试中,直接将示波器的地夹(ground clip)夹到函数发生器的地线上。

示波器探头对地的电容大约是10皮法(pF),大约是74HC逻辑门输入电容的两倍。这些测量值的精度大约是5%,毫伏级别的电压变化可能是由于测量误差造成的,不必过于关注。 以下为测量结果:

| 配置 | 耦合电压峰峰值 |

| 无地平面,15cm示波器地线夹提供地 | 800 mV |

| 标准地平面 | 340 mV |

| 走线之间有分割的地平面 | 352 mV |

| 走线跨过分割的地平面 | 360 mV |

| 标准地平面,但有导线切割穿过地平面;且待测的信号线跨过切割的导线 | 351 mV |

| 标准地平面,但有导线切割穿过地平面;且待测的信号线平行靠近切割的导线 | 340 mV |

| 双面的地平面 | 294 mV |

| 双面的地平面+缝合孔(仅一侧) | 300 mV |

| 双面的地平面+屏蔽线 | 88 mV |

| 双面的地平面+屏蔽线+缝合孔 | 48 mV |

地平面对电容耦合的影响:

即使在最糟糕的布局中,接地平面也能将电容耦合降低 2 倍以上。这意味着地平面提供了一个低电感和低电阻的电流返回路径,并且能够减少不同走线之间的串扰和耦合。

通常建议在电源、数字和模拟部分之间分割地平面,但这样做实际上增加了耦合。

在双面接地的情况下,走线只有在两侧都有缝合孔的情况下耦合才会有所改善;如果在两个走线之间放置一个接地的屏蔽走线,效果会更好(比没有地平面好16倍以上)。

地平面下的短走线的影响:

在远小于波长的尺度上,地平面下的短走线影响相对较小。

我测量了从一个交叉走线耦合到主走线的信号为153毫伏,这个值并不小,但并不像平行走线那样糟糕。

地平面上走线的对地电容:

地平面上的走线对地有显著的电容,对于1毫米宽的走线大约是每厘米0.7皮法。这可能会给高阻抗信号带来麻烦,即使是相对较短的走线。

随着板层数的增加,这种电容会变得更糟,尤其是当习惯于将地/电源平面放置在板的中间层时。

驱动阻抗对电容耦合的影响:

驱动阻抗对于电容耦合非常重要。当受影响的走线通过 100Ω电阻驱动而不是开路时,耦合信号降低到原始电压的约1/4。

电感耦合

对于电感耦合,我也使用了 50 MHz 正弦波,但将导线的另一端接地。我还添加了一个 10 欧姆的电流检测电阻(10mV = 1mA)来测量电流。

同样,这些测量值的精确度仅为 5%左右,因此无需在意单毫伏的差异。

| 配置 | 旁路电压峰峰值 | 耦合电压峰峰值 |

| 无地平面,15cm示波器地线夹提供地 | 8 mV | 62 mV |

| 标准地平面 | 12 mV | 26 mV |

| 走线之间有分割的地平面 | 11 mV | 28 mV |

| 走线跨过分割的地平面 | 10 mV | 29 mV |

| 标准地平面,但由导线切割穿过地平面;且待测的信号线跨过切割的导线 | 8 mV | 44 mV |

| 标准地平面,但由导线切割穿过地平面;且待测的信号线平行靠近切割的导线 | 9 mV | 28 mV |

| 双面的地平面 | 11 mV | 28 mV |

| 双面的地平面+缝合孔 | 9 mV | 22 mV |

| 双面的地平面+屏蔽线 | 10 mV | 33 mV |

| 双面的地平面+屏蔽线+缝合孔 | 10 mV | 7 mV |

这里的结果与电容耦合的结果类似,并不与电容耦合的结论相悖。虽然与电容耦合相比,电感耦合看起来微不足道,但它会对驱动阻抗很低(如测试中使用的 0 欧姆短路)的线路产生影响,而且这里使用的电流仅为毫安,而不是驱动 MOSFET 栅极等常用的几安培电流。

耦合到底重要吗?

虽然50 MHz的频率看似很高,但数字信号中的耦合现象很容易发生。即使方波的频率只有几千赫兹,根据上升时间的不同,谐波也可能高达数百兆赫兹。由于低阻抗输出和逻辑电平之间的较大差距,数字线路本身具有相当强的抗干扰能力。 然而,大多数项目都会在某些时候处理模拟信号,而这些信号很容易受到快速切换的数字线路的干扰。最简单的解决方法是将数字部分和敏感的模拟部分物理隔离,并避免它们之间的平行走线。使用去耦电容、磁珠和地平面保持电源清洁也非常重要。高阻抗线路很容易出现问题,因此尽可能避免高阻抗线路,并保持他们的长度尽可能的短是理想的选择。最后的办法是在地平面上使用带缝合孔的屏蔽线。 如果耦合不可避免,另一种方法是降低数字信号的速度,例如在输出端放置一个 5 千欧电阻。这不会对低速信号产生影响,但可以减缓有问题的信号边缘。 另一种情况是电流的返回路径不是地平面,这种情况下地平面的效果会大打折扣。在这种情况下,在PCB上布线时要让信号走线和返回路径尽可能靠近,并保持整体长度尽可能短。

参考文献: https://10maurycy10.github.io/projects/testing_groundplanes/ 本文遵循 Creative Commons Attribution-ShareAlike 4.0 International License.

注意:如果想第一时间收到 KiCad 内容推送,请点击下方的名片,按关注,再设为星标。

常用合集汇总:

和 Dr Peter 一起学 KiCad

KiCad 8 探秘合集

KiCad 使用经验分享

KiCad 设计项目(Made with KiCad)

常见问题与解决方法

KiCad 开发笔记

插件应用

发布记录

审核编辑 黄宇

-

pcb

+关注

关注

4391文章

23745浏览量

420802 -

电感耦合

+关注

关注

1文章

69浏览量

16356

发布评论请先 登录

高频PCB布线“避坑指南”:4大核心技巧让信号完整性提升90%

到底DDR走线能不能参考电源层啊?

降低adc在不同PCB上的噪声,如何做到接近AD4134验证板噪声水平?

多层PCB板在医疗领域的应用

如何减小DAC电路的耦合影响?

PCB叠层设计避坑指南

PCB的EMC设计(一):层的设置与排布原则

PCB 地平面奥秘及耦合的探究

PCB 地平面奥秘及耦合的探究

评论