当今处理器一共有三个最强大的架构,其中之一是以intel和AMD为代表的x86架构,另外一个是手机,平板处理器所使用的ARM架构,最后一个便是我国龙芯处理器所选择的MIPS架构。这三大处理器架构中,x86和ARM是商业化进程最为优秀的两大架构。也正是因为这两大架构的商业化进程太为出色,所以我国的龙芯处理器才被很多人批判为最严重的选择性失误。

但是从处理器的设计和能耗比来说,如果要说最经典的RISC处理器,那么非MIPS莫属,就连它的竞争对手,也不得不承认它的优雅,它被作为处理器教科书的典范,很多其他的处理器,都能看到它的身影。

为什么史上最强IC公司Intel和最早的RISC公司收到ARM的步步蚕食?我们今天来了解一下,欢迎大家在“评论”发表自己观点。

随着ARM在智能手机市场独占鳌头,如同两把尖刀刺入intel和MIPS的腹地。

众所周知,基于MIPS的MCU的应用广泛多元,包括工业、办公自动化、汽车、消费电子系统和先进技术,如无线通信等。此外,我们看到目前可穿戴和超便携市场的需求不断增长,瞄准这一领域的公司迫切希望硅IP供应商如Imagination等提供高效的解决方案,以便可以轻易集成进那些全功能产品中。

MIPS的前世今生

MIPS是世界上很流行的一种RISC处理器。MIPS的意思是“无内部互锁流水级的微处理

器”(Microprocessor without interlocked piped stages),其机制是尽量利用软件办法避免流水线中的数据相关问题。它最早是在80年代初期由斯坦福(Stanford)大学Hennessy教授领 导的研究小组研制出来的。MIPS公司的R系列就是在此基础上开发的RISC工业产品的微处理器。这些系列产品为很多计算机公司采用构成各种工作站和计算 机系统。

MIPS技术公司是美国著名的芯片设计公司,它采用精简指令系统计算结构(RISC)来设计芯片。和英特尔采用的复杂指令系统计算结构(CISC)相比, RISC具有设计更简单、设计周期更短等优点,并可以应用更多先进的技术,开发更快的下一代处理器。MIPS是出现最早的商业RISC架构芯片之一,新的 架构集成了所有原来MIPS指令集,并增加了许多更强大的功能。

1986年推出R2000处理器,1988年推出R3000处理器,1991年推出第一款64位商用微处理器R4000。之后,又陆续推出R8000(于 1994年)、R10000(于1996年)和R12000(于1997年)等型号。1999年,MIPS公司发布MIPS 32和MIPS 64架构标准。2000年,MIPS公司发布了针对MIPS 32 4Kc的新版本以及未来64位MIPS 64 20Kc处理器内核。

在MIPS芯片的发展过程中,SGI公司在1992年收购了MIPS计算机公司,1998年,MIPS公司又脱离了SGI,成为MIPS技术公司; MIPS32 4KcTM 处理器是采用MIPS技术特定为片上系统(System-On-a-Chip)而设计的高性能、低电压 32位MIPS RISC 内核。采用MIPS32TM体系结构,并且具有R4000存储器管理单元(MMU)以及扩展的优先级模式,使得这个处理器与目前嵌入式领域广泛应用的 R3000和R4000系列(32位)微处理器完全兼容.

新的 64 位 MIPS 处理器是RM9000x2,从“x2”这个标记判断,它包含了不是一个而是两个均具有集成二级高速缓存的64位处理器。RM9000x2 主要针对网络基础设施市场,具有集成的 DDR 内存控制器和超高速的 HyperTransport I/O 链接。处理器、内存和 I/O均通过分组交叉连接起来的,可实现高性能、全面高速缓存的统一芯片系统。除通过并行处理提高系统性能外,RM9000x2 还通过将超标量与超流水线技术相结合来提高单个处理器的性能。

64位处理器MIPS 64 20Kc的浮点能力强,可以组成不同的系统,从一个处理器的Octane工作站到64个处理器的Origin 2000服务器;这种CPU更适合图形工作站使用。MIPS最新的R12000芯片已经在SGI的服务器中得到应用,目前其主频最大可达400MHz。

MIPS处理器是八十年代中期RISC CPU设计的一大热点。MIPS是卖的最好的RISC CPU,可以从任何地方,如Sony, Nintendo的游戏机,Cisco的路由器和SGI超级计算机,看见MIPS产品在销售。目前随着RISC体系结构遭到x86芯片的竞争,MIPS有 可能是起初RISC CPU设计中唯一的一个在本世纪盈利的。和英特尔相比,MIPS的授权费用比较低,也就为除英特尔外的大多数芯片厂商所采用。

MIPS的系统结构及设计理念比较先进,其指令系统经过通用处理器指令体系MIPS I、MIPS II、MIPS III、MIPS IV到MIPS V,嵌入式指令体系MIPS16、MIPS32到MIPS64的发展已经十分成熟。在设计理念上MIPS强调软硬件协同提高性能,同时简化硬件设计。

中国龙芯2和前代产品采用的都是64位MIPS指令架构,它与大家平常所知道的X86指令架构互不兼容,MIPS指令架构由MIPS公司所创,属于 RISC体系。过去,MIPS架构的产品多见于工作站领域,索尼PS2游戏机所用的“Emotion Engine”也采用MIPS指令,这些MIPS处理器的性能都非常强劲,而龙芯2也属于这个阵营,在软件方面与上述产品完全兼容。

MIPS 技术公司则是一家设计制造高性能、高档次及嵌入式32位和64位处理器的厂商。在通用方面,MIPS R系列微处理器用于构建SGI的高性能工作站、服务器和超级计算机系统。在嵌入式方面,MIPS K系列微处理器是目前仅次于ARM的用得最多的处理器之一(1999年以前MIPS是世界上用得最多的处理器),其应用领域覆盖游戏机、路由器、激光打印 机、掌上电脑等各个方面。

由于服务器RISC处理器市场的激烈竞争结果导致HP 公司放弃它的PA-RISC和“私生子”Alpha 两种类型服务器处理器,而“Alpha技术”则被Intel和AMD吸收应用到他们自身的处理器中; MIPS处理器应用范围则较广,对于作为服务器RISC处理器来说,主要是应用于专门的图形工作站/服务器上;相对来说,应用面较专业,因而竞争较少。就 目前的服务器RISC处理器来说,主要是IBM 的POWER和SUN 的UltraSPARC 两大处理器之间的竞争;相对而言,IBM在这场RISC处理器竞争中是个大赢家。

MIPS VS ARM

以RISC技术为基础,再加上MIPS架构中的可扩展硬软件设计,使得MIPS的解决方案比ARM的同类解决方案性能更高、功耗更低且面积更小。MIPS科技原来主要瞄准高性能工作站与服务器,而ARM最初针对低端移动系统开发基本内核。MIPS充分利用它在高性能设计方面的经验,向主流嵌入式系统市场转型。ARM则继续沿用其原有性能有限的架构,相比MIPS,它处于不利地位。

MIPS32 4K®处理器内核系列包括MIPS32 M4K®内核,其应用程序执行速度超过同类ARM Cortex™-M系列内核。这一优势部分可归功于更高效的MIPS指令集架构和优化软件工具,但主要原因还是在于MIPS架构具有众多专为更高的性能级和应用效率而设计的出色特性,其中包括一般是在微控制器设计中实现的加速功能。例如:

• MIPS 内核包含32个GPR(通用寄存器),而ARM内核只有16个GPR。这意味着寄存器溢出更少,从而性能更高。

• MIPS内核包含有影子寄存器组,而ARM内核没有。使用映像寄存器可加速中断处理保存/恢复功能,减少上下文切换(context switching)和中断延迟中所需要的周期。

• MIPS架构主要执行单一操作指令,而ARM指令在写入GPR之前执行多个操作(如移位操作、算术操作、条件校验位等等),故MIPS更容易达到更高的时钟频率。

• MIPS架构采用比ARM更简单的存储器寻址模式工作,故更容易达到更高的时钟工作频率。

• MIPS架构的预测执行较少,这大大降低了其逻辑复杂性,并使MIPS内核能够达到更高的频率。

• M4K与M14K具有5级流水线结构,故无需预测分支方向。而ARM内核采用了复杂的分支预测和分支推测逻辑。

• MIPS架构实现了带延迟的分支,而ARM结构不这样;这意味着,利用MIPS,在短流水设计时可获得更高效率。

• MIPS同时提供32位和64位架构,MIPS64架构具有后向兼容性和更高的性能。ARM只有32位架构,而且并非所有版本都后向兼容。

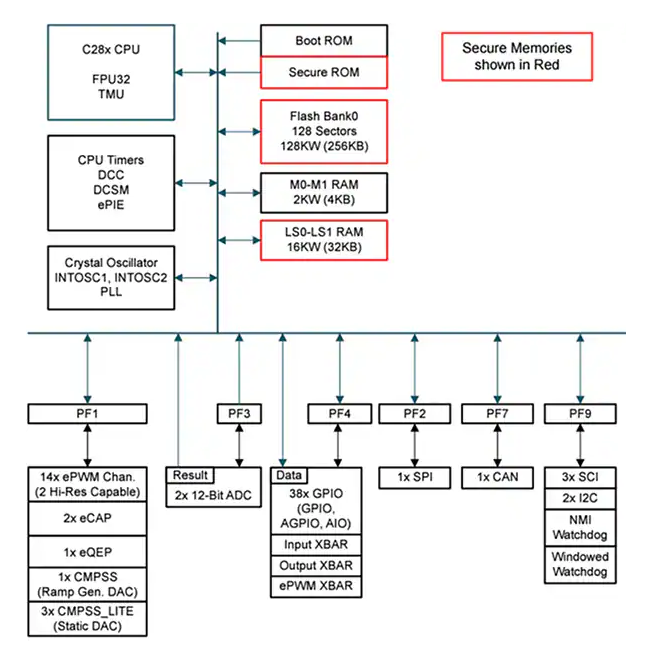

M4K 执行流水线

M4K内核的性能可达1.5 DMIPS/MHz,而根据ARM网站公布的数据,Cortex-M3的性能只有1.25 DMIPS/MHz,比前者低约20% (ARM Cortex-M0的性能甚至更低,仅0.9 DMIPS/MHz,比MIPS32 M4K内核低40%;Cortex-M0 还存在众多其它局限性,我们接下来会讨论到)。换言之,Cortex-M3 需要使用高20%的时钟频率才能达到M4K内核的性能,但随之产生更多的功耗。

类似的,如第4节的“性能基准”所述,在采用CoreMark 基准时,M4K内核可达到2.297 CM/MHz的性能,比同类的基于Cortex-M3的解决方案高20-30%。MIPS已把业内越来越获认可的CoreMark基准视为比Dhrystone MIPS更精确的CPU性能测量标准。

M4K执行单元采用5级流水线微架构,如图2所示,而Cortex-M3内核的执行则基于3级流水线架构。因此M4K内核能够采用更高的最大时钟频率,每秒钟处理更多的指令,从而获得比Cortex-M3更高的性能和执行效率。

在M4K内核中,所有ALU和移位操作都在单周期内完成。旁路逻辑(Bypass logic)包含在流水线中,在所有流水线级完成之前提供快速数据存取以供下一条指令所用。由于执行特定任务的周期缩短,性能得以提高。

MIPS架构是龙芯发展的唯一选择

在自MIPS中国看来,龙芯处理器的架构选择并没有错误,相反的如果龙芯要想得到更好的发展,选择MIPS才是最为正确的道路。这又是为何呢?这还要从这三大架构的拥有者谈起。

x86架构的拥有者intel可以算作是技术合作上最抠门儿的一位,在推出x86架构之后,intel就只将这一架构授权给过AMD和VIA等几个芯片公司。而在VIA退出x86架构处理器竞争之后,intel便不再给任何公司x86架构授权。所以从x86架构上入手,龙芯处理器显然是行不通的。intel的x86架构行不通,那么ARM架构是否就能行得通呢?答案当然也是否定的。

x86被intel独占几十年,奉行的是肥水不流外人田的政策

ARM公司是一家非常优秀的芯片设计公司,但自身并不生产处理器,而是将自身的设计licensing卖给需要处理器的公司,而后交给他们生产或者是找人代工。也许有人要问了,既然ARM向外卖出架构设计,那么为何龙芯不去选择ARM架构呢?其实不然,ARM之所以能够发展成为一家非常成功的商业性公司,靠的就是芯片的架构设计,倘若架构设计被别人夺走了,那么自己就丢掉了赖以生存的饭碗。所以ARM虽然对外进行licensing授权,却不允许购买者进行任何对ARM架构有更改的设计。倘若个更改了设计,那么这便违反了合作协定。ARM便有权撤回licensing授权。我国的龙芯要是选择了ARM架构的话,那么基本上也就被捆住了脚步,无法发展出属于自己的高性能处理器了。

自身虽然强大,但因考虑到市场发展的问题ARM也对外妥协过。目前高通,苹果和NVIDIA这三家公司便是ARM体系中较为特殊的几个。因为这三家公司在芯片设计领域的特殊地位,ARM为了能够拉拢他们站立在自己的阵营中,对这三家公司开出了特别通行证。在其他芯片公司只能使用licensing去生产芯片的时候,高通,苹果和NVIDIA却能够自行设计基于ARM架构的处理器。也正是拉拢到了高通,苹果和NVIDIA,才使得ARM拥有了更多的支持者。但即便这样,我们也不得不佩服ARM的老狐狸作风,在给出架构授权后,ARM依然会通过升级下一代架构为由让高通,苹果和NVIDIA再掏一回钱购买架构授权。这样ARM就可以再赚一把。相信看到这里您应该了解到龙芯不选择ARM的原因了。

那么是什么本领让MIPS最终成为了我国龙芯处理器的设计架构呢?答案非常简单,那就是架构授权。也许有人又问了,ARM不也是给授权吗?那为什么还选MIPS呢?面对这样的问题,MIPS和ARM虽然都是对外进行架构授权的公司,但意义完全不同。ARM对外出售的是设计方案授权(licensing),与ARM的商业化相比,MIPS倒像是学院派的公司。MIPS的架构授权,并不限制任何对MIPS架构的更改。换句话说,就是MIPS公司给授权者一张白纸,而白纸上仅仅写着一行字,MIPS公司同意你设计生产MIPS架构处理器,至于你设计成什么样,性能有多高,经过多少代更改,MIPS一概不管,只要你不把架构彻底改变就行了。与ARM相比,MIPS是一个完全开放的架构,对龙芯未来的发展没有任何的限制,这与intel给AMD x86架构授权,而不是给设计图纸的道理是完全一样的。在加上MIPS本身经过几十年的发展,已经拥有了众多的应用软件,综合考虑来看,MIPS是最为适合龙芯处理器发展的架构选择。

MIPS的意思是“无内部互锁流水级的微处理器”(Microprocessor without interlocked piped stages),其机制是尽量利用软件办法避免流水线中的数据相关问题。

互锁的发生主要有以下几种情况,

一是由于流水线中的2个处理模块同时使用同一资源产生冒险,此时等待资源的流水级以及前面的流水级都要等待;

二是由于在某一流水级的操作需要多个时钟周期,整个流水线上的各个流水级等待多周期操作的完成。当互锁发生后,互锁处理模块暂停流水线直到互锁解决。

如果从不同流水级同时发出暂停流水线的请求,也要判断暂停流水线请求的优先级。

MIPS的流水线的特点:

一条经典的5段流水线

每一个周期作为一个流水段;

在各段之间加上锁存器(流水寄存器)。

MIPS的意思是“无内部互锁流水级的微处理器”(Microprocessor without interlocked piped stages),其机制是尽量利用软件办法避免流水线中的数据相关问题。

1、流水寄存器保证了流水线中不同段的指令不会相互影响。每个时钟周期结束之后,该段的所有执行结果都保存在流水段寄存器中,在下一个时钟周期开始作为下一个段的输入。

需要确定处理器在每一个时钟周期都进行什么样的动作。

要保证在同一个周期没有两条指令使用相同的数据通路资源。

可以采用流水线方式下简化的RISC数据通路图来表示。

上图蓝色小方框表示寄存器。

MIPS流水线方式实现时,应解决好以下几个问题:

1、要保证不会在同一时钟周期要求同一个功能段做两件不同的工作。

例如:不能要求ALU同时做有效地址计算和算术运算。

2、避免IF段的访存(取指令)与MEM段的访存(读/写数据)发生冲突。

可以采用分离的指令存储器和数据存储器;

一般采用分离的指令Cache和数据Cache。

ID段和WB段都要访问同一寄存器文件.

如何解决对同一寄存器的访问冲突?

把写操作安排在时钟周期的前半拍完成,把读操作安排在后半拍完成。

上图中,边框画实线表示操作,画虚线表示不做任何操作。

流水寄存器的作用

将各段的工作隔开,使得它们不会互相干扰。

保存相应段的处理结果。

流水线寄存器在两个相邻的流水段之间既传递数据也传递控制信息。后面流水段需要的数据,必须能从一个流水寄存器复制到下一个流水寄存器,直到不再需要为止。

所以流水寄存器与非流水通路中使用的临时寄存器不一样。

解决数据冲突的问题

让一条指令从ID段到EX段的操作称为发射指令。

对于MIPS定点流水线,所有的数据冲突均可以在ID段检测到。

如果存在数据冲突,就在相应的指令流出ID段之前(也就是发射前)将之暂停。完成该工作的硬件称为流水线的互锁机制。

采用数据定向的思想避免数据相关

两种动态调度算法

记分牌算法和Tomasulo算法是两种比较典型的动态调度算法。

尽量减少数据冲突造成的流水线性能影响。

-

intel

+关注

关注

19文章

3510浏览量

191625 -

mips

+关注

关注

1文章

245浏览量

49596 -

龙芯处理器

+关注

关注

1文章

25浏览量

11502

发布评论请先 登录

MPC180LMB安全处理器:功能、架构与应用全解析

ADSP - 2185M数字信号处理器深度剖析:特性、架构与应用指南

ADAU1702音频处理器:音频处理的强大解决方案

SMJ320C80数字信号处理器:架构、特性与应用全解析

TAS3103A数字音频处理器:特性、架构与应用详解

Cortex-M0 处理器介绍

基于E203 NICE协处理器扩展指令

基于E203 NICE协处理器扩展指令2.0

AM67x处理器技术文档总结

什么是ARM架构?你需要知道的一切

德州仪器AM68x Jacinto 8处理器技术解析

处理器MIPS架构的知识您都知道么?没关系这篇文章告诉你

处理器MIPS架构的知识您都知道么?没关系这篇文章告诉你

评论