1. 项目概述

项目说明

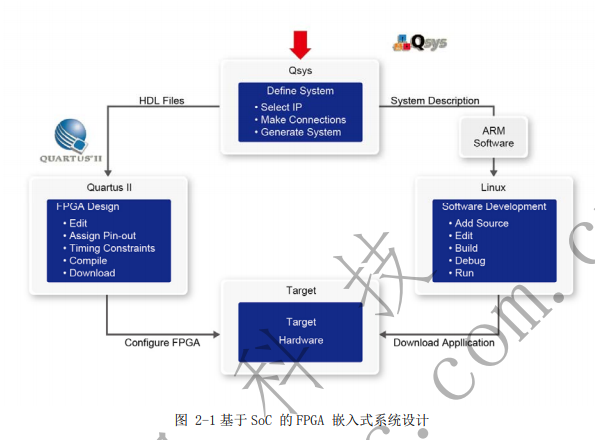

该项目的目标是创建一个用DE1-SOC进行硬件加速的2D N-Body重力模拟器。

该模拟器拥有可定制的地图和基于鼠标的 GUI 交互功能。

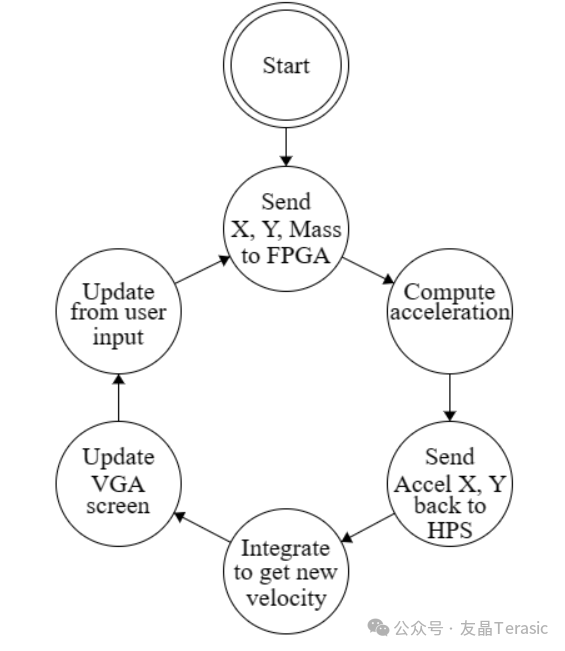

使用标准CPU模拟天体(恒星、行星、小行星等)之间的引力是有限的,因为它只能进行顺序计算,随着天体数量的增加,模拟时间会很长。而该项目是通过将每个天体的信息发送到FPGA来加速这些计算,让它并行计算其他天体之间的每次交互,然后将结果发送回ARM继而显示在显示器上。

2. 数学原理

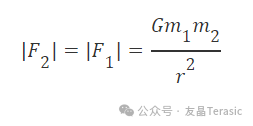

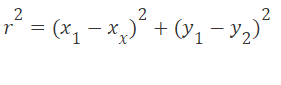

加速器的数学基础从标准牛顿重力方程开始:

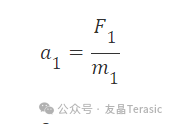

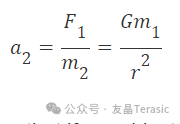

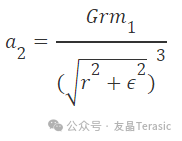

为了简化方程并减少 HPS 处理的计算量,先这样求解加速度:

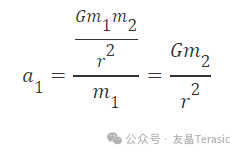

然后用同样的方法计算其他加速度:

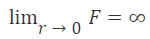

不过,对于这个计算,

这意味着如果物体靠得太近,会产生无限的加速度。这与现实不符,且由于该系统不处理对象的碰撞,因此需要添加不出故障的计算进去。

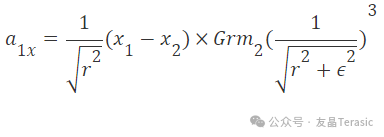

如果用一个偏移量epsilon来规范半径数学计算,就可阻止加速度增加到无穷大。

当选择epsilon取值是10的负8次方时,这意味着它不会明显超出尾数的精度也就是小数点后9位。

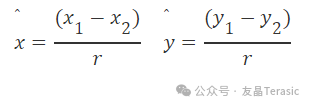

但是这只计算了总加速度。为了将加速度存储为矢量,则这里需要方向分量。为了计算这个,就用x和y的位移除以半径。

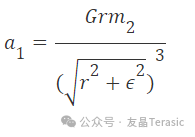

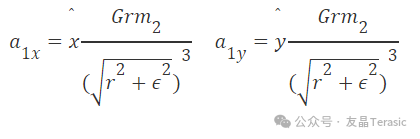

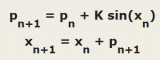

当应用到之前的加速度公式时得到了下面的方程:

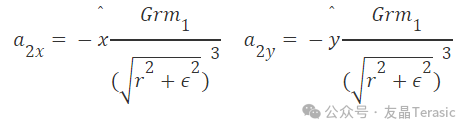

给物体2的加速度加上一个负号因为位移是我们在原始x^计算中计算的负的位移。

由于无法快速执行浮点除法,因此在计算中只能进行3种不同的操作。加/减,乘和反平方根(使用快速反平方根算法)。下面的操作用于计算加速器中的最终结果。首先用2个加法器计算半径的平方来计算x和y的位移,然后将输出与其自身相乘并求出它们的和,也就是半径的平方。

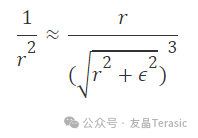

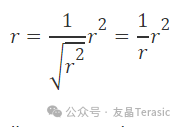

一旦有了半径的平方,就可以试着用半径平方的平方根的倒数来计算半径的倒数。

用半径平方和epsilon平方之和的平方根的倒数,可以用下面的方法计算出前面所述的加速度方程:

更多原理介绍和方法实现请参考项目原文。

审核编辑:刘清

-

FPGA

+关注

关注

1655文章

22286浏览量

630300 -

ARM

+关注

关注

135文章

9499浏览量

388729 -

模拟器

+关注

关注

2文章

992浏览量

45381 -

GUI

+关注

关注

3文章

693浏览量

42852 -

硬件加速器

+关注

关注

0文章

43浏览量

13344

原文标题:FPGA开源项目分享——2D N-Body重力模拟器

文章出处:【微信号:友晶FPGA,微信公众号:友晶FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

基于DE1-SOC开发板的oneAPI实验教程(2)

硬件加速模块的时钟设计

DE1-SOC新货转让

DE1-SoC官方自带ControlPanel代码解读与AV图像采集处理?

de1-soc FPGA(Quartus工程含Qsys系统) + HPS 操作步骤

基于VxWorks的硬件加速技术探讨

如何在DE1-SOC开发板上搭建NIOS II处理器运行UCOS

Veloce仿真环境下的SoC端到端硬件加速器功能验证

ALTERA公司的DE1 SoC FPGA开发板的培训教程免费下载

用DE1-SOC进行硬件加速的2D N-Body重力模拟器设计

用DE1-SOC进行硬件加速的2D N-Body重力模拟器设计

评论