一、高斯白噪声

高斯噪声:是一种随机噪声,其时域内的信号幅度的统计规律服从高斯分布。

白噪声:信号的功率谱在整个频域内为常数的噪声。

带限白噪声:带宽限制在一定范围内的高斯白噪声。

二、产生方法

传统的高斯白噪声的产生是将多个m序列通过D/A转换器,然后通过滤波器得到,比较繁琐。本项目将通过线性反馈移位寄存器和FIR滤波器完成。

首先通过matlab中wgn函数生成高斯白噪声,并将生成的噪声数据存入到rom中,然后通过LFSR产生m序列伪随机码作为rom地址对噪声数据进行读取增加其随机性,最后将输出的随机噪声通过FIR滤波器得到带限白噪声。

三、线性反馈移位寄存器(LFSR)

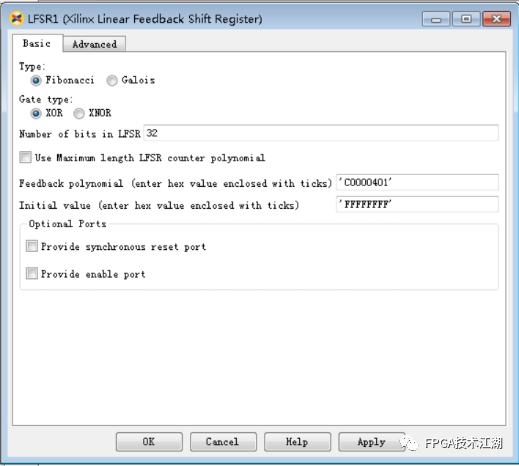

伪随机码的性能指标直接影响产生白噪声的随机性。本设计采用xilinx提供的LFSR IP核来实现。

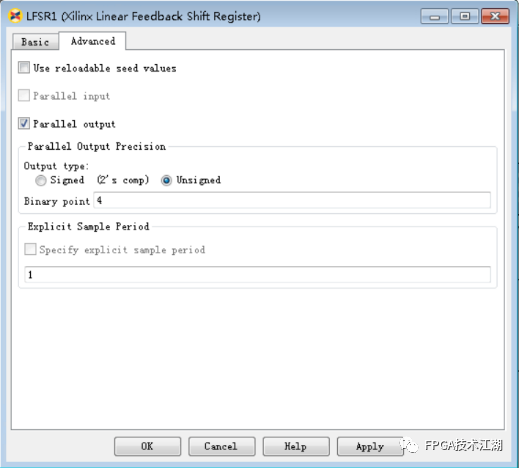

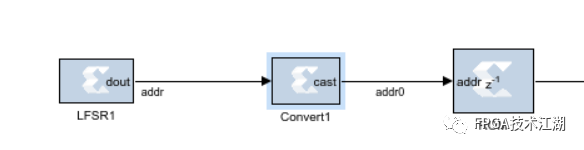

LFSR可以通过如图方式进行配置,可选择输出的数据类型、位宽、小数位等。

本设计选择数据类型为UFIX_32_4,然后再通过convert对其进行截位,得到UFIX_10_0的数据输出作为ROM地址,再一次提高了随机性。

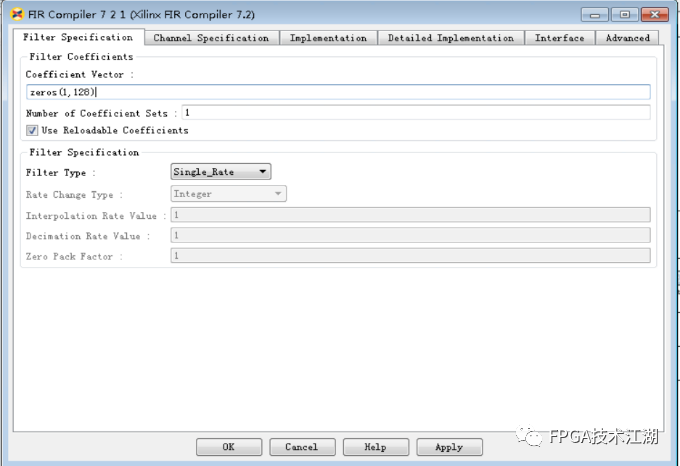

四、FIR滤波器系数重载

该部分滤波器的设计选择Use Reloadable Coefficients模式,接收系统发送的滤波器系数,产生可变带宽的带限噪声信号。

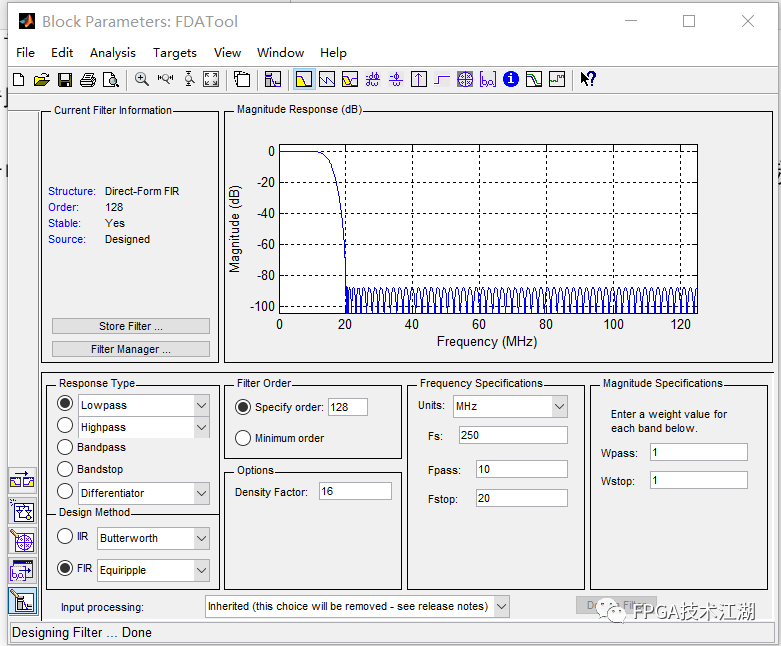

使用可重新加载的滤波器系数时,需将内部系数设置成相同长度的0,然后借助FDATools设计并导出滤波器系数。

本设计中低通FIR滤波器使用等波纹法设计、128阶,250M采样率、通带频率10M、截止频率20M。

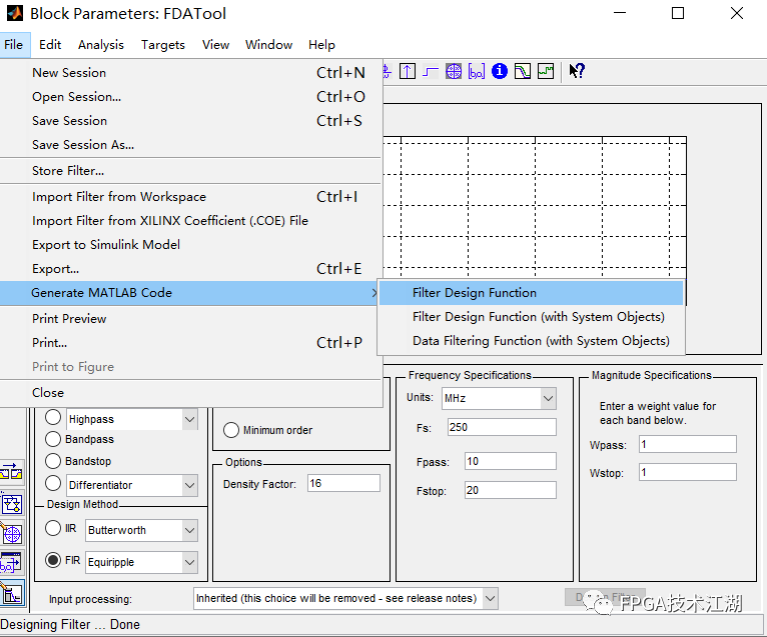

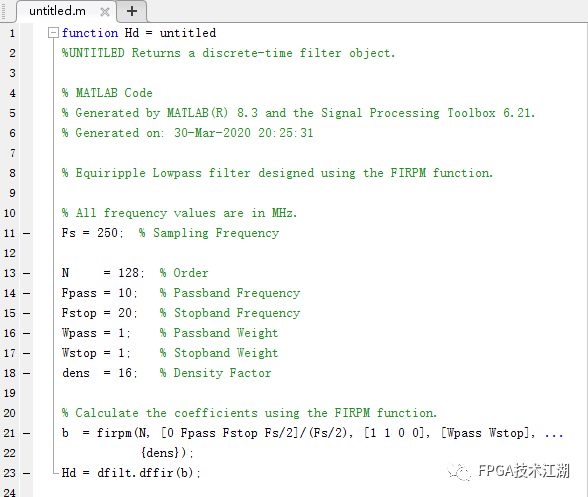

设计完成后可通过下图操作将系数生成.m文件,然后就可以作为重载系数输入到滤波器中了。

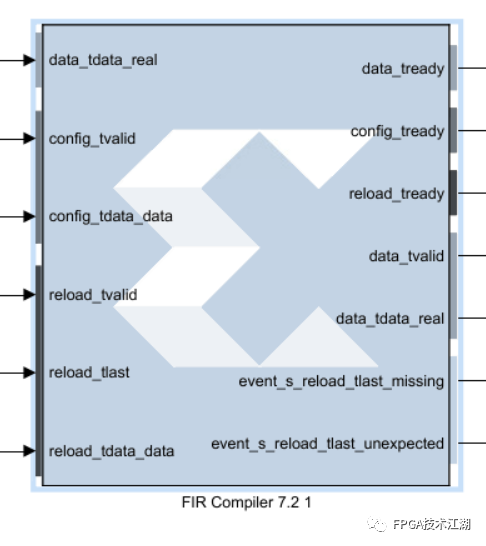

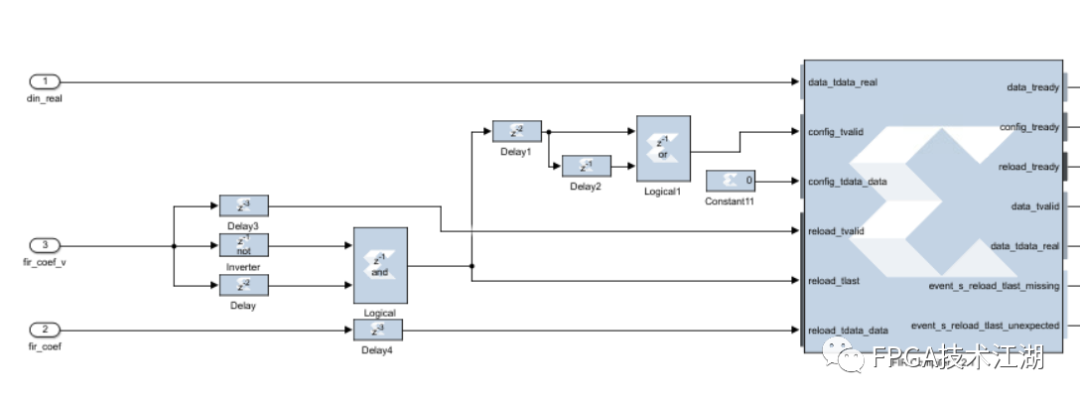

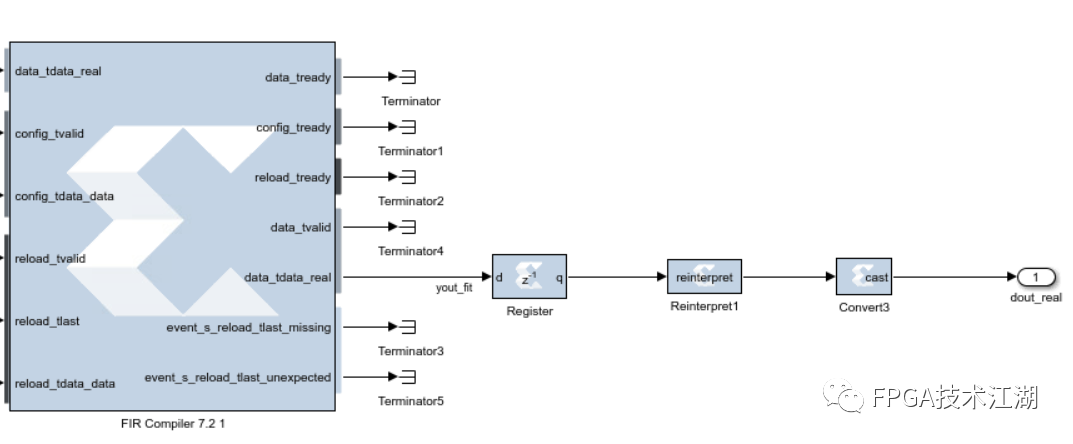

滤波器设置成系数重载模式时,需控制的接口如下图;

其中data_tdata_real即为输入的数据,reload_tdata_data为输入的系数。

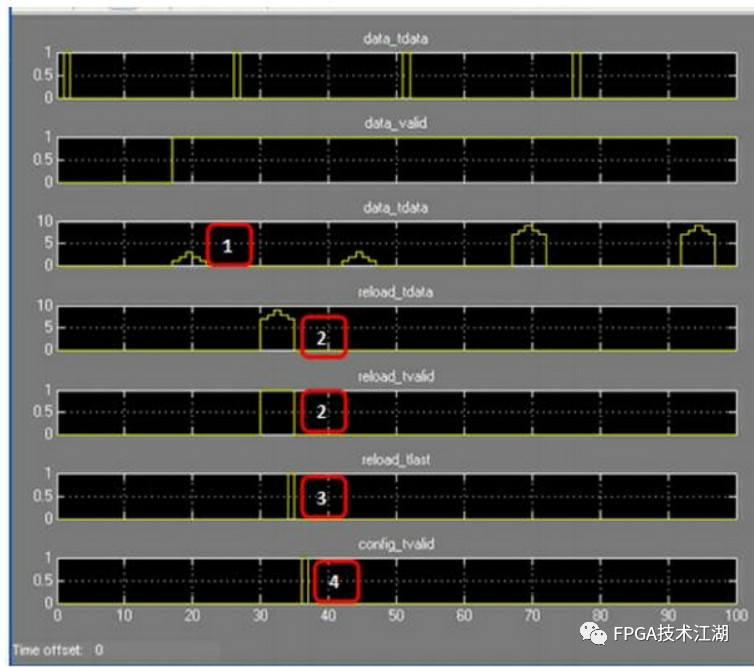

其接口时序图如下图所示:

按照时序要求配置FIR滤波器:

然后对输出数据的位宽和类型进行调整得到结果。

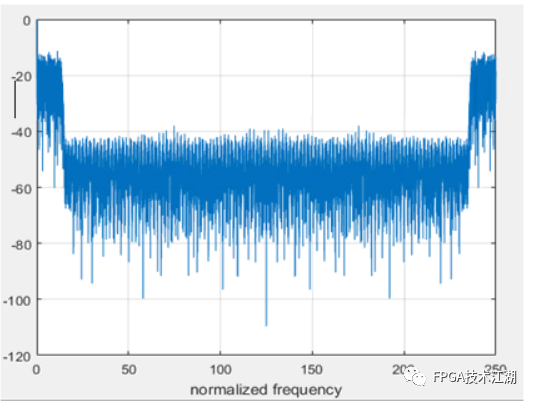

最后得到的带宽为10M的带限白噪声:

审核编辑:刘清

-

matlab

+关注

关注

189文章

3029浏览量

239228 -

ROM

+关注

关注

4文章

579浏览量

89378 -

移位寄存器

+关注

关注

4文章

352浏览量

23426 -

fir滤波器

+关注

关注

1文章

97浏览量

19734 -

高斯白噪声

+关注

关注

0文章

6浏览量

7923

原文标题:往期精选:基于FIR滤波器的带限白噪声的设计

文章出处:【微信号:HXSLH1010101010,微信公众号:FPGA技术江湖】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

使用FPGA构建的数字滤波器设计方案

FIR滤波器FAQ原理简述

基于FPGA的FIR滤波器设计与实现

基于MATLAB与QUARTUS II的FIR滤波器该怎么设计?

fir滤波器的设计和实现

FIR并行滤波器设计

高效FIR滤波器的设计与仿真-基于FPGA

基于FPGA流水线分布式算法的FIR滤波器的实现

基于优化神经网络的FIR滤波器的设计方案

FIR数字滤波器设计方案

FIR滤波器的FPGA设计与实现

基于FIR滤波器的带限白噪声的设计方案实现

基于FIR滤波器的带限白噪声的设计方案实现

评论