电源的作用是为系统提供稳定的电压及电流。电源完整性问题是指电源的电压、纹波及噪声不满足系统的工作要求,通过合理的电源供电网络设计可以减小电源塌陷等电源完整性问题,提高系统的稳定性。

1.电源分配网络

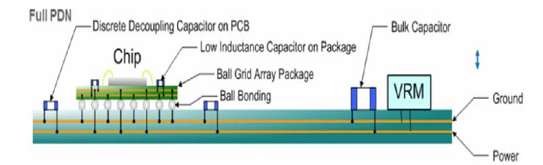

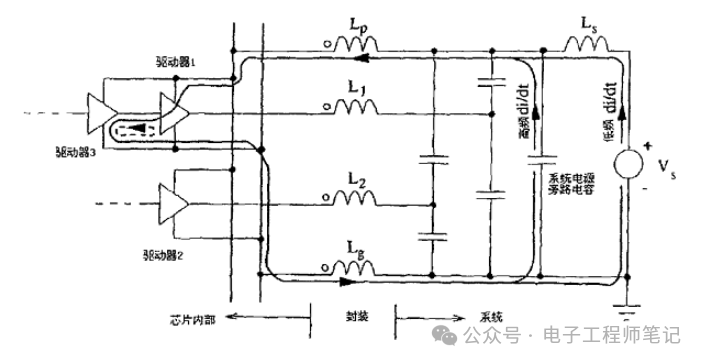

电流从供电模块输出,流经PCB板、芯片封装,最终到达负载芯片给其供电的完整供电路径称之为电源分配网络(PDN),除此之外,它还包含有大量PCB板及芯片封装上的去耦电容。即电源分配网络是电流所经过的所有结构和器件组成的系统,如下图所示。

在上图所示的电源分配网络中,电流从电源模块(VRM)输出后经PCB板上的走线、过孔等结构,通过BGA焊球到达芯片封装,然后经过芯片封装上的走线,进入到封装内部的Die上,给芯片进行供电,其路径中还包括电阻、去耦电容、电感等无源器件。走线、过孔、电阻和去耦电容等都会给电源供电网络带来寄生电感、寄生电容和寄生电阻的影响,导致电源供电网络并不是理想的供电网络。另外,芯片内部的开关速度变得越来越高,供电电压变得越来越低,其对电源配送网络的设计提出了更高的要求。

2.同步开关噪声

在高速数字电路中,当数字集成电路加电工作时,它内部的门电路输出会发生从高到低或者从低到高的状态转换,这时会产生一个瞬间变化的电流△i,这个电流在流经回流路径上存在的电感时会形成交流压降,从而引起噪声,当同时发生状态转换的输出缓冲器较多时,这个压降将足够大,从而导致电源完整性问题,我们将这种噪声称为同步开关噪声(SSN),也叫△i 噪声。

同步开关噪声主要是伴随着器件的同步开关输出(Simultaneous Switch Output,SSO)而产生,开关速度越快,瞬间电流变化越显著,电流回路上的电感越大,则产生的SSN越严重。基本公式为:VSSN=NLLoop(di/dt),其中N是同时开关的驱动器的数目,LLoop为整个回流路径上的电感,i是每个驱动端的电流,而VSSN就是同步开关噪声的大小。这个公式看起来简单,但真正分析起来却不是那么容易,因为不但需要对电路进行合理的建模,还要判断各种可能的回流路径,以及分析不同的工作状态。

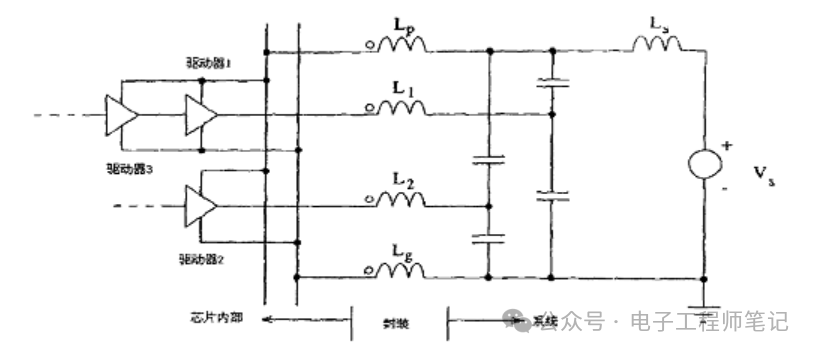

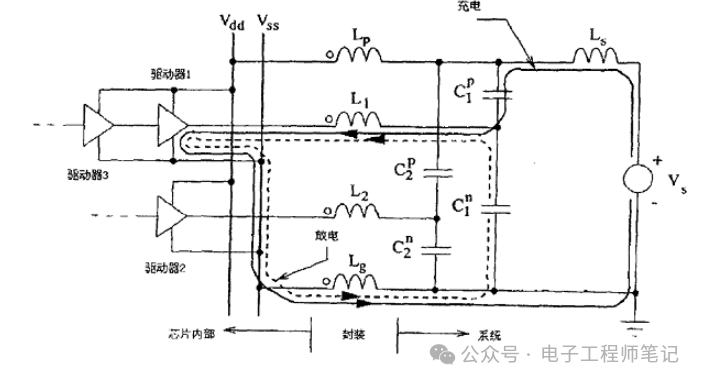

同步开关噪声的产生可以通过下图所示的原理图来解释,其中,封装模型包括自身的电感和封装之间的互电感(互电感没有在图中标出),由于电阻对开关噪声的影响很小,为了简化讨论,这里忽略其影响,系统的接收器用电容表示。

我们可以将同步开关噪声分为两种:芯片内部(on-chip)开关噪声和芯片外部(off-chip)开关噪声。当驱动器3开关输出,驱动器1作为接收端时,产生的噪声称为芯片内部开关噪声;当驱动器1或驱动器2开关输出,将信号传输到系统的接收器时,产生的噪声称为芯片外部开关噪声。两种情况下封装电感的影响各不相同。

2.1芯片内部开关噪声

在上图中,当驱动器3跳变时,它必须对驱动器1的输入电容进行充放电。驱动器3由高电平到低电平转换时的电流路径如下图所示,驱动器3对驱动器1下方的电容进行放电,放电回路如虚线所示,电流完全在芯片内部,不会产生互连噪声;同时对驱动器1上方的电容充电,充电回路如实线所示。驱动器3出低到高转换时,驱动器主上方的电容被放电,同时下方的电容被充电,电流路径不变。

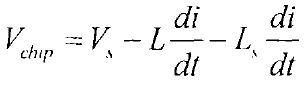

上图中,充电电流流经了封装中电源引脚电感Lp和地引脚电感Lg,而没有流经信号线电感L1和L2。由于Lp和Lg上通过的电流是反向的,所以封装总电感为:L=Lp+Lg-2Mpg,其中Mpg指Lp和Lg之间的互感。由于封装电感L和系统电源电感Ls上产生压降,则芯片实际得到的电源电压为:

因而,在开关的瞬间,加在芯片上的电源电压会下降,随后围绕Vs呈现阻尼振荡。

要将供电下降限制到最小,需要通过减小电感或者电流变化速率来减小感应噪声,通常可以采取的措施有:

⑴降低芯片内部驱动器的开关速率以减小di/di,但是当需要获得很高的时钟频率时,这种方法不可取。

(2)使用电源平面和地平面,并让电源平面和地平面尽量接近以获得最小的系统电源供电电感Ls。

(3)增加电源/地的管脚数目,缩短电源/地的管脚引线长度,以降低芯片封装中的电源和地路径的电感。

(4)电源和地管脚应成对分布并尽量靠近放置,以增加封装中电源和地路径的互感,从而减小封装总电感。

(5)给系统电源增加旁路电容,在此情况下驱动器3由高电平到低电平转换时的电流路径如下图所示,旁路电容可以给高频的瞬变交流信号提供低阻抗的旁路,而变化较慢的信号仍然走系统电源回路,因此产生的噪声电压变小。

(6)在芯片封装内部使用旁路电容,这样高频电流的回路电感会非常小,能在很大程度上减小芯片内部的同步开关噪声。

2.2芯片外部开关噪声

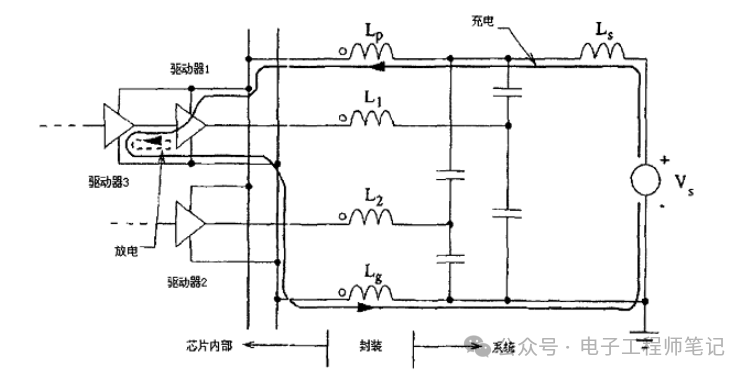

驱动器1出高电平到低电平转换时的电流路径如下图所示,驱动器1对进行放电,放电回路如虚线所示,同时对进行充电,充电回路如实线所示,充、放电电流都是从封装的地引脚流出,从信号线流回,不经过电源引脚;反之,驱动器1由低电平到高电平转换时,充、放电电流都是从信号线流出,从封装的电源引脚流回,不经过地引脚。

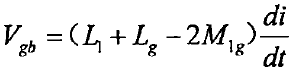

上图中,不考虑系统电源电感Ls,仅封装电感造成的电压降为:

所以,这时芯片地和系统地并不是保持同样的零电位,而是存在Vgb的电压波动,这种情况我们称之为地弹(Ground Bounce)。同样,低电平到高电平转换时,由于感应电压的影响,芯片内电源电压将低于系统电源电压,我们称之为电源反弹。

要减小地弹,可采取以下几种方法:

(1)降低驱动器的边沿速率,满足时序要求的最慢边沿速率将产生最小的噪声。

(2)减小封装回路电感,即减小自感或者增大互感。

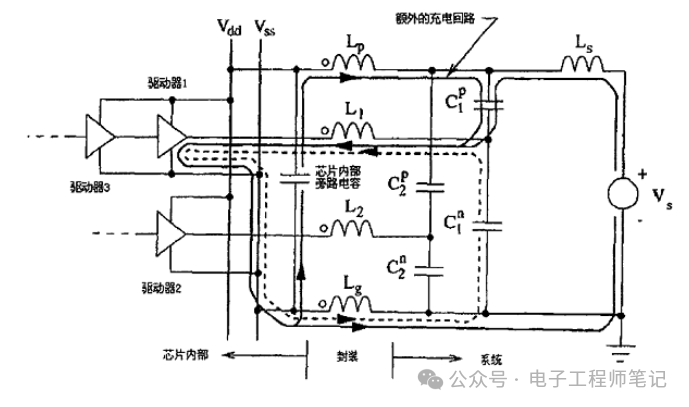

(3)在芯片封装内部使用旁路电容,在这种情况下驱动器1从高电平到低平转换时的电流路径如下图所示,增加了额外的充电回路,封装的电源引脚和地引脚共同分担充电电流回路,从而减小电压波动。

对于电源反弹,可以采用类似的分析方法和抑制措施。

审核编辑:刘清

-

PCB板

+关注

关注

27文章

1487浏览量

54783 -

缓冲器

+关注

关注

6文章

2215浏览量

48681 -

BGA

+关注

关注

5文章

581浏览量

50963 -

去耦电容

+关注

关注

12文章

325浏览量

23477 -

电源完整性

+关注

关注

9文章

223浏览量

21832

原文标题:电源完整性分析

文章出处:【微信号:电子工程师笔记,微信公众号:电子工程师笔记】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

信号完整性与电源完整性的仿真分析与设计

电源完整性分析

电源完整性设计分析

电源完整性问题是指什么?电源完整性分析

电源完整性问题是指什么?电源完整性分析

评论