数字减法器电路的性能指标

目前,针对数字电路研究的主要目标都是为了提高电路的运算速度、降低电路的功耗和减少电路逻辑输出的误差,因此延时、功耗和误差是数字电路三个最重要的性能指标。

运算速度指标——延时

数字电路的延时主要是指信号的传输延时,电路的延时与逻辑门的工艺设计相关,延时限制了电路的工作速度,所以对电路的延时优化一直是很多学者研究的热点。全减器模块作为最基本的电路组成部件,整个电路的延时取决于全减器模块的延时,因此,对全减器模块延时的优化工作显得尤为重要。

对于全减器来说,延时优化主要方法是减小信号在关键路径上的延时;对于串行进位减法器电路来说,关键路径就是指信号进位位支路(也就是对电路中所有的输入来说,信号延时时间最大时的情形),减小进位位支路的延时时间,对于提高串行进位减法器电路运算速度具有重要意义。

近年来,随着电路低功耗设计的要求,电源电压随之降低,而电源电压的降低又会增大电路中信号的传输延时时间,从而影响电路的逻辑输出结果。尤其是在时钟周期固定的同步电路中,如何保证电路正确的逻辑输出结果,实现电路的可靠性设计和最大限度的降低功耗是当前电路设计研究的主要课题。

能量消耗指标——功耗

CMOS 电路中功耗由两部分组成:动态功耗、静态功耗。动态功耗主要是由 CMOS 电路中逻辑门工作过程中负载电容充放电时引起的功耗,主要包括翻转功耗(翻转指的是电路中信号 0→1 或 1→0 的变换)和短路功耗。

翻转功耗是数字电路要完成逻辑功能计算所必须要消耗的功耗,也称有效功耗;短路功耗是由于 CMOS 在翻转过程中 PMOS 管和 NMOS 管同时导通时所消耗的功耗,也称无效功耗;静态功耗是由于漏电电流引起的功耗。

通常静态功耗与电路中的器件相关,在电路设计过程中,如何降低整体的电路功耗已成为当今电路研究者与设计者十分关注的问题,特别是要考虑到如何降低电路的动态功耗。

可靠性指标——误差

在同步电路中,由于时钟周期的存在,一旦电路总的延时时间超过了时钟周期,那么在时钟周期内我们采样得到的电路输出结果与理论上电路正确的逻辑输出结果不同,此时电路实际上输出的是错误的结果。

因此,如何保证电路最终的输出结果是正确的,最大限度的减小误差也是目前电路研究的一个热点方向。

两位格雷码减法器数字电路设计

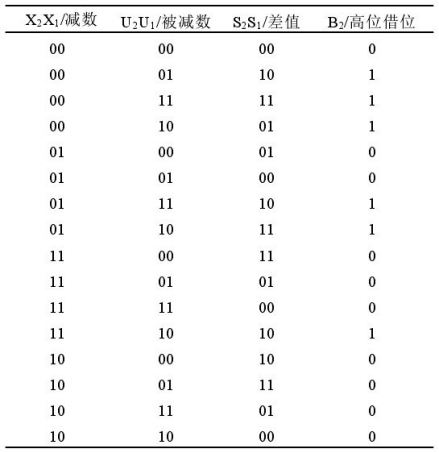

两位减法器的格雷码(Gray code)真值表如图13所示,可以实现两个两位二进制数之间的减法算术运算。从真值表中可以得知,存在 16 种不同的逻辑运算。

如表 4-1 所示,X2X1****和 U2U1 分别代表减数和被减数,S2S1 代表两个两位二进制数之间的差值,B2代表来自高位的借位。在图13中,减数、被减数和差值都通过使用格雷码来表示,格雷码可以转换成二进制码(8421 码),即从左边的第二位开始,在每个位和左边的解码值之间获得异或操作的值作为该位的解码值,最左边的值保持不变。

图13 两位减法器操作运算的真值表

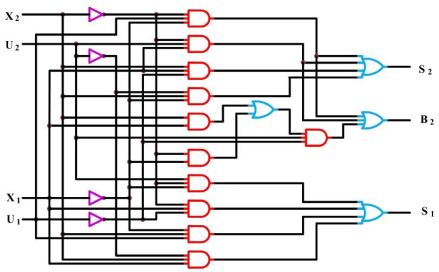

根据两位格雷码减法器的真值表,列写其布尔逻辑表达式,依据其布尔表达式,构造相应的数字电路原理图,如图14所示,有三种基本的逻辑门,即非门、与门、或门,不同的逻辑门使用不同的颜色标记,使用紫罗兰色标记非门,红色标记与门,天蓝色标记或门,图14中共存在 4 个非门,11 个与门,4 个或门。

图14 两位格雷码减法器原理图

-

逻辑门

+关注

关注

1文章

159浏览量

26373 -

二进制

+关注

关注

2文章

809浏览量

43201 -

格雷码

+关注

关注

2文章

34浏览量

13559 -

减法器

+关注

关注

1文章

26浏览量

17408 -

CMOS电路

+关注

关注

0文章

50浏览量

12101

发布评论请先 登录

两位格雷码减法器数字电路设计

两位格雷码减法器数字电路设计

评论