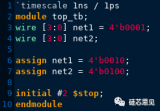

Verilog代码

以VCS 2017为例,可以使用-autoprotect128/-auto2protect128/-auto3protect128选项,实现不同级别的自动代码加密。以auto2protect128为例,可以对module内除端口列表以外的内容加密。

vcs -auto2protect128 -f dut_file_list.f

还有一个-protect128选项,需要先在待加密代码前后添加“`protect128”和“`endprotect128”。

SystemVerilog代码

我个人实际测试下来,上面的-autoprotect128/-auto2protect128/-auto3protect128选项不能对SystemVerilog代码自动加密,只能借助于-protect128选项。如果平时写代码过程中就已经添加“`protect128”和“`endprotect128”,可以直接使用vcs命令加密:

vcs-protect128-ftb_file_list.f

而如果平时写代码时没有加,下面提供一个Python脚本,在给定文件列表中每个文件的首行添加“`protect128”,末尾添加“`endprotect128”,具体使用sed和echo命令实现文件首尾添加内容。

#add_protect.py

import sys

import os

def main():

if(len(sys.argv) != 2):

print("Optionsilleagal.")

sys.exit()

else:

o_file = sys.argv[1]

add_protect(o_file)

def add_protect(o_file):

try:

f_obj = open(o_file)

except FileNOtFoundError:

print(o_file+" :no such file.")

else:

for line in f_obj:

os.system("sed -i '1i `protect128' " + line)

os.system("echo'`endprotect128'>>"+line)

f_obj.close()

main()

os模块中的system()函数接受一个字符串参数,其中包含要执行的命令。在21-22行中,line为字符串变量,和前面双引号中的linux命令拼接在一起,组成system()函数的字符串参数。

pythonadd_protect.pytb_file_list.f

审核编辑:黄飞

-

Verilog

+关注

关注

31文章

1374浏览量

114723 -

字符串

+关注

关注

1文章

596浏览量

23212 -

VCS

+关注

关注

0文章

80浏览量

10339 -

python

+关注

关注

58文章

4885浏览量

90309

原文标题:使用VCS进行代码加密的方法

文章出处:【微信号:处芯积律,微信公众号:处芯积律】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

round robin 的 systemverilog 代码

请问GLCM verilog代码不能正常工作该怎么办?

保护您的 IP 内核——第一部分软 IP,第一节:HDL 代码的加密

SystemC 和SystemVerilog的比较

使用Verilog/SystemVerilog硬件描述语言练习数字硬件设计

从Verilog PLI到SystemVerilog DPI的演变过程

verilog-2005和systemverilog-2017标准规范

SystemVerilog相比于Verilog的优势

如何对Verilog/SystemVerilog代码加密

如何对Verilog/SystemVerilog代码加密

评论