写过Verilog和systemverilog的人肯定都用过系统自定义的函数$display,这是预定好的,可以直接调用的功能。但是当Verilog中的task和function不能满足仿真需求时,这就需要自定义一些任务和函数。

Verilog中使用编程语言接口PLI(Program Language Interface)编程语言接口来和C语言程序交互,它提供了一套C语言函数,我们可以调用这些集成函数编写软件C程序。RTL代码编译的时候,这些软件C程序也会集成到仿真环境中。仿真运行后,使用系统任务调用的方式,就可以去访问仿真中的数据结构,也就是说PLI提供一个使得用户自带C函数能够在运行时间访问仿真数据结构的接口。

PLI先后经历了3代的发展: 1985年TF Task/Function interface,第一代VerilogPLI。包含一整套C语言函数库,函数定义在verisuer.h文件中,一般称为TF子程序,主要作用是把任务/函数参数传递给C函数。TF的缺点是它定义系统任务/函数,函数返回值以及需要关联任务/函数名称到C函数的机制。该机制并不是标准化的, 这就意味着每个仿真器有不同的PLI接口机制。TF的一个缺点是定义系统任务/函数名称、函数返回类型以及与任务/函数名称相关联的 C函数的机制。这种机制不是标准化的,这意味着每个模拟器都有不同的 PLI 接口机制。 1

989年ACC Access interface,第二代VerilogPLI。引入了访问程序库的C函数,即ACC函数库,由单独的acc_user.h定义,函数均以acc_作为前缀。它是作为TF的附加库。只是增加了搜索仿真数据结构的功能,但是不能访问RTL和行为级的设计部分。此外,复杂的,因仿真器而异的接口机制也是ACC接口的一大缺点。

1995年VPI Verilog Programming Interface,第三代Verilog PLI。VPI是TF和ACC的超集扩展库。VPI库定义在C函数库文件vpi_user.h。使用VPI, 用户能够访问整个仿真数据结构, 包括系统任务/函数的参数(替换TF) 以及设计的层次结构单元(替换ACC)。

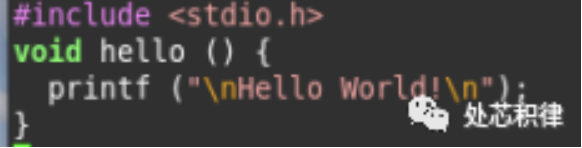

DPI的发展相对来说比较缓慢 Accellera在2003年4月发布了包括DPI在内的SystemVerilog 3.1标准,随后在3.1A版本中进一步对DPI进行了加强。systemverilog中使用DPI(Direct Programming Interface),更加简单地连接C、C++或者其他的非Verilog语言。你只需要使用import语句把C函数导入到,就可以像调用systemverilog的子程序一样来使用它。使用DPI, 用户无需再像Verilog PLI那样, 事先编写系统任务/函数名称,然后通过复杂的PLI库间接传递数值回C函数。但是DPI不能直接访问仿真数据结构的内部,这限制了DPI的应用。

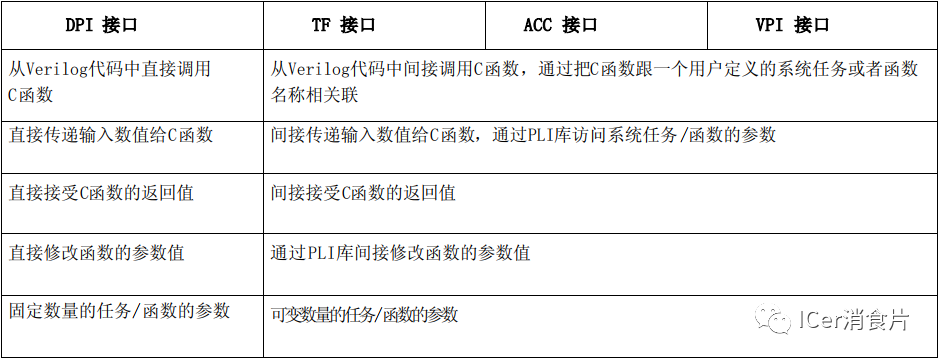

SystemVerilog DPI和Verilog PLI的比较

DPI绝不是为了替代PLI,而是弥补PLI中的不足,相信不久的未来能出现一个新的PI标准更好得结合两者的优点。

审核编辑:刘清

-

Verilog

+关注

关注

30文章

1370浏览量

114140 -

C语言

+关注

关注

183文章

7642浏览量

144619 -

RTL

+关注

关注

1文章

393浏览量

62397 -

DPI

+关注

关注

0文章

41浏览量

11859

原文标题:从Verilog PLI到SystemVerilog DPI的演变

文章出处:【微信号:处芯积律,微信公众号:处芯积律】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

buck电路原理图讲解 buck电路的演变过程

电机瞬变过程

数字式称重传感器的功能演变过程

【视频分享】降压电路的演变过程

The Verilog PLI Handbook

Verilog手册的公众责任

升压变换器二种结构的演变过程资料下载

使用Verilog/SystemVerilog硬件描述语言练习数字硬件设计

谈谈Verilog/System Verilog和C的几种交互模式

buck电路的演变过程

浅析can技术的演变过程

从Verilog PLI到SystemVerilog DPI的演变过程

从Verilog PLI到SystemVerilog DPI的演变过程

评论