在本应用笔记中,我们利用 Moku 云编译和多仪器模式来解释常用移动平均滤波器的开发。我们使用示波器和频率响应分析仪来检测有限脉冲响应(FIR)滤波器。然后,我们使用Moku:Pro、MokuGo设备开发、部署和检测五点中值滤波器。以这种方式组合线性和非线性滤波器,可用于抑制许多控制或传感应用中的尖峰并降低噪声。

Moku云编译

Moku云编译(Moku Cloud Compile, MCC)是Liquid Instruments的一项功能,可让您快速编译自定义硬件描述语言(HDL)代码并将其部署到Moku设备。MCC将Moku内的FPGA开放,可以自定义代码,并允许特定的功能和特性。我们提供一系列示例和支持来帮助您部署自定义功能。

移动平均滤波器

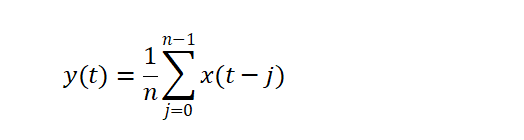

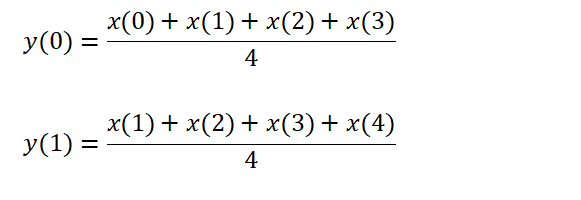

移动平均滤波器是n个连续信号样本的平均值。方程为:

其中x(t)是离散时间序列输入信号,y(t)是输出信号。例如,当n = 4时:

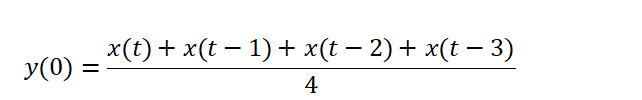

这种滤波器在降低信号噪声方面具有非常有用的应用。对于不相关的白噪声,此移动平均函数最适合抑制噪声并保留尖锐的阶跃响应,但阻带性能较差。在硬件中实现这一点仅需要加法器和一次除法,因此在硬件资源有限的情况下非常有用。在硬件中,除以任意数字在FPGA中并不简单。通常,该滤波器是通过确保n是2的幂(即n=2N)来实现的,从而将除法减少为右移N个二进制位。

图1二进制按位移位示意图

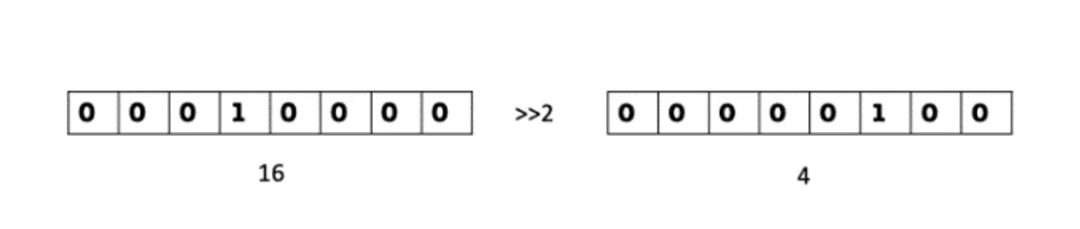

直接硬件实现如图2所示。

图2 以一系列加法器实现移动平均

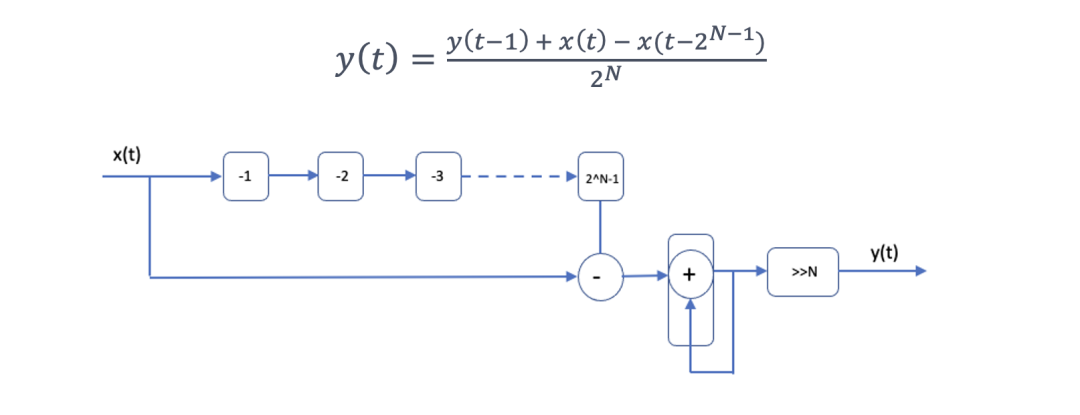

此方案需要2N个加法器,硬件成本比较昂贵。深度加法器还可能需要时钟寄存器来满足合理的时序性能。我们可以通过以下方式改进这一点:

因此,图3更概括地说明了这一点:

图3累加器实现

这说明每个输出取决于先前的输出和当前的输入。现在,我们已将移动平均简化为一个累加器、一个减法器和一个n级移位寄存器,后者用于2N除法的按位右移。当N > 4时,硬件明显有了节省,限制因素是2N级移位寄存器。此外,不需要更多的时钟元件来满足时序限制。

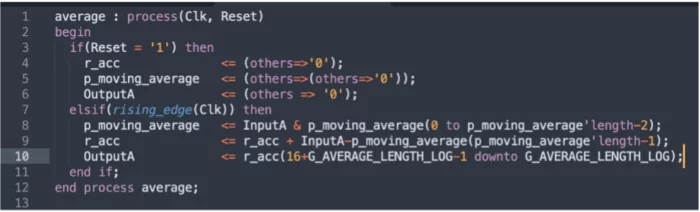

VHDL实现

图4显示了VHDL实现的核心。这个过滤器的核心非常简单,只有12行代码。p_moving_average是最后N个样本的时间历史记录,其中第8行在前面添加最新的输入并删除最旧的输入。在第9行,累加器r_acc正在添加新的输入,而第10行正在生成输出所需的按位移位(除法器)。

编译和部署

编译该VHDL代码非常便捷。

首先,请访问compile.liquidinstruments.com,上传代码,然后选择构建。Liquid Instruments服务器将生成一个文件或比特流,定义FPGA上实现代码所需的硬件配置。对于MokuLab,编译大约需要5分钟;对于 Moku:Pro,由于 FPGA 的尺寸更大,该时间接近20分钟。

此处提供了指导您完成编译和部署的详细说明:

https://www.liquidinstruments.com/blog/2022/09/02/starting-with-moku-cloud-compile/

测试MCC移动

平均滤波器

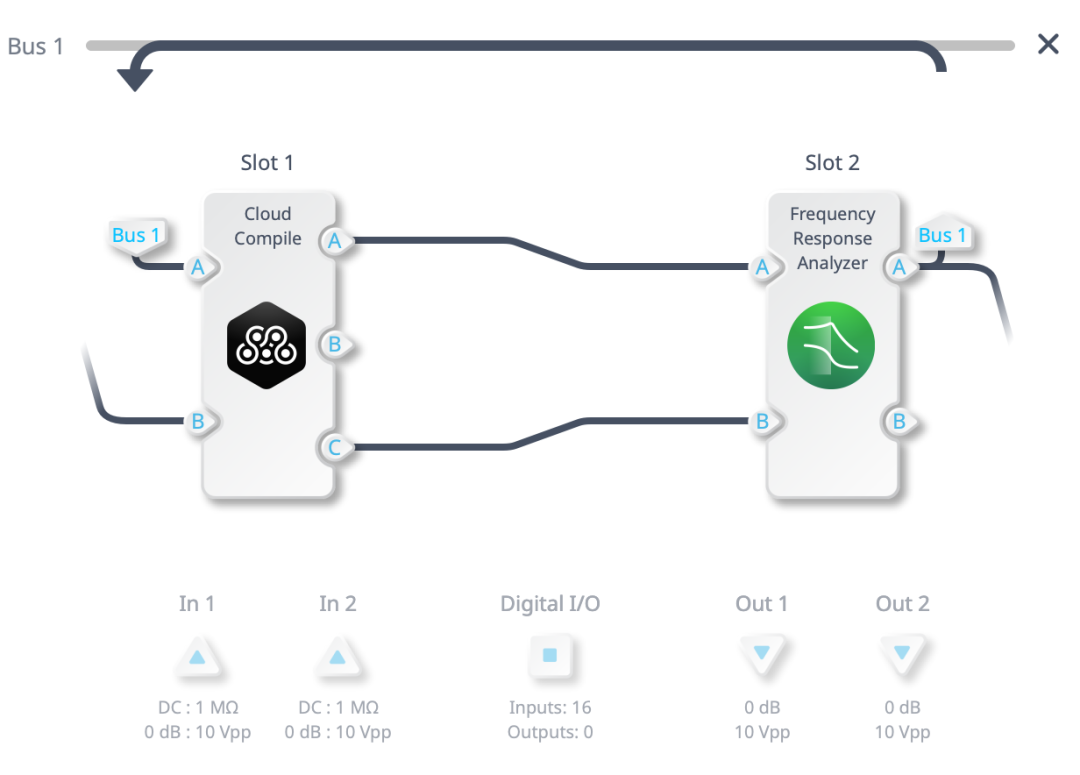

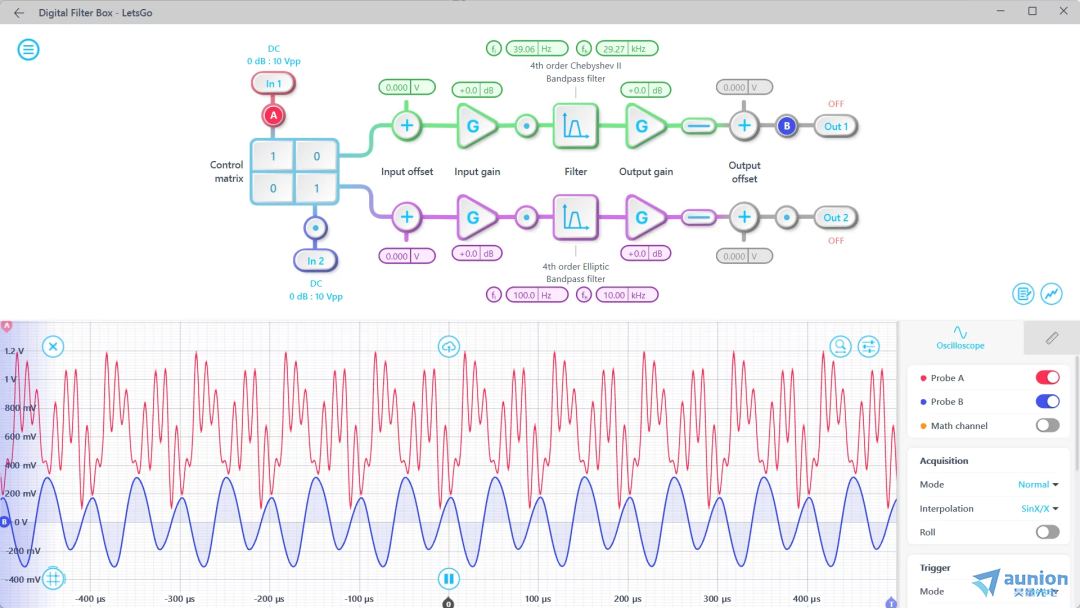

为了测试该移动平均滤波器,我们使用Moku:Go的多仪器模式(MiM),如图5所示。在此模式下,我们可以部署两台采样率为31.25 MHz的仪器。我们同样可以在Moku:Pro,Moku:Lab上测试该滤波器。

插槽1插入MCC移动平均滤波器,插槽2插入示波器仪器。我们使用示波器观察从输入1输入的的已滤波和未滤波信号。示波器还具有一个集成波形发生器,用于生成测试信号。在本例中,我们使用示波器的内置波形发生器生成2 kHz 的方波,并将其连接到输出1。我们在外部将信号衰减 60 dB,使其接近Moku:Go的本底噪声。然后我们将该信号路由回输入1。

图 5:多仪器模式下的滤波器测试设置

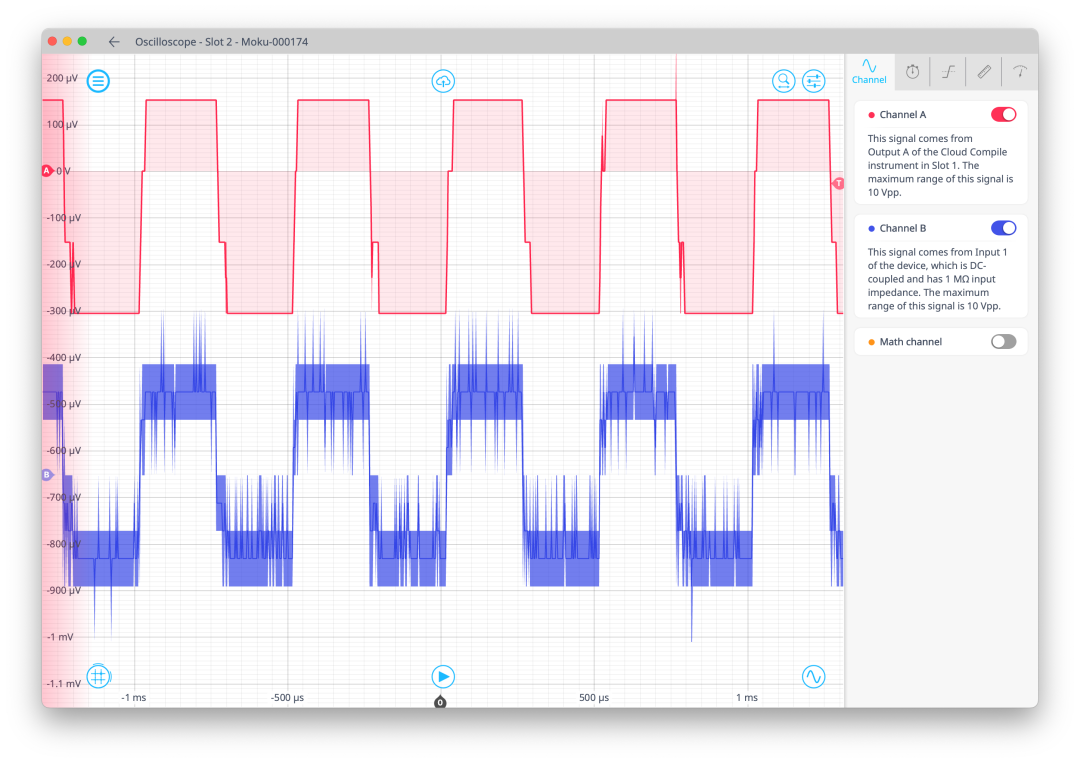

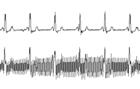

在图6中,我们可以在蓝色轨迹中看到衰减后的噪声方波。红色迹线显示移动平均器的输出,具有明显更干净的方波。这是一种十分有效的降噪技术,我们使用了MiM,并在一个插槽启用了MCC功能。

现在我们转为关注噪声功率,我们知道该平均滤波器将噪声功率降低了2N倍;噪声幅度降低了2N/2。我们的实现使用N=8,因此噪声幅度应减少到原始值的6.25%(1/16)。

因此,这种最简单的滤波器对于降低噪声很有用。它的计算量也非常小,只需要累加器、减法器和按位移位。这意味着它可以以非常高的速度运行,在 Moku:Pro 上为 312.5 MSa/s,在 Moku:Go 上为 31.25 MSa/s。

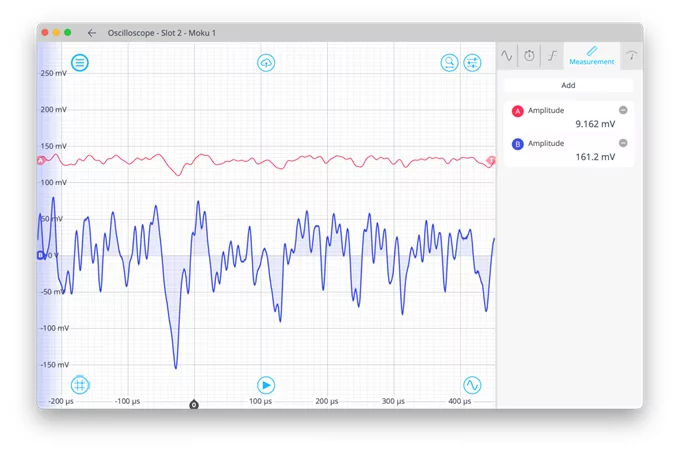

图7显示了 Moku:Go 输入噪声(蓝色线)和幅度分别为161.2 mV和9.162 mV的移动平均滤波器信号(红色线)。由此我们可以看出,滤波器后的噪声幅度接近于原始噪声的预期因子1/16,即 9.162161.2 = 0.057。该过滤器正在运行并满足我们的期望。

图7输入噪声与滤波后信号

频率响应

我们可以使用Moku频率响应分析仪(FRA)仪器轻松确定移动平均滤波器的频率响应。FRA在其输出上驱动扫频正弦波,并测量其输入上产生的幅度和相位。图8显示了测试设置:

图 8:频率响应分析仪设置

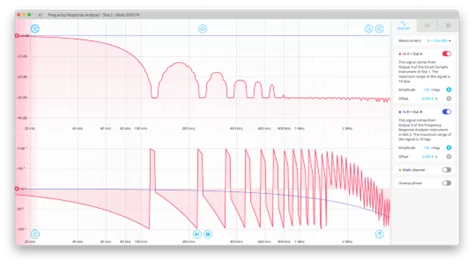

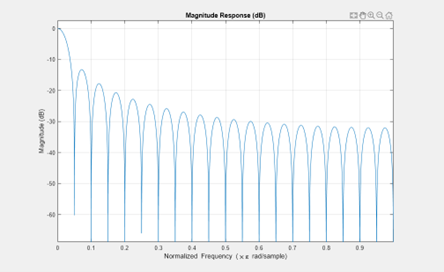

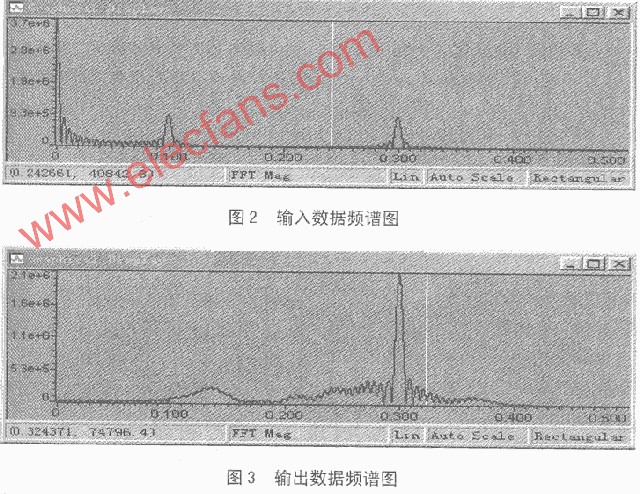

图9显示了MCC滤波器的频率响应结果。与图10(理想移动平均滤波器的MATLAB图)相比,我们发现移动平均滤波器没有提供特别好的阻带衰减。

图9移动平均滤波器的频率响应

图10理想移动平均滤波器的MATLAB图

中值滤波器

中值滤波器是一种非线性滤波器,用于确定小移动窗口的中值。输入样本通过窗口,输出给定任何时间样本的中值。移动平均滤波器适合过滤均匀分布的随机噪声,中值滤波器适合滤除非常短的尖峰或脉冲噪声。虽然它经常部署在图像处理中,但它在更一般的信号处理中也很有用。

通常,为窗口长度选择奇数个样本:3、5或7个点。这意味着输出只是值排序窗口的中间样本。

VHDL实现

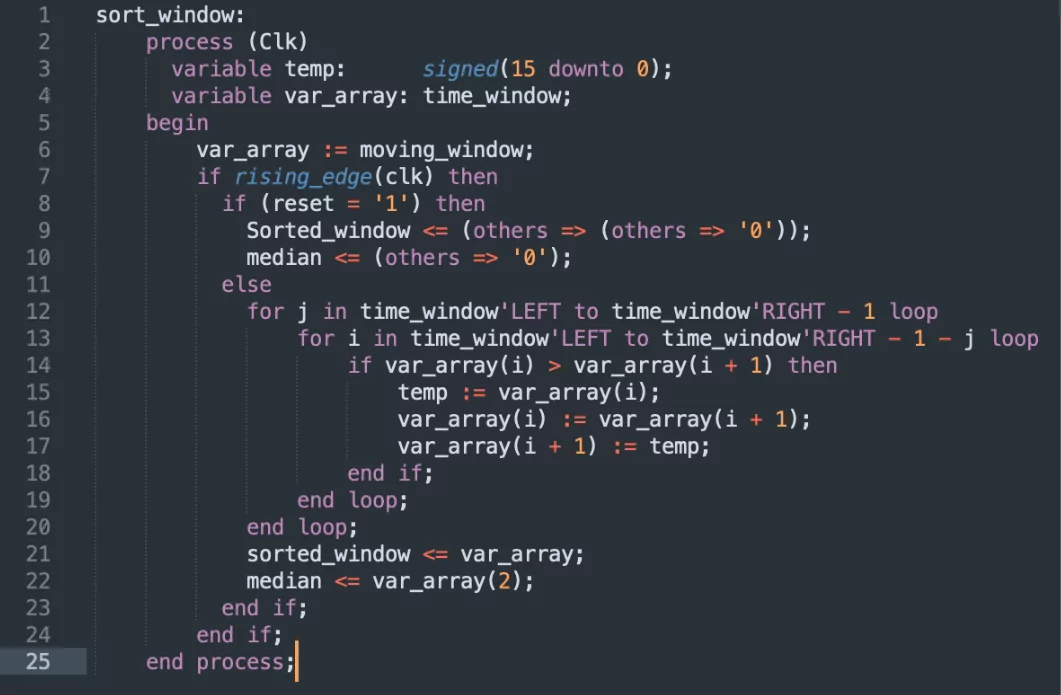

图11显示了VHDL五点中值函数的实现。在时钟信号的每个上升沿,图11中的函数将五个输入样本从低值到高值排序。这种排序发生在第12行到第20行的两个嵌套“for”循环中。因此,中位数是排序窗口中的第三个样本;这被分配给第22行的输出。

图 11:中值VHDL代码

我们可以使用示波器和云编译器插槽以及示波器的波形生成器,以与移动平均滤波器相同的方式分析中值滤波器的时域性能。

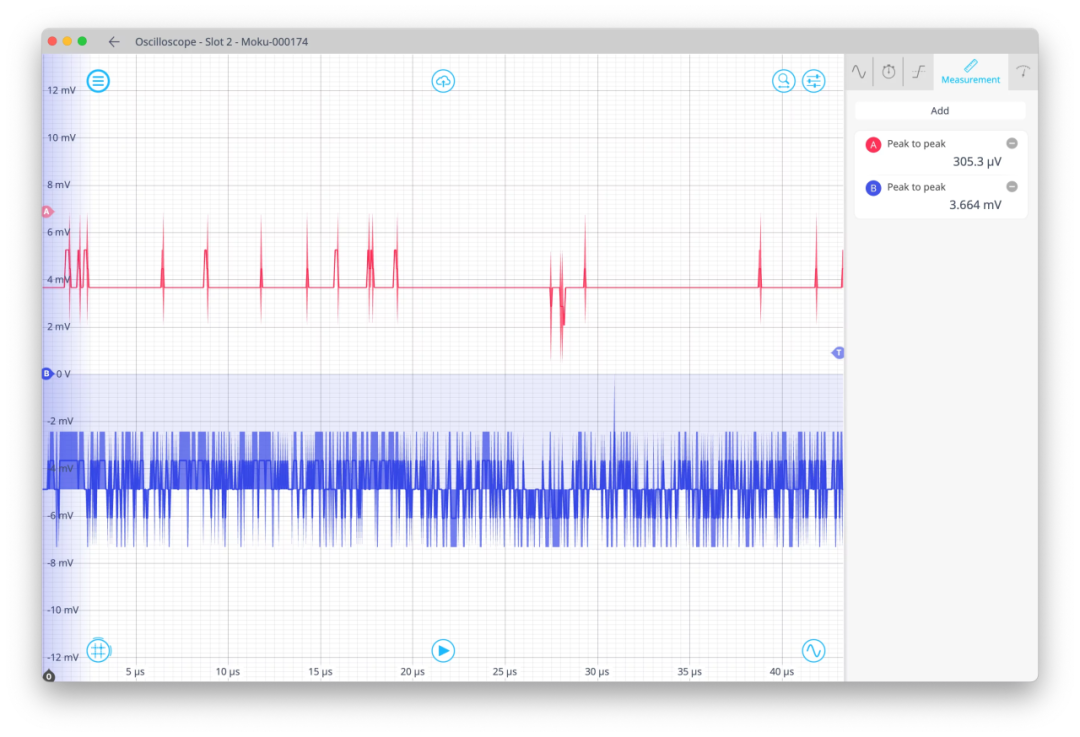

图12显示噪声峰值显着降低,未滤波噪声的峰峰值测量值从 3.66 mV 降低至滤波后的305 μV。这减少了1/12,不如移动平均滤波器(1/16)有效。

图12中值滤波器时域性能

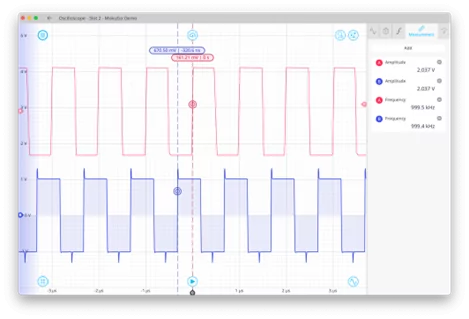

由于中值滤波器的一个关键功能是消除脉冲噪声,因此我们还使用带有附加脉冲的方波来检查其性能。图13显示了具有前沿尖峰和低电平中途尖峰的方波(蓝色线),滤波信号显示中值滤波器去除尖峰后的方波(红色线)。

图13去除尖峰噪声的中值

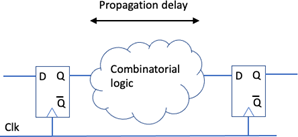

我们在Moku:Go上编译并测试了这个中值滤波器,它的MCC时钟速率为31.25 MHz。然而,在为Moku:Pro测试此示例时,由于时钟速率增加到312.5 MHz,我们需要调整我们的示例。图 11 中的实现使用带有变量的嵌套 for 循环。这合成了一个复杂的组合逻辑网络,其转递延迟(图14)超过了Moku:Pro时钟速率的3.2 ns周期。为了满足时序要求,时钟元件之间的逻辑转递延迟必须小于时钟周期。

图 14:通过逻辑的传递延迟

我们需要将大型逻辑块分成由寄存器或时钟元件分隔成段。在VHDL中,我们通过使用信号而不是变量来实现这一点。在本例中,为了便于编码,我们将逻辑分为五个阶段。这意味着输入到输出的延迟约为五个时钟周期,这适合我们的应用程序。

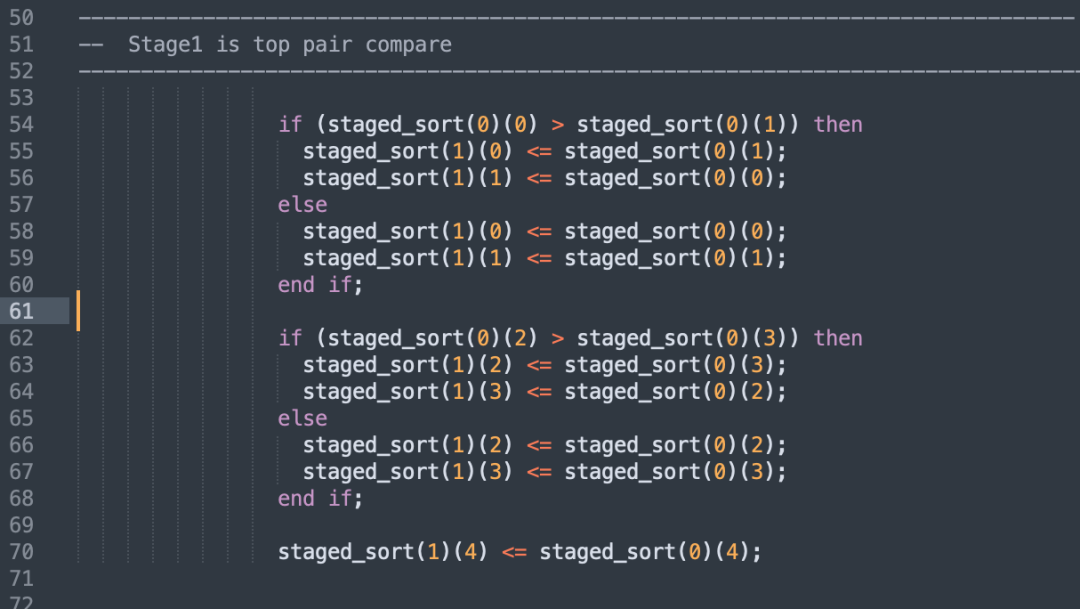

图15显示了该五阶段线性中值算法的一个阶段。可以在此处下载的项目文件中找到完整的VHDL:https://gitlab.com/liquidinstruments/cloud-compile/examples

图15VHDL代码部分示例

Moku:Pro

中值滤波器测试

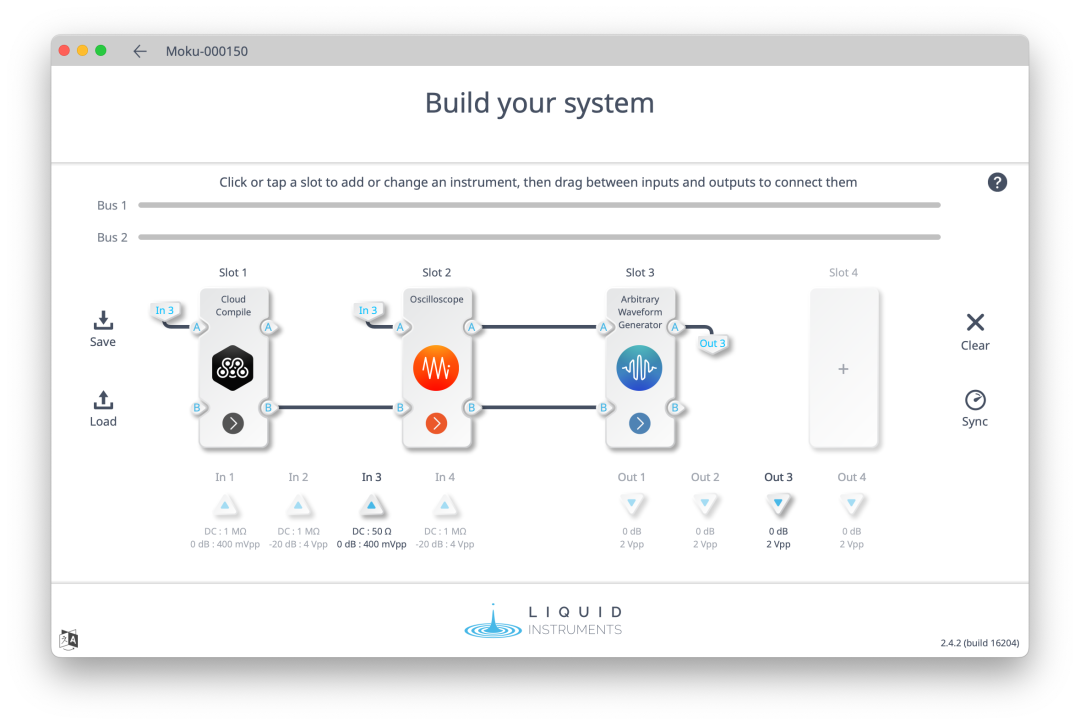

我们使用MiM中的Moku:Pro和任意波形发生器(AWG)来创建带有噪声尖峰的方波。然后,我们将AWG的输出连接到MCC中值滤波器,并使用示波器观察效果。

此MiM设置如图16所示。我们配置了AWG,如图17所示。它的输出将模拟信号驱动到Moku:Pro的输出 3,而该信号又通过同轴电缆环接到输入3。中值滤波器部署在MCC中,并使用示波器来观察性能。

图16Moku:Pro中值滤波器测试系统

图17任意波形发生器,带有脉冲的方波

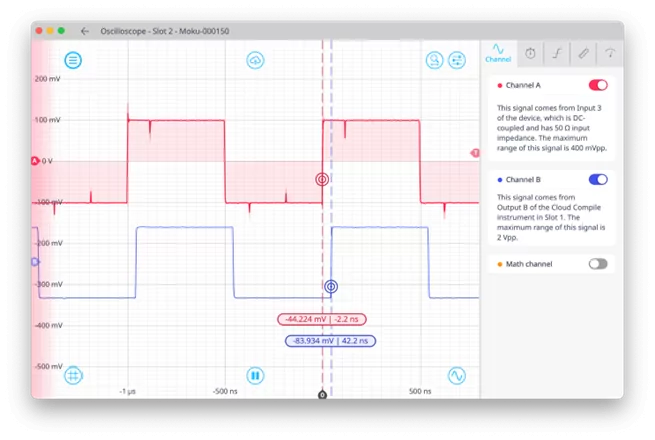

最后,我们观察中值滤波器的性能,如图18所示。中值滤波器消除了尖峰,同时保留了方波的尖锐边缘。由于插入分级时钟线程而导致的处理延迟导致大约44 ns的延迟。

图 18:Moku:Pro中值滤波器现象

总结

在本应用笔记中,我们讨论了移动平均滤波器和中值滤波器的实现。为了实现这些,我们利用Moku Cloud Compile来构建过滤器并将其部署到Moku:Go。然后我们修改了设计以确保与增加的Moku:Pro时钟速率兼容。为了验证MCC滤波器,我们使用多仪器模式连接完全可定制的滤波器、示波器和任意波形发生器。这种实现方式可以有效降低噪声,同时保留数字信号处理应用中的信号边缘。

-

示波器

+关注

关注

113文章

7120浏览量

196790 -

数字滤波器

+关注

关注

4文章

300浏览量

48394 -

FIR

+关注

关注

4文章

152浏览量

35673

发布评论请先 登录

使用FPGA构建的数字滤波器设计方案

LabVIEW如何实现数字滤波器的设计

数字滤波器,数字滤波器原理是什么?

数字滤波器的MATLAB与DSP上设计实现

基于LabVIEW的数字滤波器设计过程

如何使用FPGA实现IIR数字滤波器的设计

FIR数字滤波器设计

Moku:Go中的数字滤波器、FIR滤波器生成器和锁相放大器

使用Moku自定义实时数字滤波器实现降噪与去尖峰

使用Moku自定义实时数字滤波器实现降噪与去尖峰

评论