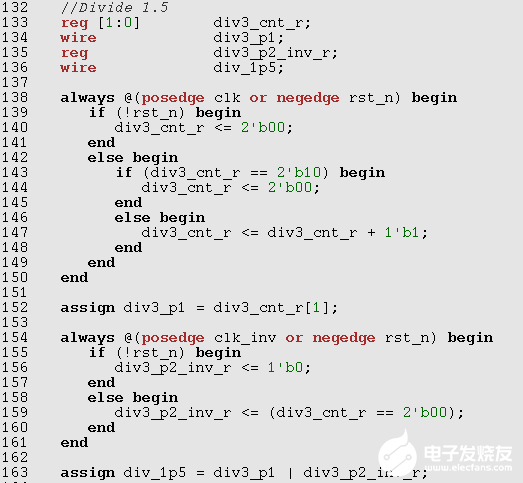

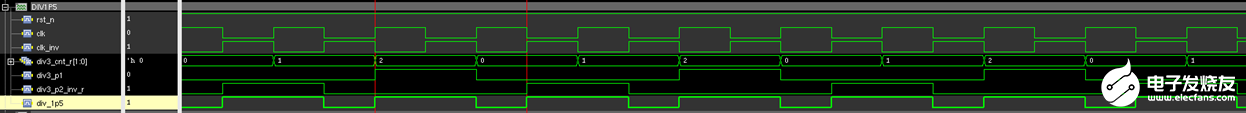

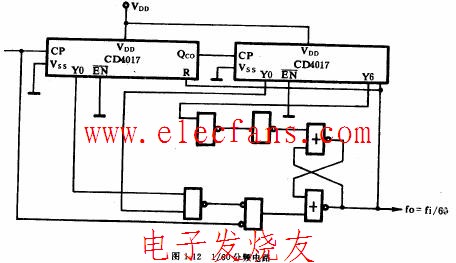

思路很简单,在3个周期里产生两个脉冲,等效于分频1.5。

第一个脉冲很容易实现。计数器2’b00 -- 2’b01 – 2’b10无限循环,最高位就是每三个周期出现一次的脉冲。第二个脉冲要用到一个negedge DFF。两个脉冲OR一下,输出就是1.5分频。

下面是Verilog RTL及波形。

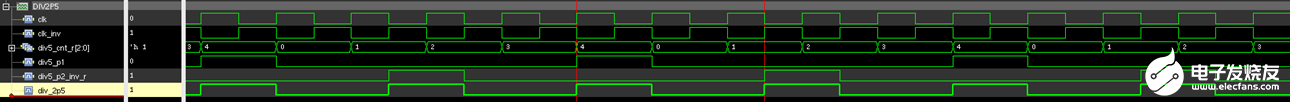

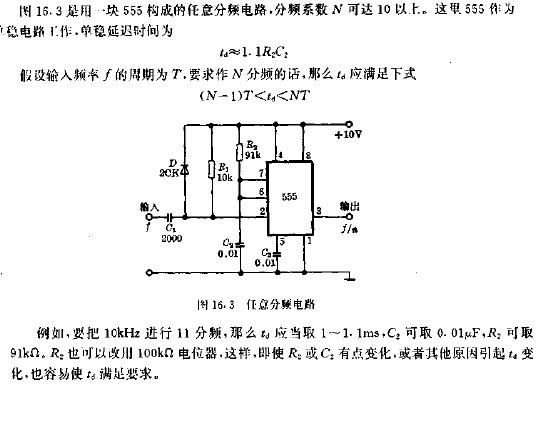

2.5分频

一样的思路,5个周期产生两个脉冲就可以了。

其他x.5分频可以按同样的思路类推。

这种分频后的输出有几个“缺陷“,使用的时候要注意。

-占空比无法做到50-50。

-分频输出有一点jitter。Jitter来自于两个脉冲上升沿相对于原始时钟的上升沿下降沿,delay是不一样的。原始时钟本身上升沿下降沿的jitter会叠加在上面。

要求不高的场合,这种数字逻辑实现的小数分频输出可以当作时钟用。Jitter要求高的场合,还是要用PLL实现。

审核编辑:黄飞

-

pll

+关注

关注

6文章

976浏览量

137587 -

计数器

+关注

关注

32文章

2306浏览量

97571 -

分频

+关注

关注

0文章

254浏览量

25277 -

数字逻辑

+关注

关注

0文章

74浏览量

17369 -

数字前端

+关注

关注

0文章

12浏览量

7946

发布评论请先 登录

数字前端设计的x.5分频实现思路

数字前端设计的x.5分频实现思路

评论