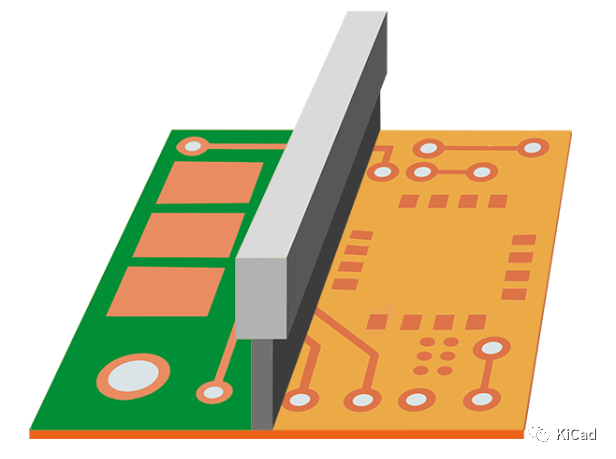

阻焊层可以封住PCB,并在表面层的铜上提供一层保护膜。阻焊层需要从表面层的着陆焊盘拉回,这样您可以有一个可供安装和焊接元件的表面。从顶层焊盘上移除阻焊层,应该会围绕焊盘边缘延伸一定距离,从而为您的元件创建NSMD或SMD焊盘。

应该将阻焊层扩展拉回多远,以防止装配缺陷并确保有足够的焊接区域?事实证明,随着越来越小的元件和更高密度的布局成为常态,阻焊层扩展会产生小的阻焊层碎片,这些碎片将留在表面层上。在某些时候,最小的可允许阻焊层碎片和所需的阻焊层扩展成为竞争性设计规则;您可能无法同时满足这两个规则。

平衡阻焊层扩展与碎片

周边焊盘尺寸与错位公差

这是应用正阻焊层扩展的主要原因,它会创建一个非阻焊层定义(NSMD)焊盘。这样做的理由与铜蚀刻过程有关;铜蚀刻是一种湿化学过程,具有比阻焊应用更高的精度。因此,为确保始终暴露整个焊盘区域,我们在焊盘周围应用了足够大的阻焊层扩展。

阻焊剂应用过程的精度较低,会造成错位问题,阻焊层与PCB布局中定义的位置不完全匹配。然而,如果阻焊层扩展足够大,它将补偿错位,焊盘仍然可以通过阻焊层完全可见。我见过的关于阻焊层扩展的最小建议是在焊盘的所有侧面上增加3密耳,这将补偿大约2密耳的错位。

此焊盘有少量阻焊层错位

如果您的焊盘已经足够大,会怎么样?在该背景下,您可以证明使用较小的阻焊层扩展值是合理的。在这种情况下,如果您使用带有较大焊盘的较小扩展,仍然可以确保有足够大的暴露焊盘区域,即使存在一些错位问题。无论如何,您还必须考虑附近的焊盘/过孔之间是否需要设置焊接屏障。

最小焊料屏障尺寸

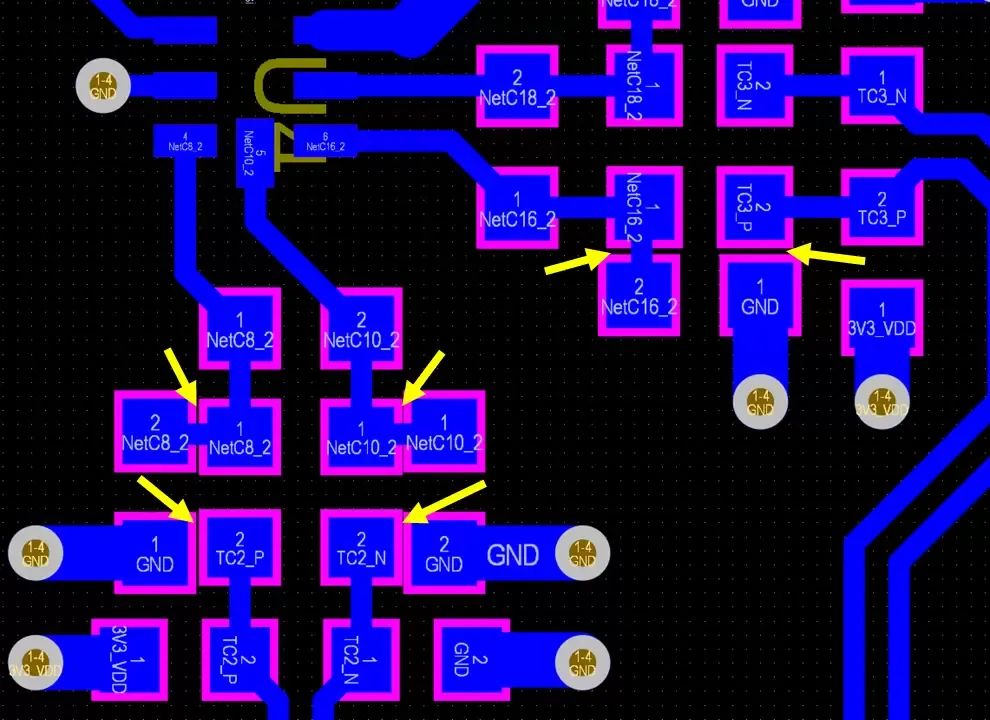

最小阻焊碎片尺寸将限制您可以应用于给定引线间距的阻焊层扩展开口。如果引线间距足够大,那么您始终可以应用较大的阻焊层扩展,而不必担心达到阻焊屏障限制。当引线间距变小时,或者当元件靠得很近时,您可能会违反最小阻焊碎片尺寸。在这种情况下,您需要决定是希望补偿错位还是确保始终存在一些阻焊屏障。在细间距元件方面,我更喜欢后者。

这些位置将违反模式制造商对最小焊料屏障尺寸的限制。在用于不同元件的焊盘之间应用一些额外间距,可以防止装配缺陷。

因为阻焊层网需要至少大约3密耳才能粘附到PCB基板表面,所以当焊盘间距为20密耳或更高时,您通常可以在焊盘周围适配最小的阻焊层扩展。如果您正在查看内部引线(例如BGA封装上的内部球),则应使用SMD焊盘并在焊盘和过孔之间放置小型屏障。

是否应该让制造厂决定?

如果您只是设置综合的设计规则并应用0密耳或1密耳扩展以达到密度要求,则您的制造商可能会应用额外的扩展值。如果他们这样做,他们可能不会告诉您;您应该预料到晶圆厂可能会如此应用以克服阻焊层模板和表面层焊盘之间的错位。

我的首选是在大多数项目中将掩膜设为0密耳,原因有两个:

除非我处理的是非常高密度的布局,否则我们用于大多数元件的封装将具有足够大的焊盘,典型的错位量不会显着减少焊盘上的焊接面积。

我已经知道制造商会增加阻焊层的扩展,因为我与有限数量的制造商合作;我知道他们的制造过程,当他们向我发送DFM报告时,我将有机会准确检查他们想要修改的内容。

第2点应该说明您应有一组首选制造/装配公司的原因,并且您应该了解他们的制造过程。我的公司有几个制造伙伴,我们专门用于中低批量的客户项目。我们知道他们的期望以及我们在初始DFM/DFA审查后可能收到的反馈。

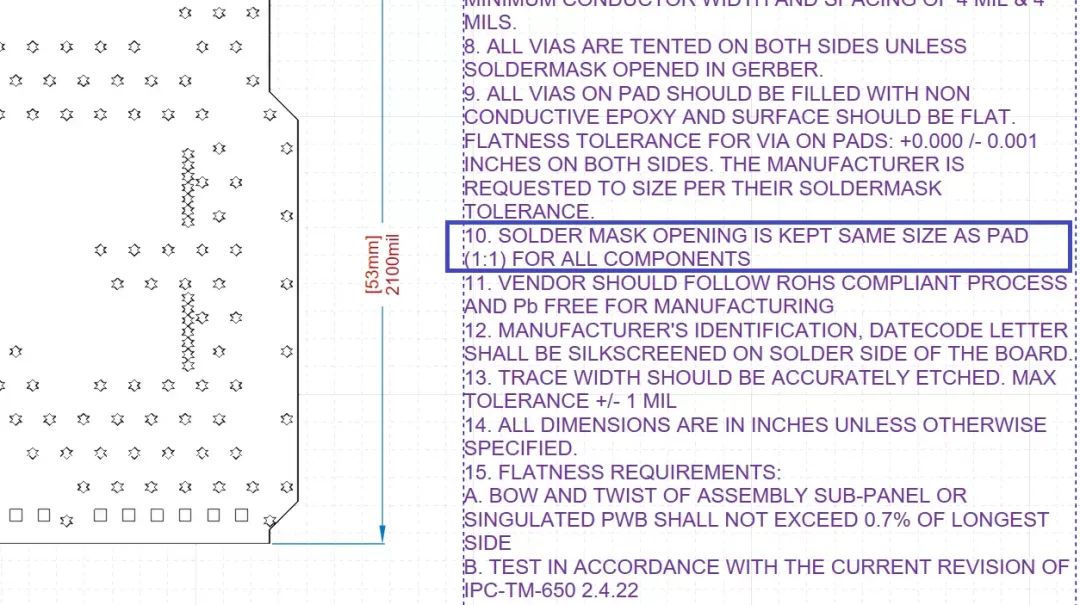

如果您想真正将您的意图传达给制造商,请在您的制造图纸中明确说明您的意图。在制造图纸中添加注释,说明制造商有权在一定范围内(可能是+/-3密耳)修改阻焊剂开口。另一种选择是在阻焊层扩展上设置一个指定的公差,然后指定一个最小碎片宽度。请注意,如果您的要求过高,他们可能会将电路板退还给您,此时您可能需要放宽容忍度要求。

这些制造说明中的注释10指定了我在此设计中能够容忍的阻焊层扩展程度。在这种情况下,我已指定首选的阻焊层开口以匹配焊盘尺寸。

确定防止装配问题所需的最小阻焊层扩展和碎片后,您就可以使用Altium Designer®中的CAD工具来定义焊盘图案和封装。您和您的团队将能够通过Altium 365™平台在先进的电子设计方面保持多产和高效协作。您可以在一个软件包中找到设计和生产高级电子产品所需的一切。

审核编辑:汤梓红

-

pcb

+关注

关注

4391文章

23742浏览量

420756 -

元件

+关注

关注

4文章

1212浏览量

38462 -

阻焊层

+关注

关注

2文章

54浏览量

11706 -

SMD焊盘

+关注

关注

0文章

3浏览量

4978

发布评论请先 登录

PCB中阻焊层设计规则

PCB中阻焊层设计规则

评论