描述

理想开关的打开(关闭或停用)关闭(打开或激活)由施加在开关控制端子上的控制信号控制,用户可以根据阈值电平和滞后定义的操作区域进一步提高可控性。

具有阈值和滞后的开关通常用于开关应用中,以避免系统振荡。它们有助于减少具有机械负载(泵或电机)的系统不稳定性并减少磨损。它们通过启用稳定的控制回路来帮助提高系统的可靠性。

在理想的开关中,开关的电阻是根据其工作状态选择的。在导通状态期间,开关的电阻将非常低,因此满载电流流过开关,同时在器件上施加的压降最小。在关断状态期间,开关的电阻将非常高,因此流过开关的电流非常低,并且在开关两端施加了全压降。

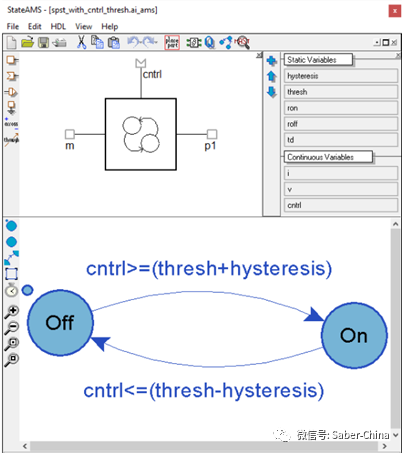

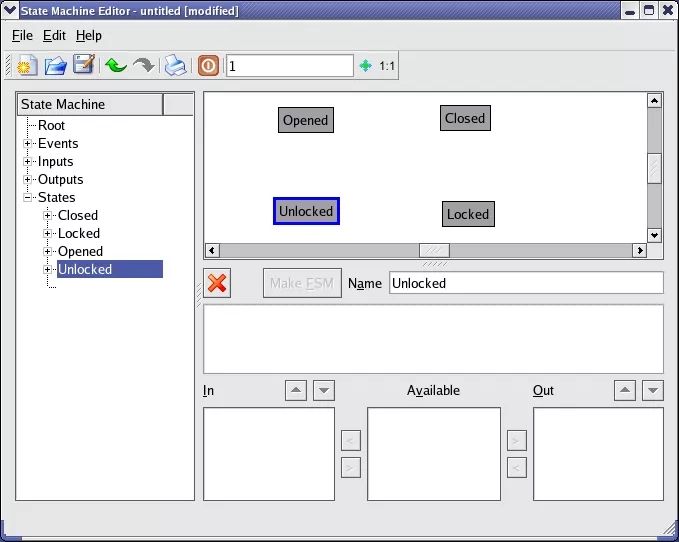

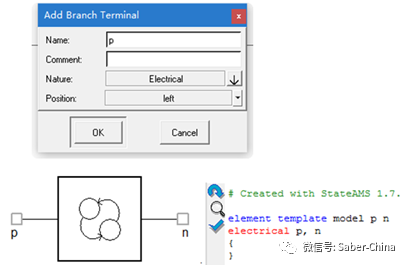

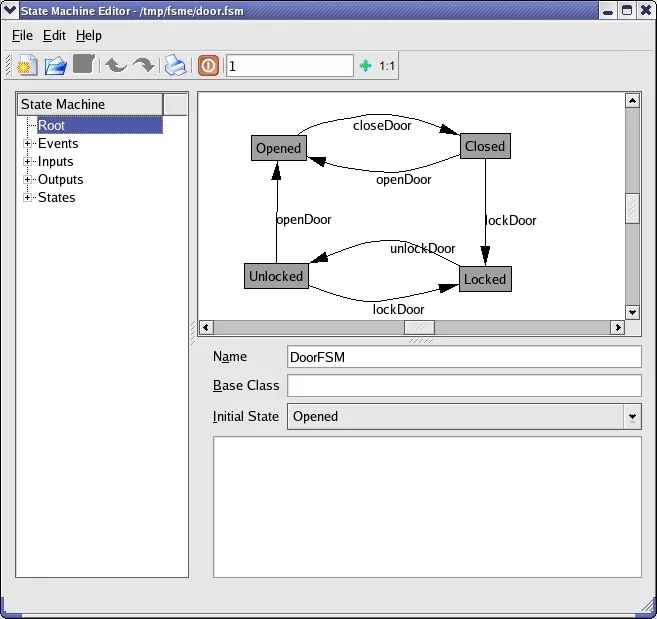

使用SaberRD中的StateAMS状态机建模工具直观地对具有阈值和滞后的理想开关进行建模。StateAMS 工具允许从基于状态图和方程的独立于语言的描述中创建混合信号有限状态机模型。有关详细的建模技术,请参阅工具帮助文档。

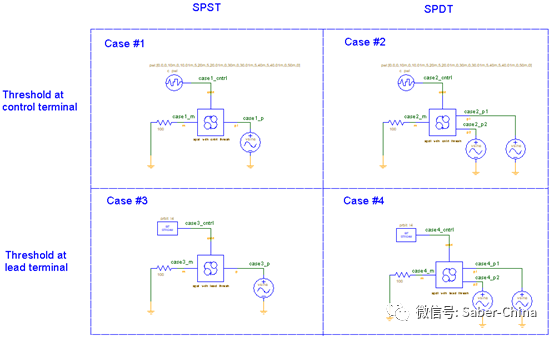

您可以根据您的应用设计不同类型的开关。本文描述了四种不同的用例。

Case 1 - 单刀单掷开关在控制终端进行阈值检查

Case 2 - 单刀双掷开关在控制终端进行阈值检查

Case 3 - 单刀单掷开关在引线端子处进行阈值检查

Case 4 - 单刀双掷开关在引线端子处进行阈值检查

向下滚动到每个用例以了解使用 StateAMS 建模工具实现的开关行为和建模技术。

文后提供了test_design.zip示例下载,使用示例中提供的测试设计文件和实验测试文件,可以验证上述四种不同开关的实现。在SaberRD中打开测试设计test.ai_dsn,下图1是四种案例的电路原理图,运行实验测试文件 test_bench.ai_expt即可。

1、Case 1

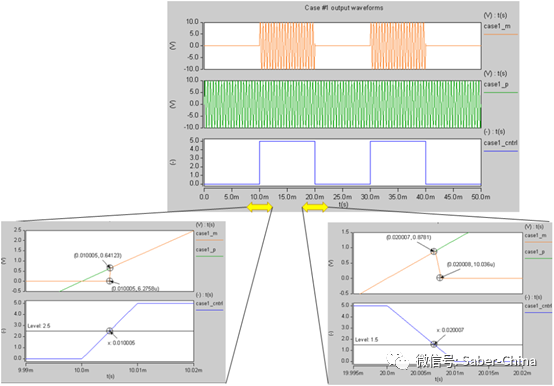

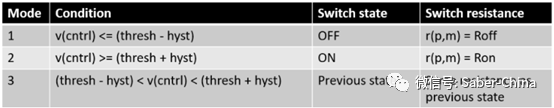

单刀单掷开关 (SPST) 是通过控制终端提供的阈值检查创建的。SPST开关常开。当控制信号值 v(cntrl) 变得大于或等于提供的阈值和滞后的总和 (v(cntrl) >= (thresh + hyst)) 时,开关闭合。表1给出了在控制端带有阈值检查的SPST的不同操作模式。

在模式3中,当控制信号值落在这两个检查点之间,即 ((thresh - hyst) < v(cntrl) < (thresh + hyst)) 时,开关将根据之前的状态保持打开或关闭施加控制信号的开关。例如,假设开关闭合(ON 状态),即 (v(cntrl) >= (thresh + hyst))。

现在,要打开开关(关闭),控制信号电平必须小于或等于 (thresh-hyst)。因此,直到控制信号电平从 ON 状态下降到 v(cntrl) <= (thresh - hyst) 的电平之前,开关仍像之前的状态一样处于 ON 状态。同样,一旦开关打开(OFF),开关将保持OFF,直到控制信号大于或等于(thresh+hyst)。

因此,当控制信号电平从关闭状态上升到 v(cntrl) >= (thresh + hyst) 的电平时,开关仍像之前的状态一样处于关闭状态。模式3的存在是由于模型中存在滞后。当滞后为零时,模式3不存在。

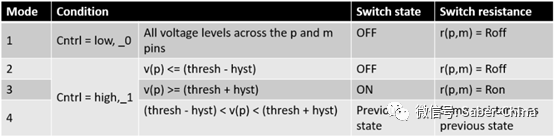

表1控制端带有阈值检查的SPST操作模式

下面是StateAMS 状态机模型。

下面是实验结果。仿真完成后,从结果窗格中打开图表 Case1。

2、Case 2

单刀双掷开关 (SPDT) 是通过控制终端提供的阈值检查创建的。SPDT 在p1端子处常闭 (NC),在p2端子处常开 (NO)。开关根据控制信号值切换p1和p2端子之间的连接。控制信号必须大于或等于(阈值 + 迟滞)才能使开关从p1切换到p2。

然后,控制信号值必须小于或等于(阈值 - 滞后),以便开关从p2切换回p1。表2给出了在控制终端进行阈值检查的SPDT的不同操作模式。模式3的存在是由于模型中存在滞后现象,如Case1 所述。

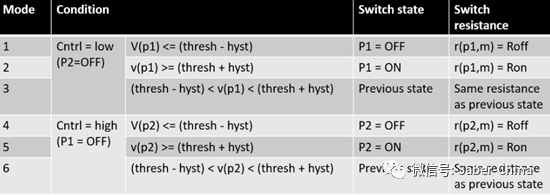

表2控制端带有阈值检查的SPDT操作模式

下面是StateAMS 状态机模型。

下面是实验结果,从结果窗格中打开图表 Case2。

3、Case 3

单刀单掷开关 (SPST) 是通过引线端子处提供的阈值检查创建的。除了提供的控制信号外,该模型还会在关闭和打开开关之前检查 p 端子的阈值电平。

在此模型中,控制端子是数字的,必须由数字源驱动。只有当控制信号为高电平或l4_1,且p端电压大于等于(thresh+hyst)时,开关才闭合。表 3 给出了在 p 端进行阈值检查的 SPST 的不同操作模式。模式 4 的存在是由于模型中存在滞后,如案例 #1 的模式 3 中所述。

表3在 p 端进行阈值检查的SPST的不同操作模式

下面是StateAMS模型。

注意:L4_0和l4_1等MAST数字值在StateAMS建模工具中分别表示为“0”和“1”。

下面是实验结果,从结果窗格中打开图表 Case3。

4、Case 4

单刀双掷开关 (SPDT) 是通过引线端子处提供的阈值检查创建的。除了提供的控制信号外,模型还会在切换连接之前检查p1和p2端子的阈值电平。

在这个模型中,控制端是数字的,它必须由数字源驱动。该模型的初始状态是在p1和p2端常开。表4给出了在引线端子处进行阈值检查的SPDT的不同操作模式。模式3和6的存在是由于模型中存在滞后现象,如Case1中模式3所述。

表4在引线端子处进行阈值检查的SPDT的不同操作模式

下面是StateAMS模型。

注意:L4_0和l4_1等MAST数字值在StateAMS建模工具中分别表示为“0”和“1”。

从结果窗格中打开图表 Case4查看结果:

-

SPST

+关注

关注

0文章

55浏览量

12146 -

有限状态机

+关注

关注

0文章

52浏览量

10691 -

状态机

+关注

关注

2文章

501浏览量

29335

发布评论请先 登录

有限状态机的建模与优化设计

用状态机原理进行软件设计

什么是状态机?状态机5要素

自动生成程序状态机代码状态机建模方法

如何使用StateAMS状态机对具有阈值和滞后的理想开关进行建模?

如何使用StateAMS状态机对具有阈值和滞后的理想开关进行建模?

评论