每次作为面试官问一些RTL功耗优化的问题时候,都会希望听到一个答案:优化了RTL的clk-gating比例。

相传在很多年前,时序逻辑中是不存在自动时钟门控(clk-gating)的。那个时候我还小没赶上,如果我们回家问问家大人的话,他们会告诉我们那时候流行的D触发器综合应该是这样的:

这种结构呢在没有使能的情况下,触发器的D端是不会有信号跳变的,能够有限的降低一些功耗。不过大家也清楚寄存器的动态功耗主要来源于时钟的跳变,因此这种综合结果下时钟信号保持翻转,触发器的内部电路也大多保持活跃,于是后面进一步的出现了自动时钟门控结构。

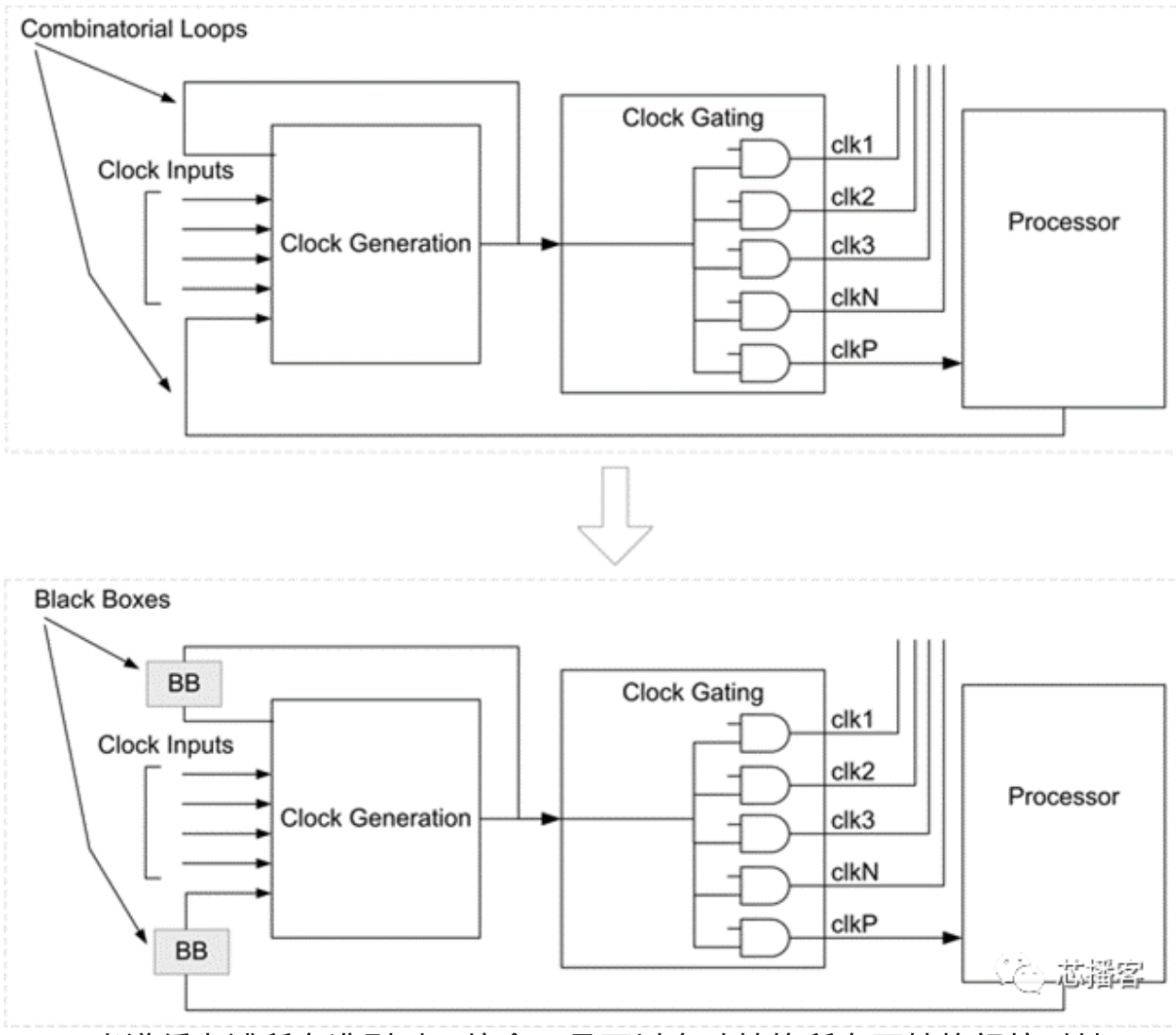

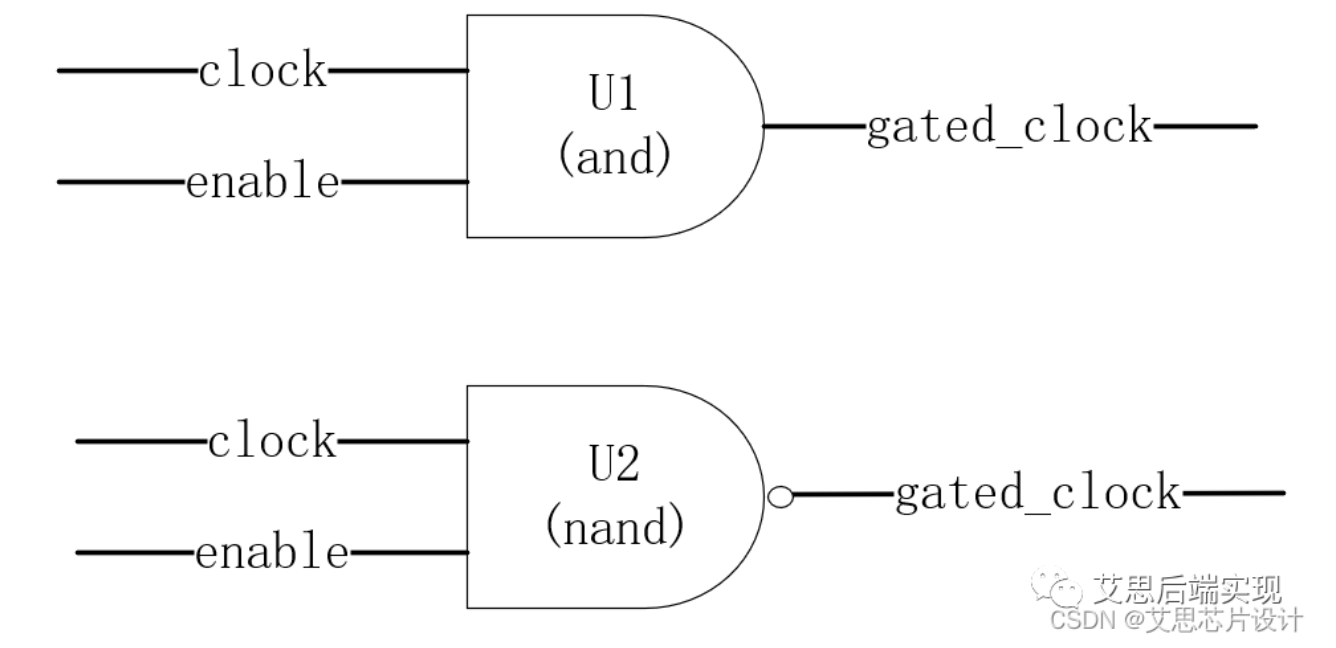

什么是自动时钟门控结构呢?就是通过工具自动的插入一些结构,能够在数据不跳变的时间里,关断寄存器的时钟输入。那么如果来做一个最简单的门控结构,那必然就是如此了:

当使能为低时,D触发器的时钟被关断,没有时钟跳变自然寄存器也不会翻转,因此Q端也不需要连线回接到D端来实现数据保持。不过这样的结构存在一个明显的问题,en信号显然是逻辑电路生成的,虽然其必然满足建立时间和保持时间要求,但是当en信号维持时间过短时,时钟会被过早的关断:

以及en的逻辑跳变引起的时钟脉冲和毛刺:

因此呢就出现一个需求,作用在clk上的en信号必须要能在时钟上升沿到时钟下降沿这个区间保持为一个常量,所以进一步的我们引入一个锁存结构:

clk信号作为锁存器的控制端,en信号为被锁存信号,当clk为1时锁存en信号,clk为0时透传en信号,对应的波形如下:

通过锁存器的锁存功能,en信号只要在上升沿前保持稳定,即可保证产生完整的时钟脉冲,这个结构就已经基本满足我们的需求了。此外,大部分的厂商会在标准单元库中提供“时钟门控单元”,比上面的结构会多一个test_se信号,在扫描测试时候使用,因此一个完成的gating结构大体是这样的:

而最终一个插入了自动时钟门控的D触发器的门电路结构图也就完成了:

那么完成了clk-gating结构后我们需要分析一下,clk-gating的收益是什么呢?功耗收益,能够在EN端不使能时关断时钟降低寄存器的动态功耗。那么对应的额外消耗支出有哪些呢?

1.面积增加,与门、或门和latch都是会增加面积的,因此工具不会无脑的插入gating,一般只有在EN控制的寄存器超过4bit时才会插入,这个值是可以设置的;

2.EN路径的时序更加紧张,为了保证时钟及时被开启,EN端必须更早的实现时序收敛(或者理解为EN路径是相对clk的,D路径是相对gating clk的)。关于这一点综合完的clk timing.rpt和clk gating timing.rpt对比下就会发现gating的timing路径中一般会减去一个时间比如-100ps;

最后再解答还是经常在面试里问的问题:为什么时序逻辑里不写else工具才能自动插入时钟门控呢?

通过观察结构就可以发现,时钟门控的结果就是当EN不使能时Q端数据不发生改变,如果else分支里有赋值,那么天然就不满足这个条件了,因此工具无法插入时钟门控。

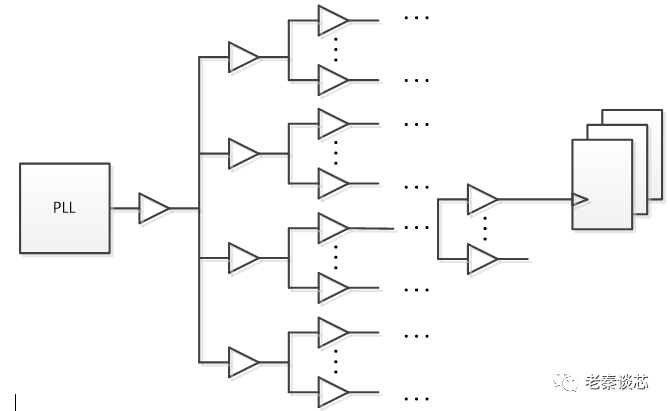

当然本篇所述是在触发器级的自动时钟门控,而整体看门控时钟可以处于整个时钟树的任何节点,越靠近根部的门控时钟对于降低功耗的作用越明显。原因显而易见,整个电路结构的功耗整体由三部分组成:组合逻辑产生的功耗+触发器产生的功耗+时钟树功耗;靠近根部的门控结构不仅降低了大量触发器的功耗,同时降低了区域的时钟树功耗(时钟树功耗几乎占到了芯片功耗的50%)。

-

寄存器

+关注

关注

31文章

5589浏览量

129065 -

RTL

+关注

关注

1文章

393浏览量

62394 -

触发器

+关注

关注

14文章

2051浏览量

63043 -

CLK

+关注

关注

0文章

132浏览量

17933 -

时钟门控

+关注

关注

0文章

8浏览量

7036

发布评论请先 登录

fpga门控时钟问题

什么是时钟门控?如何去实线时钟门控的设计呢

门控时钟与时钟偏移研究

什么是自动时钟门控结构呢?关于自动时钟门控的解析

什么是自动时钟门控结构呢?关于自动时钟门控的解析

评论