1 简介

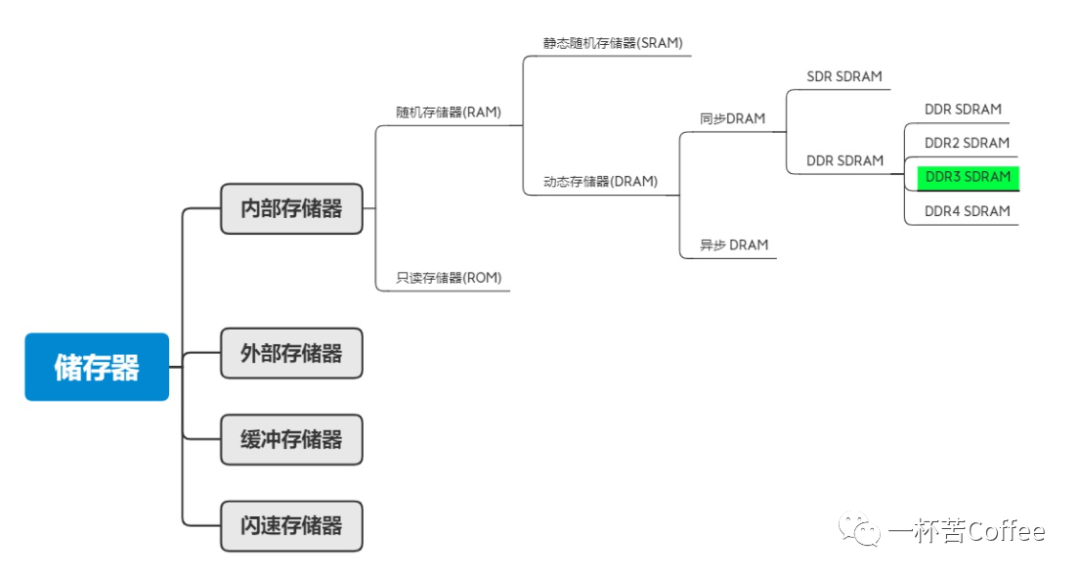

本文主要讲述一下DDR从0到1设计的整个设计的全过程,有需要的朋友可先安排收藏。内容涵盖以下部分:

DDR4级联

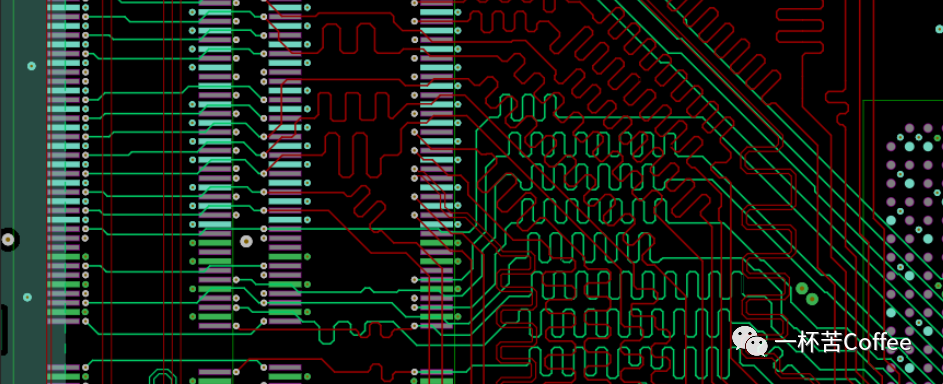

DDR4 Layout注意事项(内容太多,可能下一章节分享)

2 DDR4的级联

本节主要讲述DDR的级联,主要分为三个实战案例进行讲解,分别是2片16位DDR4级联、4片16位DDR4+1片8位DDR4级联、两组5片16位DDR4级联。相信通过本章节的讲解,大部分朋友都会对DDR的级联有一个深刻的认识。

2.1 2片16位DDR4级联

选用的DDR芯片是镁光的MT40A256M16GE-083E,2片16位DDR4级联,每个颗粒的位宽位16bit,级联的示意图见下:

16位DDR4颗粒1电路图如下:

16位DDR4颗粒1电路图如下:

总结:

两个16位DDR4颗粒级联时,地址线完全复用,具体包括地址线A[13:0]、BA[1:0]和BG0,地址线需要39.2Ω,精度1%电阻上拉至VTT,每个上拉电阻附近需要放置一个0.1uF电容,且VTT需要有uF级别大电容。

两个16位DDR4颗粒级联时,控制线完全复用,具体包括写保护(WE_B)、行选通信号(RAS_B)、列选通信号(CAS_B)、复位信号(RESET_B)、片内短接信号(ODT)、片选引脚(CS)、激活信号(ACT_B)、警告信号(ALERT_B)、奇偶检验信号(PAR),另外测试信号分别连接499Ω电阻至GND,警告信号(ALERT_B)需要上拉至1.2V。

两个16位DDR4颗粒级联时,时钟线完全复用,具体包括CK_T、CK_C、CKE,特别地,时钟信号需要连接36R,精度1%的电阻,然后串接0.01uF电容值1.2V;

注意:

这是一种末端短接匹配的一种方式(串始并末:串联端接一般放置在信号源端,并连端接一般放置在信号接收端)

直接上拉至主电源即可。

两个16位DDR4颗粒级联时,电源可以复用,具体包括VDD、VDDQ、VPP、REFCA,两个颗粒的ZQ信号需要分别连接240Ω电阻至GND。此处REFCA使用专用芯片产生:

所有的数据线均不复用,具体见下:

注意:HP BANK中LVDS的供电要求为1.8V;HR BANK中LVDS的供电要求为2.5V。

2.2 4片16位DDR4+1片8位DDR4级联

选用的DDR芯片是镁光的MT40A512M16LY-075E,其中4片16位DDR4+1片8位DDR4,总数据位宽高达72bit,级联的示意图见下:

16位DDR4颗粒1电路图如下:

16位DDR4颗粒2电路图如下:

16位DDR4颗粒3电路图如下:

16位DDR4颗粒4电路图如下:

8位DDR4颗粒5电路图如下:

总结:

两个16位DDR4颗粒级联时,地址线完全复用,具体包括地址线A[13:0]、BA[1:0]和BG0,地址线需要39.2Ω,精度1%电阻上拉至VTT,每个上拉电阻附近需要放置一个0.1uF电容,且VTT需要有uF级别大电容。

* 两个16位DDR4颗粒级联时,控制线完全复用,具体包括写保护(WE_B)、行选通信号(RAS_B)、列选通信号(CAS_B)、复位信号(RESET_B)、片内短接信号(ODT)、片选引脚(CS)、激活信号(ACT_B)、警告信号(ALERT_B)、奇偶检验信号(PAR),另外测试信号分别连接499Ω电阻至GND,警告信号(ALERT_B)需要上拉至1.2V。

* 两个16位DDR4颗粒级联时,控制线完全复用,具体包括写保护(WE_B)、行选通信号(RAS_B)、列选通信号(CAS_B)、复位信号(RESET_B)、片内短接信号(ODT)、片选引脚(CS)、激活信号(ACT_B)、警告信号(ALERT_B)、奇偶检验信号(PAR),另外测试信号分别连接499Ω电阻至GND,警告信号(ALERT_B)需要上拉至1.2V。

两个16位DDR4颗粒级联时,时钟线完全复用,具体包括CK_T、CK_C、CKE,特别地,时钟信号需要连接36R,精度1%的电阻,然后串接0.01uF电容值1.2V;

注意:

这是一种末端短接匹配的一种方式(串始并末:串联端接一般放置在信号源端,并连端接一般放置在信号接收端)

直接上拉至主电源即可。

两个16位DDR4颗粒级联时,电源可以复用,具体包括VDD、VDDQ、VPP、REFCA,两个颗粒的ZQ信号需要分别连接240Ω电阻至GND。此处REFCA使用电阻分压方式产生,这种放置最明显的优势是在布局时比较灵活:

- 所有的数据线均不复用,具体见下:

注意:

HP BANK中LVDS的供电要求为1.8V;HR BANK中LVDS的供电要求为2.5V。

最后一个颗粒的高8位数据线未使用,需要特别注意。

2.3 两组5片16位DDR4级联

这种级联方式与前面的有所不同,前面的级联方式不管多少颗粒都是同一组DDR,但是这种级联方式采用的是两组DDR设计,这种设计的方式看似比较复杂,其实两组DDR可以分开来进行分析,两组DDR完全独立,不存在复用的引脚。我们在进行电路分析时,只需要分析其中一组DDR电路即可。

16位颗粒1和颗粒2电路图见下:

16位颗粒3和颗粒4电路图见下:

16位DDR颗粒5电路图见下:

总结:

两个16位DDR4颗粒级联时,地址线完全复用,具体包括地址线A[13:0]、BA[1:0]和BG0,地址线需要39.2Ω,精度1%电阻上拉至VTT,每个上拉电阻附近需要放置一个0.1uF电容,且VTT需要有uF级别大电容。

两个16位DDR4颗粒级联时,控制线完全复用,具体包括写保护(WE_B)、行选通信号(RAS_B)、列选通信号(CAS_B)、复位信号(RESET_B)、片内短接信号(ODT)、片选引脚(CS)、激活信号(ACT_B)、警告信号(ALERT_B)、奇偶检验信号(PAR),另外测试信号分别连接499Ω电阻至GND,警告信号(ALERT_B)需要上拉至1.2V。

两个16位DDR4颗粒级联时,时钟线完全复用,具体包括CK_T、CK_C、CKE,特别地,时钟信号需要连接36R,精度1%的电阻,然后串接0.01uF电容值1.2V;

注意:

这是一种末端短接匹配的一种方式(串始并末:串联端接一般放置在信号源端,并连端接一般放置在信号接收端)

直接上拉至主电源即可。

两个16位DDR4颗粒级联时,电源可以复用,具体包括VDD、VDDQ、VPP、REFCA,两个颗粒的ZQ信号需要分别连接240Ω电阻至GND。此处REFCA使用电阻分压方式产生,这种放置最明显的优势是在布局时比较灵活:

所有的数据线均不复用。

注意:

HP BANK中LVDS的供电要求为1.8V;HR BANK中LVDS的供电要求为2.5V。

-

电路图

+关注

关注

10459文章

10749浏览量

551736 -

电路设计

+关注

关注

6732文章

2576浏览量

217984 -

DDR

+关注

关注

11文章

747浏览量

68531 -

DDR4

+关注

关注

12文章

343浏览量

42681 -

DDR芯片

+关注

关注

0文章

5浏览量

1925

发布评论请先 登录

怎么成为硬件电路设计高手?

【高手问答】第3期——走进硬件电路设计

硬件电路设计的思路分享

硬件电路设计之“磁珠”的应用资料下载

硬件电路设计之DDR电路设计(3)

硬件电路设计之DDR电路设计(3)

评论