围绕 3D异构集成(3DHI:heterogeneous integration )的活动正在升温,原因是政府的支持不断增加、需要向系统中添加更多功能和计算元素,以及人们普遍认识到,除了将所有内容都封装到单个 SoC 中之外,还有更好的前进道路。相同的进程节点。

在过去的几年里,芯片设计的前沿发生了巨大的变化。国际竞争正在推动对在岸上或友好地点设计、制造和封装的更先进芯片的投资。DARPA 微系统技术办公室刚刚宣布了其下一代微电子制造 ( NGMM ) 计划,旨在通过建立国内开放式原型设计和试验线中心来推进最先进的 3DHI 微电子技术,该中心可供美国用户使用学术界、政府和工业界。熟悉该计划的人士表示,它正在刺激整个半导体生态系统建立新的合作伙伴关系。

这只是最终将影响整个芯片行业的复杂、多层次转变的一个方面。全球的设计团队才刚刚开始理解半导体设计的新未来,这需要深入了解 3D 异构设计中的权衡和不断增加的可用选项。

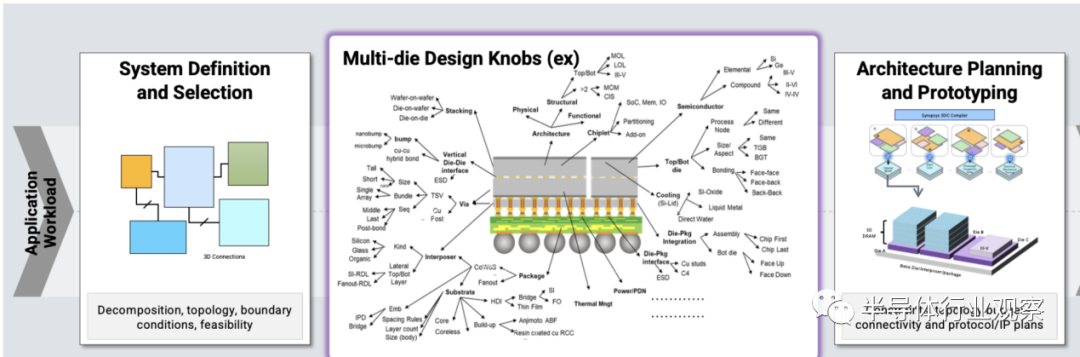

“您尝试进入 3DHI 的原因是因为您有一些 PPA 目标,或者说您想要拥有的成本优势,”Synopsys 产品管理高级总监 Shekhar Kapoor说道。“重点是什么是最优化的设计。它从前面开始。说“我要分解”很容易。但你如何决定呢?如果这样做,整个 IC 设计范式很快就会转变为系统设计范式。在这个层面上,通过软件/硬件设计,您将处理哪些工作负载?您需要什么小芯片?那里没有小芯片的市场。即使您使用从其他地方可用的子系统,它如何适合您所考虑的总体范围?”

成本仍然是每个人最关心的问题,但在系统环境中存在更大的灵活性。“成本始终很重要,” Cadence定制 IC 和 PCB 部门产品管理小组总监 John Park 说道。“但在过去,封装的目的就是成本最低。人们现在愿意为封装多付一点钱,尤其是大批量的产品。”

3DHI 还为外形尺寸的更大灵活性打开了大门,这反过来又可以对整体设计产生重大影响。

“例如,如果您要将某些东西放入智能手机中,则需要更薄、更轻的外形,”Park 指出。“如果它是放在架子上的东西,也许你不需要相同类型的配置文件。如果存在内存带宽问题,您必须找出最佳内存以及将其组合在一起的最佳 DRAM 策略。有很多不同的选择,包装仍然是狂野的西部。有些人会认为包装的选择太多,但产品有很多不同。如果你要在卫星中放置一些东西,那么它必须非常坚固,并且必须能够持续 50 年并且更加可靠。这取决于你正在设计什么,你的最终产品是什么,然后通常会得出成本,以及外形尺寸、尺寸、重量和功率,以及随之而来的所有其他因素。”

西门子 EDA产品营销经理 Keith Felton将其分为两个领域。“首先是设备之间的机械集成,”他说。“它们会与基板、封装或其他芯片/小芯片连接吗?是否需要微凸块,还是需要直接或混合键合?封装平台技术将决定其中的一些,就像您互连的芯片/小芯片一样。”

第二个领域是通信协议——UCIe、BoW、AIB 等。“如果涉及 HBM,您将需要一个硅中介层或桥作为 PHY 之间的机械接口,这将部分决定机械集成技术,”Felton说。“如果您的架构需要直接芯片到芯片集成(晶圆上芯片或晶圆上晶圆),那么很可能需要直接或混合键合。集成将影响芯片/小芯片的设计和引脚输出,因此使用支持参数化、自生成引脚区域的设计工具可以让设计人员/架构师以最小的努力或成本探索多种集成场景。”

架构选择很重要

与过去不同的是,许多设计决策都是连续且孤立的,3DHI 需要更广泛地了解所有部分如何组合在一起。设计工程师必须成为系统工程师,他们必须处理各种需要与具有不同专业知识的工程师合作的问题,例如机械工程或软件专业知识。

“如果你把它分解成太多的小部分,不仅封装的集成真的很难做到,而且这些互连也会带来开销——额外的功率开销,以及增加的一点延迟,”是德科技高速数字仿真技术产品经理 Stephen Slater说。“你必须根据重要的功能来挑选它。”

Slater指出,开发大型 ASIC 的芯片制造商知道自己的良率是多少,也知道自己的目标是什么。改变的是,他们现在必须弄清楚要分解哪些部分,以及他们愿意牺牲哪些部分来增加额外的 PHY 和复杂的高级封装所需的功率。

“(行业)清楚的一件事是,没有其他出路,”他说。“确实只有这个办法了。已经有人在向墙壁开枪了。它们已经达到了巨大的标线尺寸。他们不能做得更大。这就是前进的方向。对于其他人来说,转折点将是在他们未来的 ASIC 中,他们担心收益率会是多少。从那时起他们就开始考虑分手。”

但 3DHI 增加了一个全新的复杂性轴。数据将如何流经该系统(该系统可能是使用不同工艺技术开发的 2D 和 3D 元素的组合)?还有很多事情会出错,从机械问题到片上网络死锁(deadlocks)。

Arteris产品管理和战略营销高级总监 Guillaume Boillet 表示:“这些死锁是可怕的小错误,它们会阻止数据包流动并导致整个系统停止运行。”他指出,这些死锁有两种类型:拓扑死锁和协议死锁( topology and protocol deadlocks)。“虽然拓扑死锁特征在小芯片中通常是基本的,但只需要一个端口就可以形成环。

如果两个不同的供应商对规范的解释存在分歧,那么它很可能会出现错误。在协议死锁方面,人们正在努力简化跨小芯片的数据流的性质。尽管如此,新生的规范仍然很复杂,基于文本,因此可以进行解释。正如我们过去所看到的,每次桥接协议时,都存在未涵盖极端情况的风险。”

在宏观层面上,Cadence的Park 相信每个人对于 3DHI 都有或多或少相同的目标。但确定优先级可能很棘手。“如果你想节省成本,那么成本就成为了你的目标。如果您希望获得最高性能,那么性能会优先于它。热量开始发挥作用。如果您在服务器场中使用可以进行液体冷却的设备,请全力以赴地提高性能。如果你要在智能手机中放入某些东西,最好不要太热,以免在触摸手机时烫伤你的手。”

随着选择数量的增加,封装的权衡变得更加混乱。

“在过去的半导体时代,每隔几年我们就会得到一个新节点,就是这样,”Park说。“封装在不断发展——尤其是现在晶圆厂已经进入世界各地。因此,我们每年可能会获得六到十几种新的封装技术。随着代工厂和现在的 OSAT 不断增加其封装选项组合,这是一个不断发展的事情。它曾经是相当有限的。它主要是基于层压板的基板,但现在有了将原厂和 3D 堆叠,您就有了所有这些不同的选择。有了中介层,我会变成玻璃吗?我要选择硅吗?我应该使用薄膜 RDL 中介层吗?薄膜层压板?每个封装层都会增加成本和复杂性,具体取决于您计划做什么。如果我今天能给你一些选择,明天它就会改变,因为有人会想出另一种新方法。你有代工厂,有 OSAT,然后是这些封装技术公司——像 Deca 这样的公司,推出了一种新的封装方式。”

封装对 3DHI 系统中设备之间接口的技术规范有直接影响。

“如果你只是谈论物理引脚间距,如果我有超密集、高带宽类型的设计,我通常需要使用硅类型的基板,”Park 解释道。“这意味着如果我采用硅基板(又名高级封装),我可以采用 45 微米或 35 微米的凸块间距。如果我继续使用层压板,则间距为 125 微米。因此,封装决定了引脚的密度,这当然会影响其他因素,例如带宽。”

这里发挥作用的其他考虑因素包括通信接口,它指的是 UCIe、BoW、AIB 等。

“有了这些通信接口,事情就变得一样了,”Park 说。“UCIe 有标准封装(间距约为 130 微米)和高级封装(间距更像是 40 微米)。然后它会变得更加复杂,因为你有桥,并且与桥连接的芯片部分可以具有非常小的节距,而位于层压板其余部分上的部分必须具有更大的节距。因此,您会看到这些多间距芯片和小芯片开始采用它们所采用的封装技术。就是这样确定的。对于层压板,我们只能做到这么小,而对于硅,我们可以做得更小,这样我们就可以将引脚放置得更近。”

探索选项

模拟对于理解所有这些细节至关重要。Keysight 的 Slater 指出,对于高速数字,必须彻底模拟与 UCIe 的高速互连。射频微波也是如此。

“在射频微波领域,我们看到某些公司谈论射频小芯片的未来前景,”Slater说。“虽然这可能是以后的发展,但您在射频微波市场中确实看到的一件事是,在一个模块中,您有不同的芯片,不同的基板技术被组装在一起使用。因此,异构集成在射频模块设计中已经出现多年。现在有新的方法能够以更简化的方式堆叠各个基板技术。曾几何时,你必须按层次结构来做这件事。您必须将一项技术集成到另一项技术中,然后集成第三种技术。现在,我们可以将所有单独的技术组合成一项,从而使设计层次结构扁平化,并使设计变得更加容易。既然您正在谈论所有这些不同的接口和所有这些不同的层,从一种技术连接到另一种技术,您需要能够跟踪信号并分析信号路径在所有这些边界上的行为方式”。

劳动力问题

随着整合而来的是劳动力问题。如今,芯片、封装、验证和测试工程师通常处于责任和专业知识的孤岛中。这需要改变。

“连续的‘跨界’方法不适合跨学科的协同设计和协同优化,”西门子的Felton说。“参与 HI 设计的设计师和设计团队需要能够更早地了解集成和架构选择的影响,并在设计进入详细实施之前做出决策和权衡。这通常称为“左移”,需要将设计方法更改为imec 定义的系统技术协同优化 (STCO)。当然,劳动力教育/赋能是未来劳动力的关键,美国政府正在通过 NGMM、Cornerstone 等项目解决这一问题。”

芯片公司成功的基础之一是设计团队的长寿和凝聚力。这对于先进封装尤其重要。

“如果我去航空航天和国防客户那里,他们就去过那里,这就是他们所知道的,这就是他们做事的方式,”Park说。“你去一家大型商业公司,都是一样的。他们一直都在那里。他们就是这样做事的。我很少看到有人离开航空航天和国防领域并决定加入这家制造手机芯片的公司。人们通常会留在自己关注的领域。设计这些东西的专业知识不只是一个人的。

但现在,随着系统和 IC 的融合,这意味着需要更多的人员。您请信号完整性专家来看看,“如果您将这个小芯片从中介层移到层压板上,是否仍能提供我想要的带宽?” 或者,你让热学人员进来问,“如果我将这两件事叠加在一起,从热学角度来看这可行吗?” 现在这是一个巨大的团队努力。您无法将芯片设计和封装设计者分开。他们都与设计和验证工程师一起负责封装、布局、散热、信号完整性、电磁学、布局布线、签核——所有这些不同的人都需要聚集在一起。”

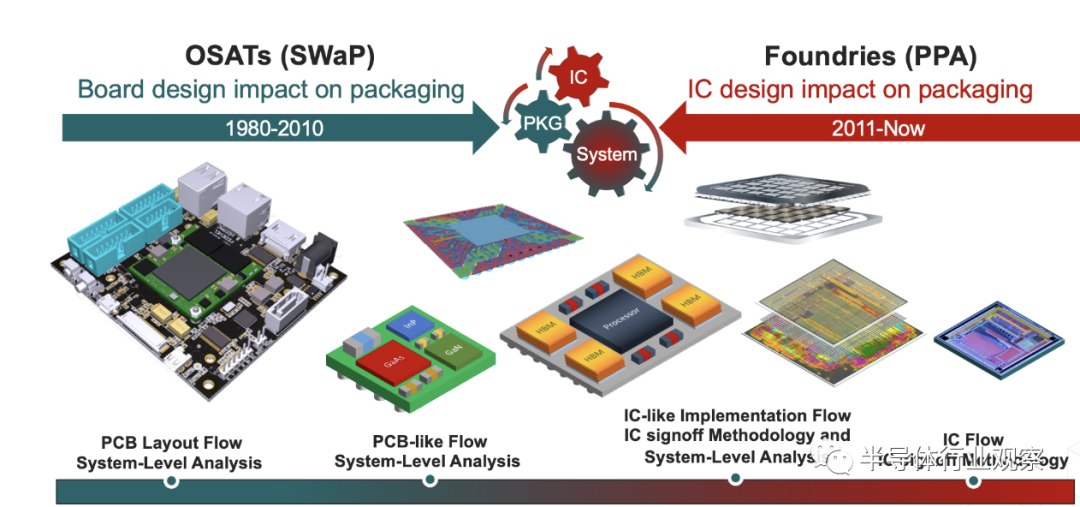

代工厂在 3DHI 中的作用

3DHI 的基础是半导体代工厂作为整个项目的推动者。

“没有代工厂,你就无法进行异构分离,”Park 说。“它们是所有正在发生的事情的推动者,从 3D 堆叠到异构集成,再到超高密度 RDL。这是因为代工厂已经认识到整个世界正在走向多芯片、多芯片——这就是未来。因此,他们现在需要做后端并集成所有这些晶圆,而不仅仅是设计这些晶圆。这意味着他们现在正在与 OSAT 竞争,但 OSAT 和代工厂之间的竞争总是好的。”

例如,台积电的 3DBlox 和三星的 CODE 是巨大的推动者,特别是对于刚接触封装设计的人来说。

“这是这组文件。将这些读入您的工具中,它就会为您的设计建立整个 3D 平面图,”Park 说。“顺便说一句,我们保证它建立的 3D 平面图可以按照这种方式制造。这是代工厂带来的巨大推动力。铸造厂带来了正式的设计结构,而不是非常非正式的包装世界。为了提高产量、降低价格,铸造厂将这种正式感带入了包装中。其中一些开始渗透到包装中,因此我们可以开始制定更正式的 OSAT 设计流程,这对行业来说都是好事。”

西门子的 Felton 指出,代工厂、OSAT 和基板供应商可以在减少 HI 采用障碍方面发挥重要作用。“第一步是帮助客户确保 DRC/PDK 的签署和流程合规性。下一个领域是提供设计工具支持,例如设计模板、技术块、使用标准的装配规范。除此之外,一些 OSAT 和基板供应商正在为其客户提供增值服务,例如脱气和阻抗匹配,这减轻了客户可能面临的所需工作量和技能。”

Chiplet 问题

3DHI 仍然被许多人认为是狂野的西部,而 Chiplet 是这个尚未被驯服的世界中不断增长的一部分。

Expedera营销副总裁 Paul Karazuba 表示:“当我们谈论来自多个供应商的小芯片时——AMD 或英特尔的小芯片,情况就不同了。” “这只是制造设计的选择。这几乎不是您在不同小芯片供应商那里面临的供应链问题。”

虽然商业小芯片正在取得进展,但互连标准仍然不存在。

“UCIe 一年前引起了很大的轰动,”卡拉祖巴说。“今天我不一定会看到同样多的噪音。这可能只是人们正在开发它的一个因素。UCIe 提供了很多承诺,并且确实提供了很多承诺。我们需要完成这件事。”

但小芯片仍然存在一些业务问题。

“谁为设备提供保修?这一切将如何处理?是否会有通用的信赖标准?我们如何测试这些小芯片是否会有通用标准?实际上,这可能会通过多芯片模块外部的名称来设置,因为我们需要为组装的小芯片提供一个更好的名称,”Karazuba 说。“盒子外面的名字很可能就是决定这一切的人,但这些如何相互作用仍然是一个悬而未决的问题。

对于像“实际上如何物理连接所有这些”这样简单的问题,当今封装单片硅上的互连在不同位置、不同节点等方面仍然有很大不同。因此,仍有大量工作需要完成必须要做。但半导体行业 70 年来一直擅长的一件事就是解决极其复杂的问题,并让事情看起来如此简单,而实际上并非如此。”

审核编辑:刘清

-

soc

+关注

关注

38文章

4514浏览量

227578 -

芯片设计

+关注

关注

15文章

1128浏览量

56437 -

3D芯片

+关注

关注

0文章

52浏览量

19020 -

ASIC芯片

+关注

关注

2文章

94浏览量

24633 -

chiplet

+关注

关注

6文章

482浏览量

13501

原文标题:3D芯片,怎么办?

文章出处:【微信号:晶扬电子,微信公众号:晶扬电子】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

玩转 KiCad 3D模型的使用

iTOF技术,多样化的3D视觉应用

SciChart 3D for WPF图表库

腾讯混元3D AI创作引擎正式发布

腾讯混元3D AI创作引擎正式上线

uvled光固化3d打印技术

3D芯片,怎么办?

3D芯片,怎么办?

评论