Hardware 设计

对于 Intel 平台,自 ICL Lake 开始,就不再支持 LPC,仅支持 eSPI。

以 TGL 平台为例,硬件设计上需要注意如下两点。

一,Hardware Strap Pin

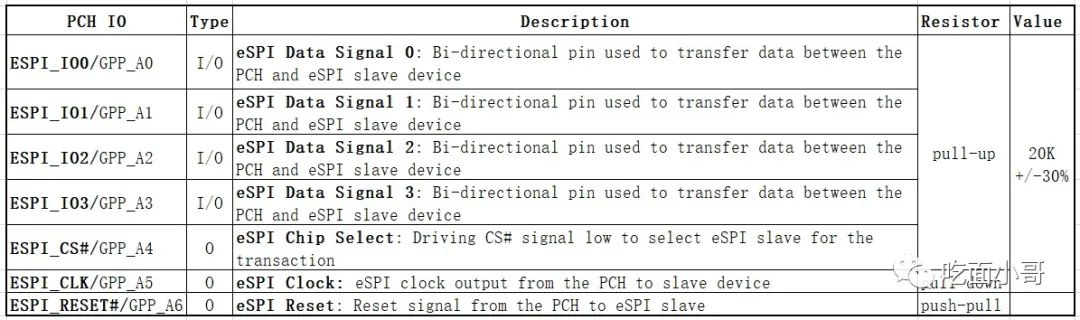

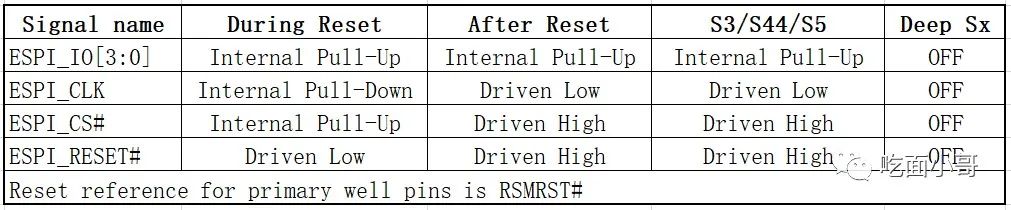

GPP_C5、GPP_H0、GPP_H1、GPP_H2,四个 pin 按顺序组成 4-Bit Boot Strap Pin。配置规则如下表格:

| 0000 = Master Attached Flash Configuration (BIOS / CSME onSPI). eSPI is enabled |

|---|

| 0010 = Master Attached Flash Configuration (BIOS / CSME onSPI). eSPI is disabled |

| 0100 = BIOS on eSPI Peripheral Channel; CSME on masterattached SPI |

| 1000 = Slave Attached Flash Configuration (BIOS / CSME oneSPI attached device). |

| 1100 = BIOS on eSPI peripheral Channel; CSME on slaveattached SPI. |

常规设计都是 MAF,eSPI Enable。正常的配置需要 0000,四个 pin 内部都有 20K 的下拉,因此 Strap Pin 保持 Floating 即可。

注意:不同 CPU 平台,Strap Pin 有差异,以对应平台 EDS 文档描述为准。

二,Flash Access

为了降低硬件设计 BOM 成本,CPU 设计上提出 MAF 和 SAF 两种 Flash 共享方式,以节省 EC Flash。

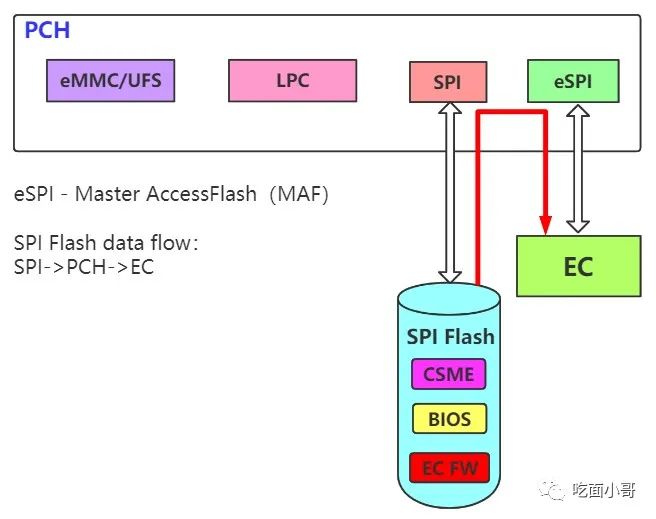

Master Attached Flash Sharing,如下图。EC 通过 eSPI 访问 PCH 下 SPI 总线上的 Flash,以获取 EC Firmware。

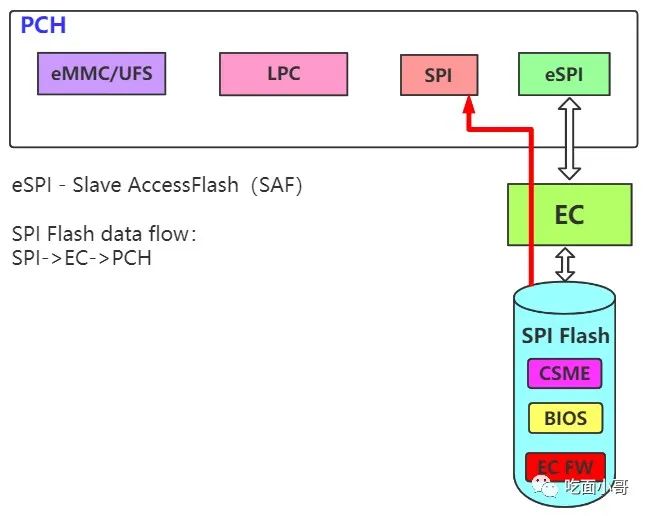

Slave Attached Flash Sharing,如下图。PCH 通过 eSPI 透过 EC 访问

BIOS、CSME Firmware。

对于 MAF 设计,需要保持 CPU 部分电打开,确保 PCH 内 eSPI 和 SPI 可以工作。EC 才有了透过 PCH eSPI Master 访问 Flash 的基础。

对于 SAF 设计,BIOS、CSME Firmware 体量大,PCH 透过 EC 访问,对 EC SPI Controller 要求比较高。

事实上,PCH 通过 自己的 SPI Controller 获取 BIOS、CSME,就称之为 MAF。PCH 通过 eSPI 获取 BIOS、CSME,就称之为 SAF。

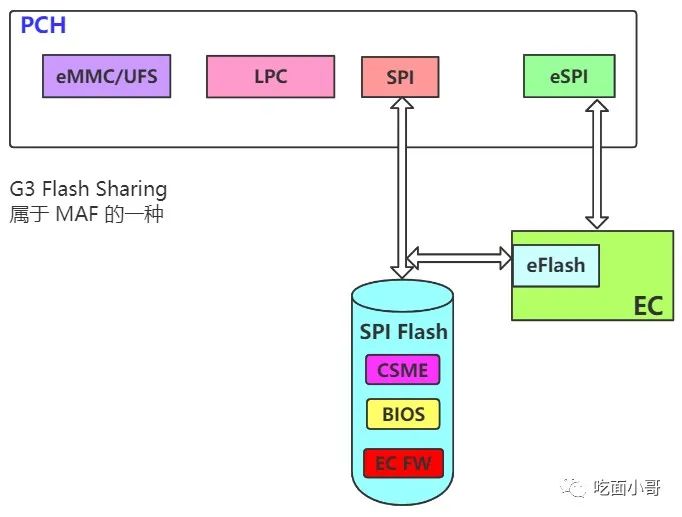

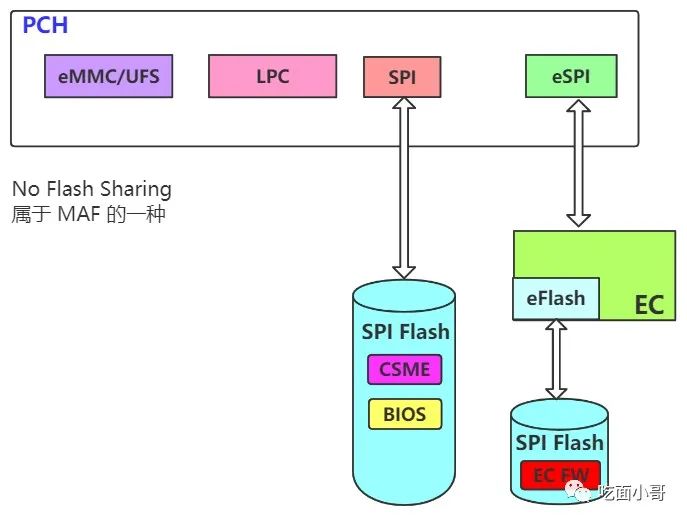

实际应用中,MAF 和 SAF 这两种 Flash Sharing 方式都没有采用。而是选择

G3 Flash Sharing 或者 No Flash Sharing。

G3 Flash Sharing,如下图。PCH 的 SPI 和 EC 的 SPI 接在一起,PCH 上电前或者 RSMRST# 拉高前,EC 直接从 SPI 接口读取 EC Firmware。

No Flash Sharing,如下图。PCH 的 SPI 和 EC 的 SPI 分别挂一个 Flash,互不干涉。

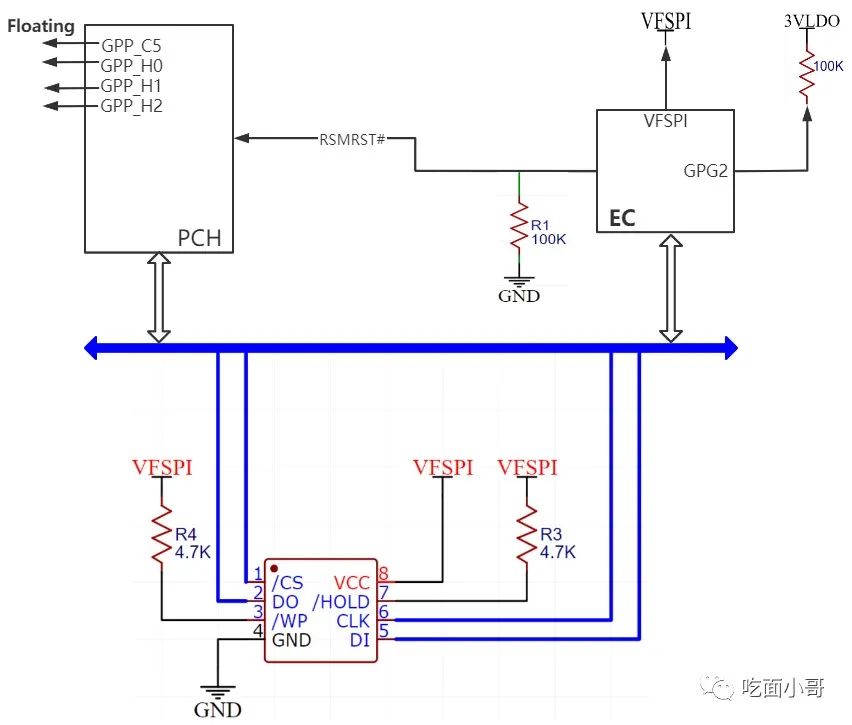

基于上述 G3 Flash Sharing 设计,通常硬件设计如下。

三,eSPI Pin List

PCH 和 EC 端的 eSPI 直接连线即可,上下拉在 chip 内部完成。

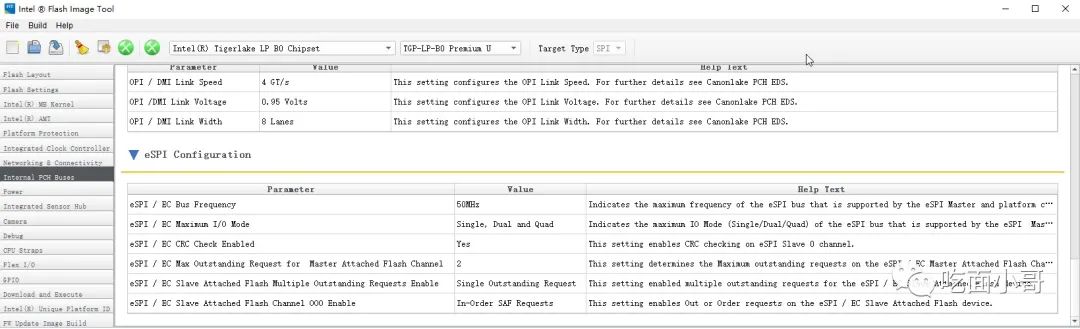

BIOS/ME 配置

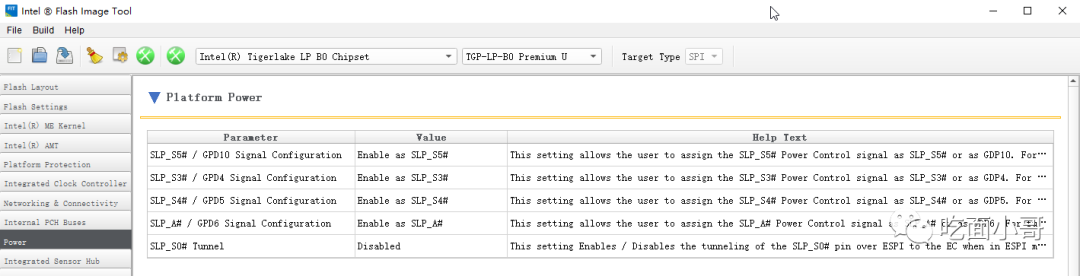

使用 FIT 配置 ME 参数,即设置 PCH 作为 eSPI Master 的工作参数,也称之为 Soft-Strap。eSPI 通讯参数最终以和 EC 沟通结果为准。

关于 FIT 更详细的配置,需要根据项目实际情况设定。

Boot 流程

eSPI 的 Boot 流程包括 Channel Config、Flash Access、Virtual Wire Communication。MAFS 和 SAFS 启动过程略有差异,此处以 MAFS 启动为例。

eSPI 通道配置

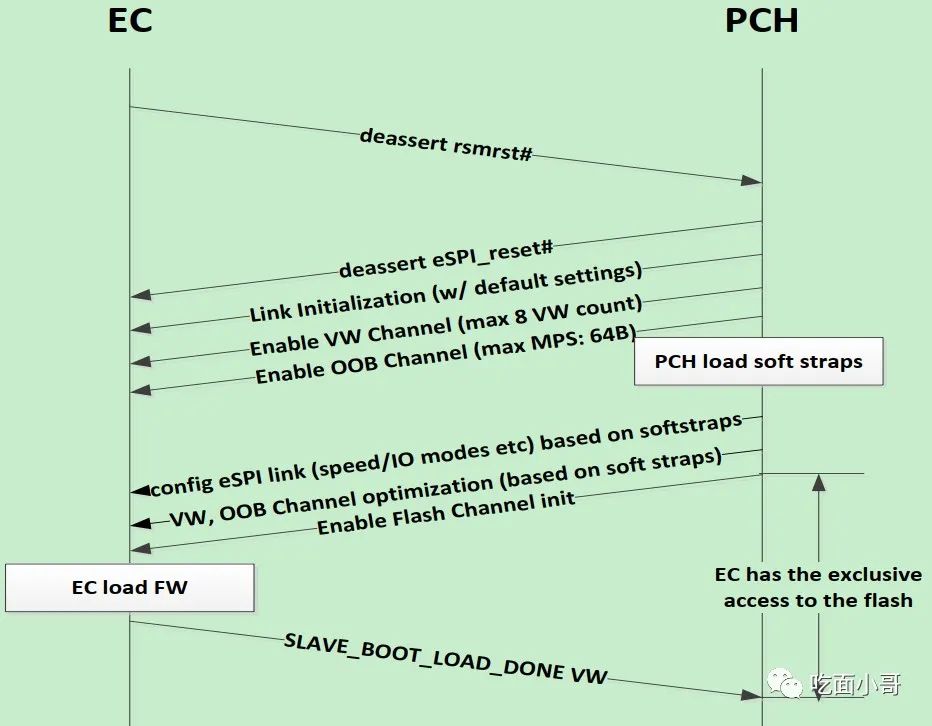

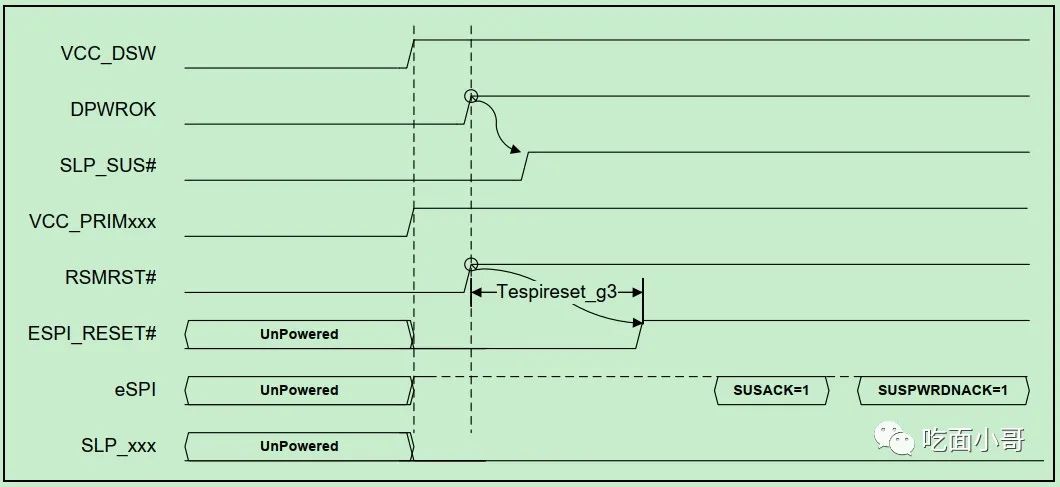

第一步,EC 拉高 RSMRST#(之前的时序按要求操作,同时 EC 端 的 eSPI Slave 需要复位完毕,准备待命)。然后 PCH 拉高 eSPI_Reset#。

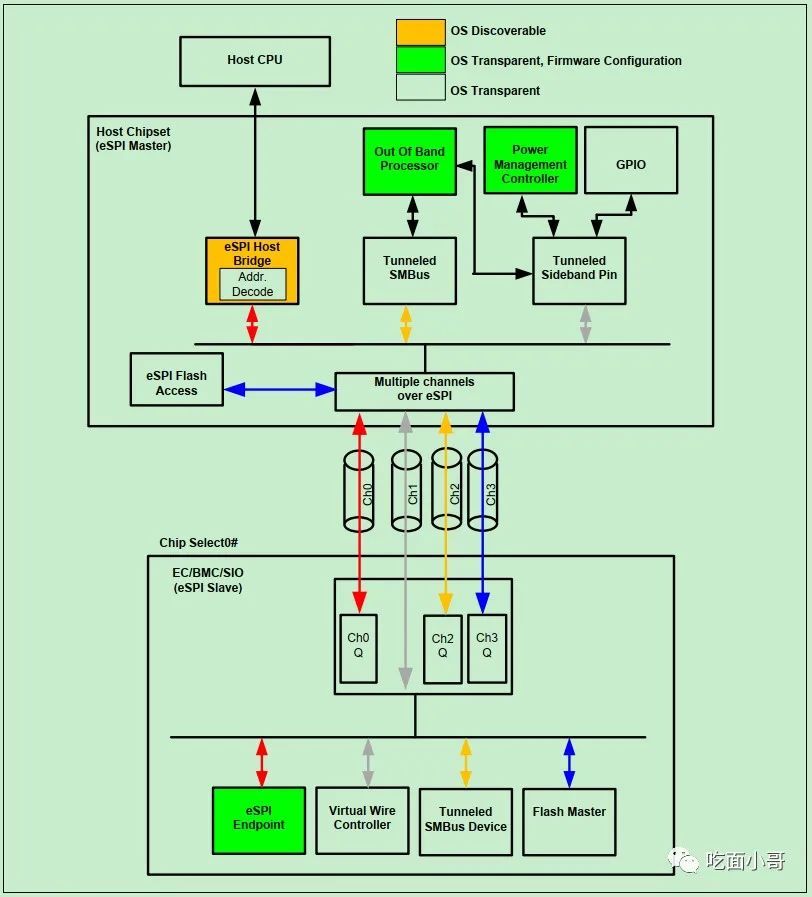

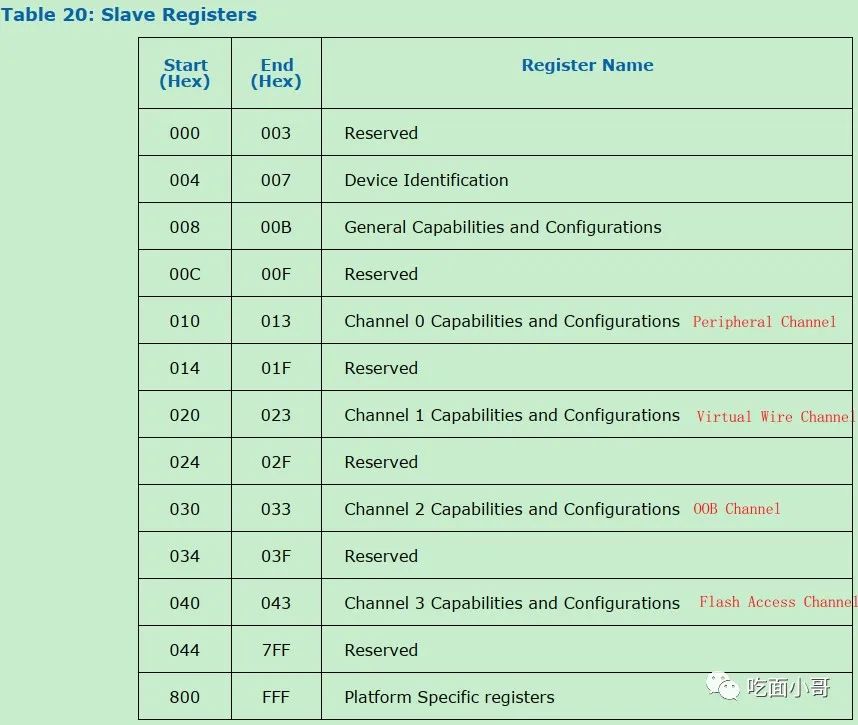

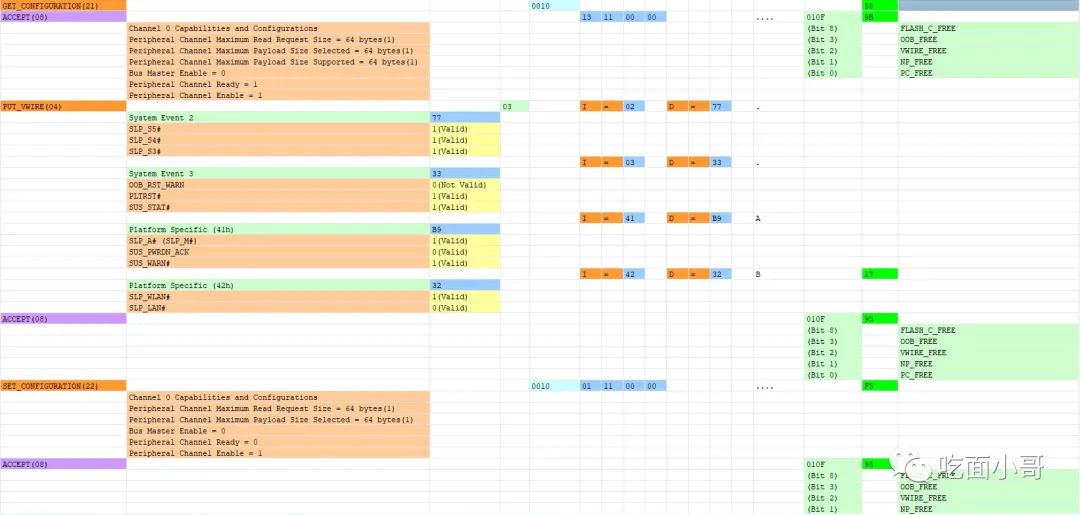

第二步,eSPI-Master 配置 Peripheral、Virtual Wire、OOB、Flash Access 四个 Channel。eSPI Master 端对 Channel 的配置,就是读取 Slave Channel 配置寄存器。然后根据 Soft-Strap(ME配置)改写 Slave 端配置寄存器,以配置实际需求的通道通讯参数。如下图,Ch-0/1/2/3 分别是 Peripheral、Virtual Wire、OOB、Flash Access Channel。

PCH 作为 eSPI Master 配置 Channel,基本逻辑就是 eSPI Master 读取 eSPI Slave寄存器,改写寄存器,回读确认。寄存器操作最小单位是 4Byte。使用到的指令是 GET_CONFIGURATION 和 SET_CONFIGURATION。

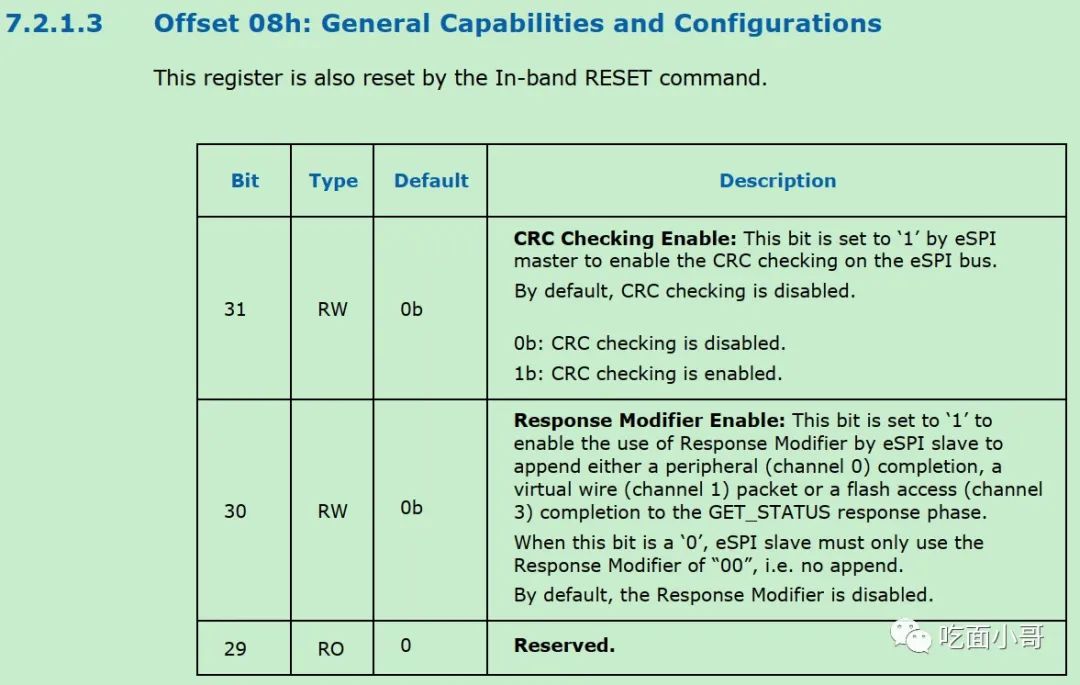

eSPI Slave 端需要配置的寄存器只有如下 5个,即 Offset 08、10、20、30、40,分别对应 4 个 Channel。

寄存器配置细节可以参考《Enhanced Serial PeripheralInterface (eSPI) V1.0》

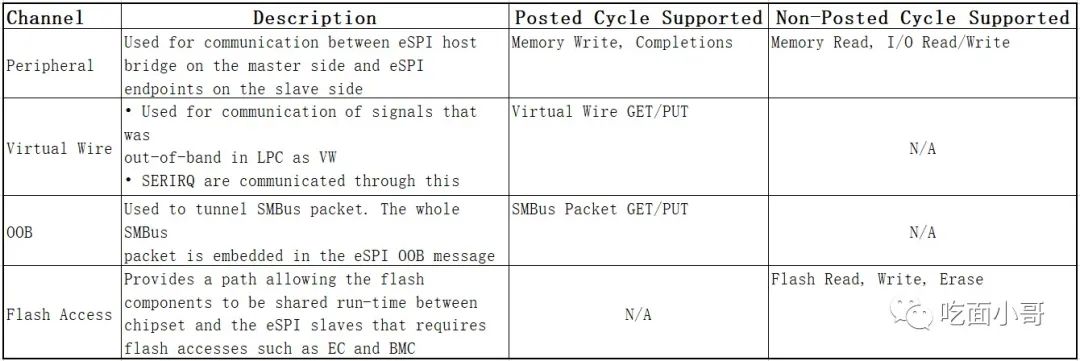

每个 Channel 的功能如下表

第三步,Slave Boot Done

配置完 Flash Access Channel,对于 MAFS 结构来说,EC 就可以通过 eSPI 访问 PCH 下的 SPI Flash了。EC 应当根据实际需要通过 eSPI 访问 PCH SPI Controller 下连接的 Flash,读取 EC Firmware。

实际上,目前通用的设计是 Flash Sharing 的接线方式,EC 虽然不通过 eSPI 读取 Firmware。但是依旧需要给 Host 发送一个 Virtual Wire Signal,即 SLAVE_BOOT_LOAD_DONE。

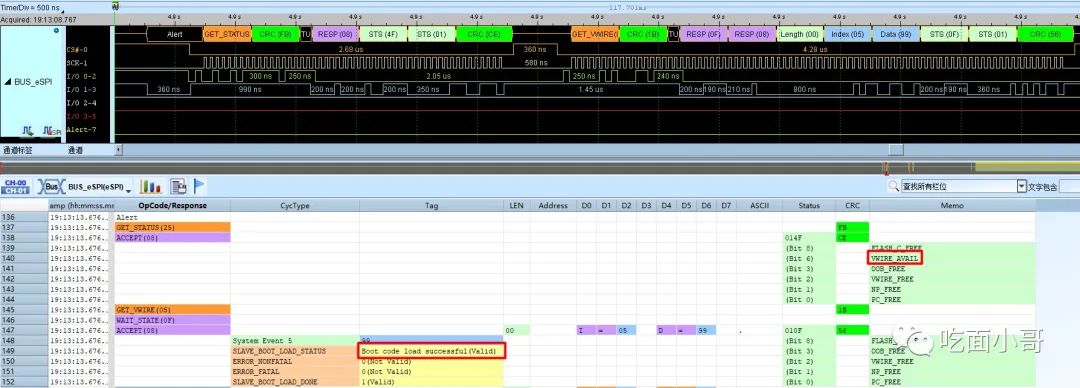

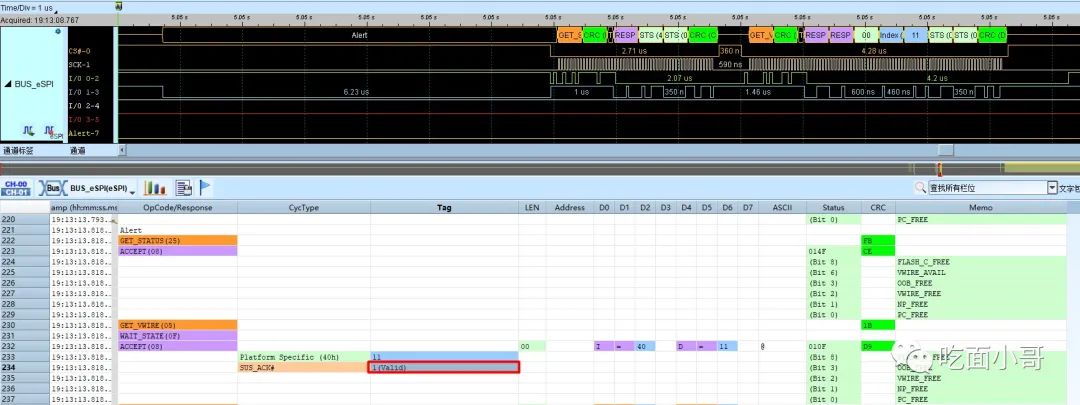

Slave 端发送 SLAVE_BOOT_LOAD_DONE 信号给 Host。由于是 Slave 主动给 Host 发送,因此在 CS# 高电平期间,Slave 拉低 I/O 1 产生一个 ALERT# 直到 Host 端拉低 CS# 为止。下图 ALERT# 拉低时间就为 360ns。

Host 紧接着发送 GET_STATUS 命令,查看 Slave 的 Event,Slave 置位 BIT-6,表明发生了 Virtual Wire 事件。

Host 发送 GET_VWIRE 获取实际的 Virtual Wire 状态。

Host 读取 Virtual Wire 状态。发现 SLAVE_BOOT_LOAD_DONE 置位,Host 即可进行下一步 Boot。

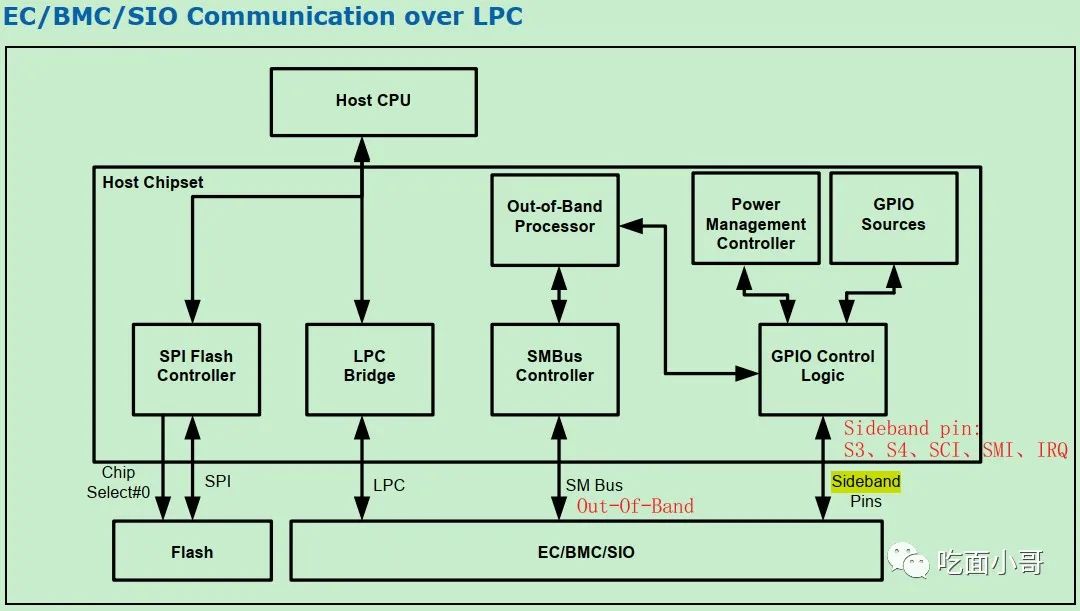

Virtual Wire 交互

eSPI 设计的一个优势就在于减少引脚资源,把 Sideband pin 转换为 in-band Message。因此 PCH 输入或者输出的一些 pin 已经转为 in-band Message。

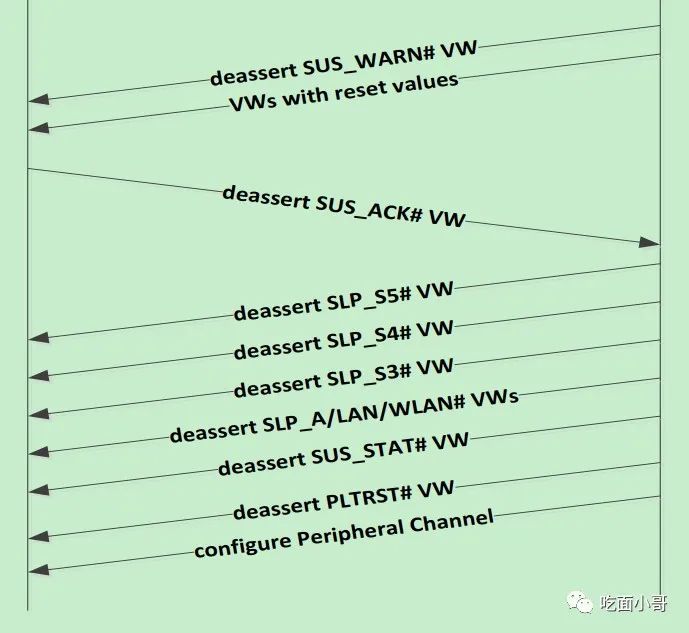

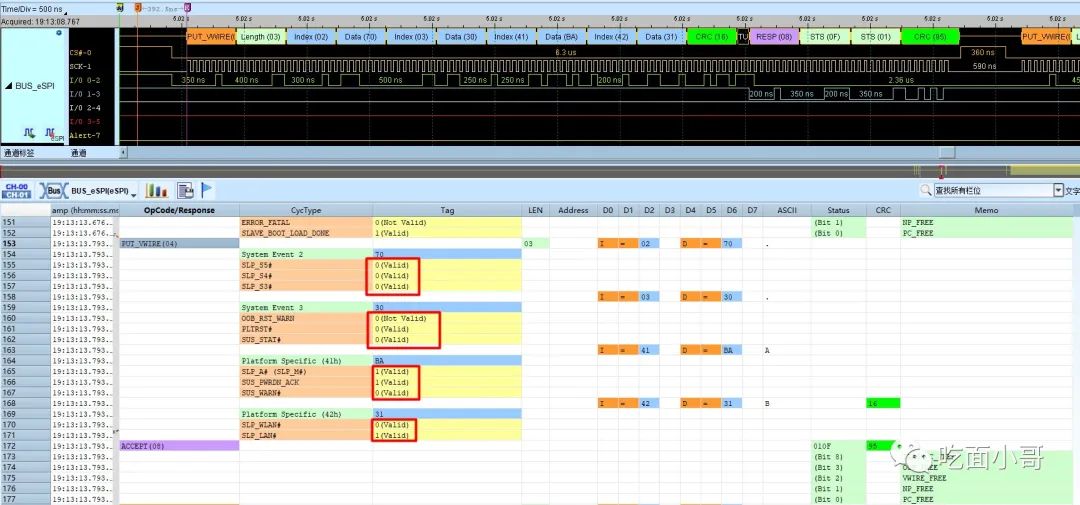

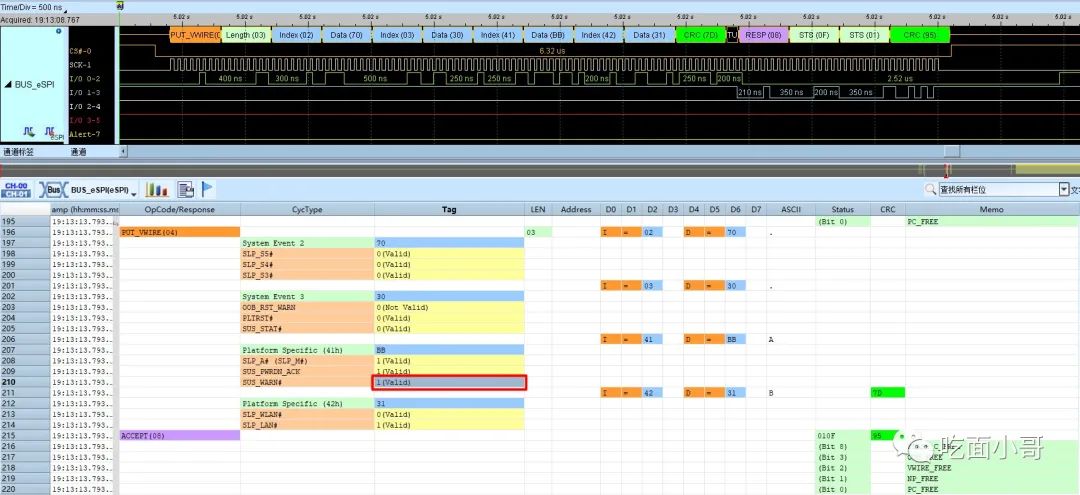

第四步,eSPI Master(PCH) 通过 PUT_VWIRE 指令把所有 VW 信号设置为复位值。

第五步,eSPI Master(PCH)发送 SUS_WARN# = 1 到 eSPI Slave。EC 回复 SUS_AC# =1 到 PCH

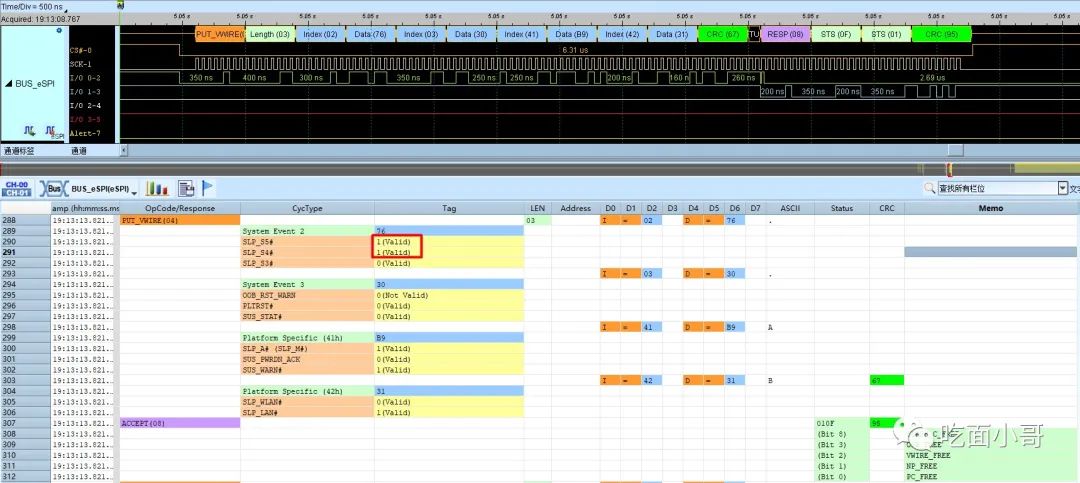

第六步,eSPI Master(PCH)挨个儿发送 SLP_S5 / 4 / 3,SLP_A / LAN / WLAN 高信号到 EC。下图仅展示了 SLP_S4/5。

第七步,eSPI Master(PCH)发送 SUS_STAT# 和 RPLTRST# 信号到 EC。这将会使能 Peripheral Channel。

紧接着 eSPI Master 根据 Soft-Strap(ME)配置 Peripheral Channel。

至此,eSPI 启动就已经完成,接下来就是 Memory、IO、OOB 通讯。

以上流程为个人理解,仅供参考。

-

cpu

+关注

关注

68文章

10451浏览量

206580 -

intel

+关注

关注

19文章

3452浏览量

184785 -

SPI

+关注

关注

17文章

1615浏览量

89666 -

总线

+关注

关注

10文章

2713浏览量

87227 -

硬件设计

+关注

关注

18文章

346浏览量

44321

发布评论请先 登录

相关推荐

eSPI协议抓包分析

回收罗德施瓦茨ESPI3进口接收机ESPI3

ESPI3 回收ESPI3 EMI测试接收机

供应R&S罗德与施瓦茨ESPI测试接收机

eSPI接口通道功能解析

eSPI启动流程详解

eSPI启动流程详解

评论