今天和大家一起概要认识RISC-V可信执行环境(TEE):Risc-V Keystone。

Keystone是一个开源框架,旨在构建自定义的可信执行环境(TEE)。

它提供了一个高度可编程的受信任层,位于不可信操作系统之下,并使用RISC-V的基本组件来实现。

Keystone的设计理念是,通过将隔离机制与资源管理、虚拟化和信任边界的决定解耦,为低成本用例定制铺平道路。

与现有的TEE方案相比,Keystone更加灵活和可定制,它可以独立探索现有设计中的差距/权衡、快速原型化新功能要求、更短的修复周期、适应威胁模型和特定于用途的部署。

Keystone的设计也考虑了安全性,利用硬件原语提供对TEE保证的内置支持,例如安全引导、内存隔离和认证。

下面来一起看一下!

为什么需要Keystone?

Keystone是一个开源框架,可以让你像搭积木一样构建自己的可信执行环境(TEE)。TEE是可以在不安全的计算机环境中保护你的代码和数据的地方。过去十年,TEE得到了快速发展,许多CPU供应商都推出了自己的TEE。

但是每个供应商的TEE都有自己的限制,就像你不能随意改变积木的形状一样。当你选择一个云服务提供商或软件开发人员时,他们可能会被锁定在他们自己TEE的限制中,这可能不符合你的实际应用需求。

Keystone就像一个新的积木盒,里面有各种可以构建TEE的组件。你可以根据自己的需求,选择使用哪些组件,构建出符合自己需求的TEE。这样你就可以更灵活地保护你的代码和数据,无论是在云服务器、移动电话、互联网服务提供商、物联网设备、传感器还是硬件令牌上。

Keystone的设计也考虑了安全性。它有一个安全监视器(SM)和运行时(RT)组件。SM使用硬件原语提供安全保证,例如安全引导、内存隔离和认证。RT则在飞地内提供功能模块,例如系统调用接口、标准libc支持、虚拟内存管理和自分页。这样,任何飞地特定的功能都可以由RT干净地实现,而SM则强制保证硬件的安全性。

总的来说,Keystone是一个更灵活、更安全的开源框架,可以让你构建自定义的TEE来保护你的代码和数据。

Keystone简介

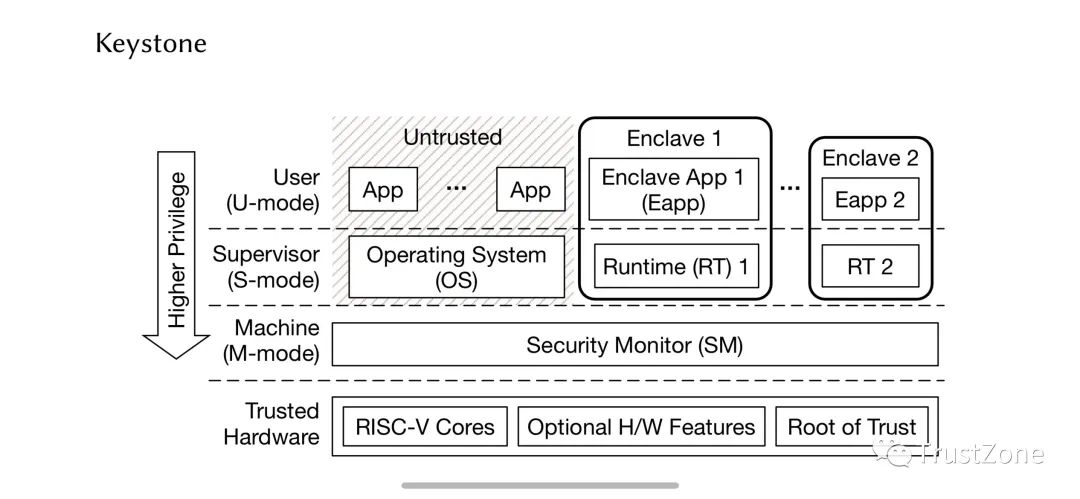

具有 Keystone 功能的系统由不同权限模式的多个组件组成。

可信硬件(Trusted Hardware) 是由可信供应商构建的 CPU 包,必须包含与 Keystone 兼容的标准 RISC-V 内核和信任根。硬件还可能包含可选功能,例如缓存分区、内存加密、密码安全的随机源等。安全监视器需要特定于平台的插件来支持可选功能。

Security Monitor (SM) 是具有小型 TCB 的 M 模式软件。SM 提供了一个接口来管理 enclave 的生命周期以及利用平台特定的功能。SM 执行大部分 Keystone 的安全保证,因为它管理 enclave 和不受信任的操作系统之间的隔离边界。

飞地(Enclave) 是与不受信任的操作系统和其他飞地隔离的环境。每个飞地都有一个私有物理内存区域,只能由飞地和 SM 访问。每个 enclave 由一个用户级 enclave 应用程序eapp和一个主管级运行时组成。

Enclave Application (eapp) 是在 enclave 中执行的用户级应用程序。可以从头开始构建自定义 eapp,或者只在 Keystone 中运行现有的 RISC-V 可执行文件。

运行时 是 S 模式软件,它实现了系统调用、陷阱处理、虚拟内存管理等功能。

Keystone特性

Keystone是一个基于RISC-V构建可定制的可信执行环境(TEEs)的开源项目,适用于各种平台和用例。

我们的目标是构建一个安全可信的开源安全硬件飞地,可应用于各种应用和设备。

Keystone是一个基于Risc-V的开源TEE框架,在任意Risc-V处理器中,只需对硬件进行非常小的修改即可满足Keystone平台框架的使用,下面就简单介绍一下使用Keystone需要Risc-V的CPU支持哪些特性。

指令集兼容性

•Keystone 需要所有三种权限模式 (M/S/U) 来支持 Linux 机器中的动态用户级隔离。•rv64gc-lp64d(Sv39 虚拟寻址模式)•rv32gc-ilp32d(Sv32 虚拟寻址模式)

Keystone 需要所有三种权限模式 (M/S/U) 来支持 Linux 机器中的动态用户级隔离。这意味着 Keystone 可以支持三种不同的权限级别,即机器级(M)、系统级(S)和用户级(U)。这三种权限级别可以用于创建和管理不同类型的隔离和安全环境。

Keystone 还支持两种不同的虚拟寻址模式,即 Sv39 和 Sv32。这些模式是 RISC-V 架构中的虚拟内存系统的一部分,用于在虚拟内存中管理代码和数据。Sv39 是 64 位模式,支持 32 位应用程序在 64 位系统中运行。而 Sv32 是 32 位模式,支持在 32 位系统中运行 32 位应用程序。

三个软件特权

RISC-V 具有三个软件特权级别(按功能递增的顺序):

•用户模式(U-mode)、•主管模式(S-mode)•机器模式(M-mode)。

处理器一次只能在其中一种特权模式下运行。

权限级别定义了正在运行的软件在其执行期间可以做什么。各个权限级别的常用用法如下:

•U-mode:用户进程•S-mode:内核(包括内核模块和设备驱动程序)、管理程序•M 模式:引导加载程序、固件

一些嵌入式设备可能只有 M 模式或只有 M/U 模式。

M-mode 是最高特权模式,控制所有物理资源和中断。M 模式类似于 x86 等复杂指令集计算机 (CISC) ISA 中的微代码,因为它不可中断且不受较低模式的干扰。

Keystone 使用 M 模式运行安全监视器 (SM),即系统的可信计算库 (TCB)。

是的,M-mode 是最高特权模式,可以控制所有物理资源和中断。它类似于 x86 等复杂指令集计算机 (CISC) ISA 中的微代码,因为它不可中断且不受较低模式的干扰。在 RISC-V 架构中,M-mode 是一种特权模式,可以执行诸如内存管理、异常处理和系统调用等关键任务。它具有对所有物理资源的完全控制权,并且可以中断其他较低模式的操作。相比之下,S-mode 和 U-mode 分别具有系统级和用户级权限,并且必须通过特定的系统调用才能进入 M-mode。

内存保护

首先,RISC-V是一种开源的指令集架构(ISA),它提供了一种灵活的方式来定义和扩展指令集。RISC-V Priv 1.10标准引入了物理内存保护(PMP)功能,这是一个强大的原语,允许在M模式下从较低的权限(U-/S模式)来控制物理内存的访问。

PMP通过一组控制和状态寄存器(CSR)来实现。这些寄存器可以配置为允许或禁止对特定物理内存区域的访问。

•在U模式下,只能访问那些由PMP配置为允许访问的物理内存区域。•在S模式下,可以访问所有未被禁止的物理内存区域。•然而,只有M模式下可以配置和更改PMP寄存器的状态。

每个PMP条目可以由一个或多个PMP CSR定义。每个CSR都有一个特定的位模式,用于指示该CSR所控制的物理内存区域的大小和范围。

例如,一个PMP条目可能由两个CSR定义,一个用于指示物理内存区域的起始地址,另一个用于指示大小。

Keystone是一个用于构建自定义可信执行环境(TEE)的开源框架。它使用RISC-V作为其基本的指令集,并引入了安全监视器(SM)和运行时(RT)组件。Keystone需要PMP来实现enclave的内存隔离。

在Keystone中,SM负责执行安全监视功能,它使用PMP来强制执行内存访问控制。每个enclave都有自己的隔离的物理内存区域,这些区域只能被该enclave访问。

RT在每个enclave内提供功能模块,例如系统调用接口、标准libc支持、虚拟内存管理和自分页。RT通过与SM通信来请求访问外部资源,例如共享内存或主机资源。

通过这种方式,Keystone能够提供高度隔离和安全的执行环境。

每个enclave都有自己的虚拟内存空间,并且只能访问由SM授权的物理内存区域。这种设计使得在执行敏感任务时可以确保数据的安全性和完整性。

中断与异常

在默认情况下,M模式是系统中任何中断或异常(即陷阱)的第一个接收者,这意味着M模式对CPU调度和配置具有完全的权限。然而,M模式可以根据需要将这种控制权委派给S模式。

M模式可以使用mieCSR来禁用或启用每个中断。mieCSR是一个控制和状态寄存器,可以配置为指示哪些中断被允许或禁止。

M模式还可以通过设置陷阱委托寄存器的位(即mideleg和medeleg)将陷阱委托给S模式。Trap委托可以跳过M-mode处理程序,这样S-mode可以快速处理频繁的陷阱,例如页面错误、系统调用(环境调用)等。

通过这种方式,M模式和S模式之间的协作可以优化系统性能。频繁的中断或异常可以由S模式快速处理,而M模式可以专注于更重要的任务,如CPU调度和配置等。这种分权处理方式使得系统可以根据特定的应用需求进行优化配置。

虚拟地址转换

在RISC-V中,虚拟地址转换是由内存管理单元(MMU)执行的,这一过程由两个硬件组件组成:页表遍历器(PTW)和转换后备缓冲区(TLB)。

虚拟地址转换使用多级页表,页表中的页数和页大小取决于寻址方式。CSR(控制和状态寄存器)确定MMU应该使用哪种寻址模式以及哪个物理页面包含用于开始页表遍历的根页表。

在Keystone飞地中,内存访问保护是通过PMP(物理内存保护)实现的。飞地具有自己的受保护的页表,操作系统无法修改。

PMP通过控制和状态寄存器(CSR)来限制对物理内存的访问。每个飞地都有自己的隔离的物理内存区域,只能被该飞地访问。

操作系统无法修改飞地的页表,因此无法通过更改页表来进行攻击。这种设计提供了高度隔离和安全的执行环境,确保了在执行敏感任务时数据的安全性和完整性。

Keystone工作流程

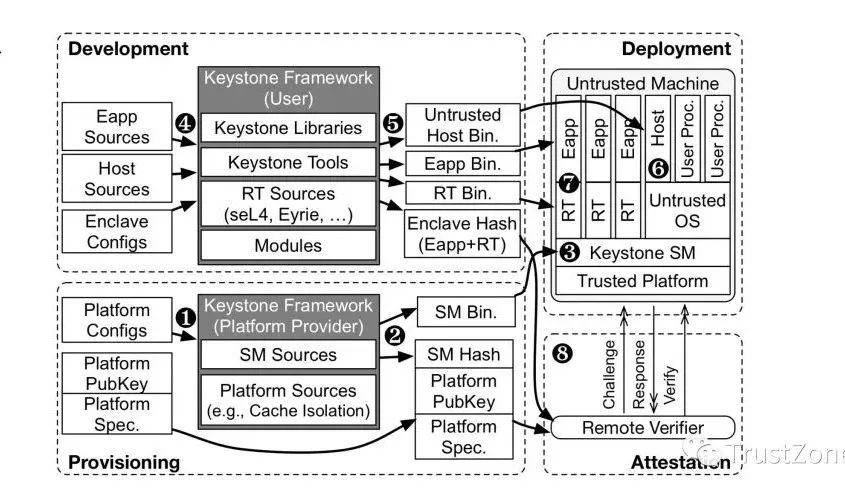

这个图片展示了开发的工作分配,主要可以分为飞地开发者和平台开发者。

•❶❷❸步骤由平台提供者执行,需要将满足Keystone架构的Security Monitor部署在设备上;•飞地开发人员使用Keystone SDK 开发飞地。开发人员构建 eapp、主机和运行时二进制文件,并(可选)将它们打包到一个文件中 (❹);•然后通过❺、❻和❼部署在设备上;•❽是远程证明的流程。

SM作为跟平台强相关的组件由平台开发者提供,而飞地开发者负责Host APP、Eapp、Runtime的开发。

•平台开发者的工作:•平台开发者需要开发和部署满足Keystone架构的Security Monitor。这个组件负责监视和管理内存访问权限,确保只有经过授权的代码和数据能够访问物理内存。•平台开发者还需要配置和管理页表(Page Table),这是操作系统用来管理虚拟内存和物理内存之间映射的数据结构。平台开发者需要设置正确的页表,以确保虚拟地址可以正确地映射到物理地址。•飞地开发人员的工作:•飞地开发人员使用Keystone SDK来开发飞地应用程序。这个SDK提供了一套API和工具,用于构建隔离的、安全的执行环境。•飞地开发人员首先需要创建一个eapp,这是飞地应用程序的代码和数据的集合。eapp可以是任何类型的程序,例如一个简单的应用程序、一个操作系统或者一个安全关键的应用程序。•飞地开发人员还需要开发和配置运行时(Runtime)环境。运行时环境提供了执行eapp所需的各种服务,例如内存管理、进程调度、输入输出等。•飞地开发人员可以使用Keystone SDK提供的工具来将eapp和运行时环境打包为一个可执行的二进制文件。这个二进制文件可以在设备上运行,并且可以与其他飞地应用程序隔离执行。•部署过程:•飞地开发人员将可执行的二进制文件部署到设备上。部署方式可以根据设备类型和操作系统而有所不同,例如可以通过USB传输、网络上传或者直接在设备上安装。•在设备上部署后,飞地应用程序将会被加载到内存中,并开始执行。每个飞地应用程序都有自己的隔离的物理内存区域,只能访问自己的内存空间,而不能访问其他应用程序的内存空间。•远程证明流程:•在某些情况下,可能需要验证飞地应用程序的完整性和安全性。这时可以使用Keystone提供的远程证明(Remote Attestation)流程。这个流程允许第三方机构或者用户验证飞地应用程序是否符合Keystone的安全标准。•远程证明流程通常包括收集飞地应用程序的元数据、运行时状态和内存内容等信息,并将这些信息提交给验证机构进行验证。验证机构可以使用Keystone SDK提供的工具和分析算法来验证这些信息的完整性和安全性。如果验证通过,那么可以认为飞地应用程序是可信的。

Keystone生命周期

创建阶段:

•申请内存:在创建飞地之前,需要向系统申请一块连续的内存,这块内存被称为飞地私有内存(EPM)。EPM是飞地应用程序的专用内存,只能由该飞地访问。•加载二进制文件:在申请到EPM之后,需要将飞地的二进制文件加载到EPM中。这个二进制文件包括飞地的页表(PT)、运行时(RT)和eapp。这些组件是飞地应用程序运行所必需的。•创建飞地:在加载完二进制文件之后,通过调用SM(安全监视器)来创建飞地。SM使用PMP(物理内存保护)条目来隔离和保护创建的EPM内存。PMP条目定义了哪些物理内存区域是受保护的,以及哪些核可以访问这些区域。•校验和度量:在飞地创建完成后,SM将对飞地进行校验和度量。这个过程主要是为了验证飞地的初始状态是否符合预期,确保没有恶意代码注入或者其他安全问题。

执行阶段:

•运行和继续:在这个阶段,Host可以控制一个核运行飞地。为了实现这个控制,SM将赋予这个核访问EPM的PMP权限。然后,该核开始执行飞地应用程序。•停止和退出:运行飞地是可以随时退出或停止的。当停止或退出时,SM会切换核的PMP权限,确保核不再具有访问EPM的权限,从而保持通过PMP与外界隔离。

销毁阶段:

•销毁:Host可以随时销毁一个飞地。当销毁一个飞地时,SM会释放相关的PMP条目,并回收EPM所占用的空闲内存。这样,系统可以重复利用这块内存来创建新的飞地。

VS TrustZone

TrustZone的关键核心词汇就是隔离,这个词汇。什么模块都增加了一个filter,都增加了一个安全与非安的标志位,这个真的设计蛮巧妙的。

那Risc-V的keystone方案相对于TrustZone的优势会有什么优势呢?

主要体现在以下几个方面:

•内存保护:Keystone使用PMP(物理内存保护)机制来隔离和保护每个飞地的物理内存,确保一个飞地无法访问其他飞地的内存空间。这种保护机制可以防止恶意代码注入和数据泄露,提高了安全性。TrustZone虽然也提供了内存隔离功能,但它无法像Keystone那样提供全面的物理内存保护。•飞地隔离:Keystone支持创建多个相互隔离的飞地(Zone),每个飞地都有自己的运行时环境、应用程序和数据,相互之间不受影响。这种隔离机制可以防止一个飞地发生问题时影响到其他飞地,提高了系统的可靠性。而TrustZone虽然也提供了隔离功能,但每个隔离区(Secure World)之间的数据和程序共享,存在潜在的安全风险。•灵活性和可扩展性:Keystone的架构更为灵活和可扩展,它支持在飞地中动态创建和销毁虚拟机,支持多种操作系统和应用程序的部署,可以满足不同场景的需求。而TrustZone在虚拟化方面的支持相对较弱,扩展性也有限。•性能优化:Keystone通过将不同的运行时环境和应用程序部署在不同的飞地中,可以更好地利用系统资源,减少不必要的开销,提高性能。而TrustZone的运行时环境是固定的,无法进行优化。

总体而言,Risc-V的keystone方案在内存保护、飞地隔离、灵活性和可扩展性以及性能优化等方面相对于TrustZone具有优势。然而,需要注意的是,这些优势并非绝对,具体选择哪种方案还需根据实际应用场景和需求进行权衡。

Keystone方案面临的一些挑战和限制

•方案的灵活性必定带来开发者的工作量,因为需要同时在SM中进行内存管理和生命周期管理,也就对应着代码量的增加,于是风险性就变大了。

怎么保证代码的可靠性?对于这些关键部分的代码,可以采用形式化验证(formal verification)或静态代码分析(static code analysis)等方法来检查代码的正确性。

其次,可以采用安全的编程实践,避免常见的安全漏洞。最后,可以通过在SM上实施访问控制,只允许授权的实体访问这些代码,防止未经授权的访问。

•PMP段数配置有限和内存要求连续的问题

关于PMP段数配置有限和内存要求连续的问题,这确实可能会对系统部署造成挑战。这可能需要系统设计师在实现时进行适当的规划和优化。例如,可以预先对系统内存进行分区,并保留一些区域专门用于飞地的创建。同时,对于需要连续内存的情况,可以通过预分配或动态内存管理技术来解决。

•攻击者通过无限创建飞地达到DDOS攻击的目的

在Keystone中,飞地的创建和销毁都需要经过SM的授权,并且SM会跟踪每个飞地的状态和资源使用情况。

Keystone本身的设计并没有提供防止DDOS攻击的机制。然而,可以通过其他安全机制来缓解这种攻击风险。

•资源限制:通过在系统级别或飞地级别设置资源限制(如内存、CPU等),防止单个飞地或多个飞地过度消耗资源。这样可以限制潜在的DDOS攻击者利用飞地资源的程度。•访问控制:通过严格的访问控制机制,限制飞地之间的通信和交互。这样可以防止恶意飞地通过大量请求或数据流来淹没其他飞地或系统资源。•监控和检测:通过实时监控系统的资源使用情况,及时发现异常流量或行为。一旦发现潜在的DDOS攻击,可以采取相应的防御措施,如限流、隔离或终止恶意飞地的运行。

•实现复杂性

Keystone方案需要实现和管理多个飞地和相应的运行时环境,这需要复杂的内存管理和生命周期管理机制。同时,要确保所有飞地之间的隔离和安全性,需要实现精细的访问控制和验证机制。

•有限的资源

虽然Keystone方案可以有效地隔离和保护飞地,但每个飞地仍然需要独立的运行时环境和内存空间。这可能导致有限的资源分配,特别是在内存和处理器资源有限的情况下。

•性能开销

Keystone方案的实现和管理需要一定的性能开销。例如,在创建和销毁飞地时,需要进行内存分配和回收、权限验证和安全监控等操作。这些开销可能会影响系统的整体性能。

•so on

keyStone

如果你想学习了解keystone,简单的follow下面流程或许会对你有所帮助:

•了解Riscv

关于芯片架构、中断与异常、内存管理

•了解操作系统相关知识

进程、中断、驱动

•理论:keystone

【Keystone: An Open Framework for Architecting Trusted Execution Environments】[1]

【Keystone-Enclave-An-Open-Source-Secure-Enclave-for-RISC-V】[2]

•实践:阅读官方指导文档【最好的指导书】

【Keystone-Getting-Started】[3]

一个新的技术的产生,必定是为了解决在某些方面的痛点而产生的,但是同时也必定会带来一些新的痛点。我想这就是为什么,很多的项目中都需要技术专家来做技术选型,通过不同技术搭配来实现一个系统的稳定与平衡。

-

虚拟化

+关注

关注

1文章

403浏览量

30842 -

开源框架

+关注

关注

0文章

33浏览量

9588 -

RISC-V

+关注

关注

48文章

2792浏览量

51902

原文标题:keyStone

文章出处:【微信号:IP与SoC设计,微信公众号:IP与SoC设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

为什么RISC-V是嵌入式应用的最佳选择

RISC-V 手册

2025新思科技RISC-V科技日活动圆满结束

构建基于 RISC-V 平台的 TEE 架构:RV-ACRN Hypervisor 的实践与展望

RISC-V和ARM有何区别?

FPGA与RISC-V浅谈

直播预告|智算时代下,RISC-V 安全技术在金融场景的探索与实践

芯来科技亮相RISC-V Day Tokyo 2025

2025中国RISC-V生态大会-运营商分论坛成功举办

认识RISC-V可信执行环境(TEE):Risc-V Keystone

认识RISC-V可信执行环境(TEE):Risc-V Keystone

评论