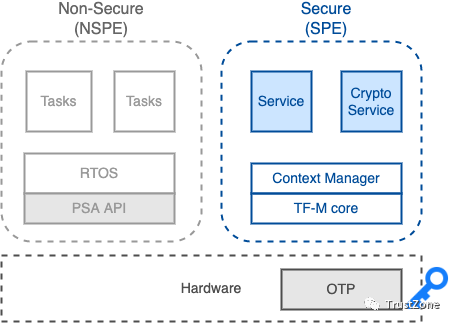

SPE主要是提供需要安全保护的服务,例如固件更新、加解密;而NSPE则是一般使用者执行应用程序的环境。

如果在NSPE中执行的应用程序使用到secure层级的服务,则需要透过特定API来呼叫(这个概念类似操作系统的user-space和kernel-space会透过system call来沟通),这样可以限制NSPE的操作权限,避免重要机密资源外泄。

听起来有点抽象,那就来举个具体的例子吧!

应用场景

假设有一个应用场景是:一个应用程序需要使用硬件所保护的OTP(one-time programmable)securekey来进行数据的加解密。

执行流程

• 1、Task(应用程序)呼叫整合进RTOS的Crypto PSA(Platform Security Architecture)API,发出Crypto request。

• 2、TF-M core收到request,由context manager产生对应的request context(包含执行此request的stack、crypto service ID等)。

• 3、Crypto Service接收到此request,接着呼叫hardware API从OTP读取secure key并进行加解密算法。

• 4、加解密完成,Crypto Service将加解密后的结果透过context回传给Task。

如上述例子,由于重要的数据或是key仅能在SPE下存取,因此透过此构架来处理加解密需求,就能确保在NSPE执行的应用程序不会取得key。

其实这里和TFA是极其类似的思想。

-

处理器

+关注

关注

68文章

20327浏览量

254747 -

ARM

+关注

关注

135文章

9586浏览量

393509 -

API

+关注

关注

2文章

2469浏览量

66998 -

构架

+关注

关注

0文章

7浏览量

7228

发布评论请先 登录

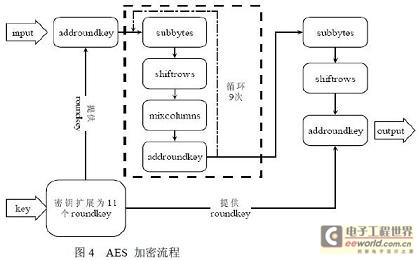

基于蜂鸟E203的AES加解密NICE协处理单元设计

labviewAES加解密小程序

基于FPGA的可编程AES加解密IP

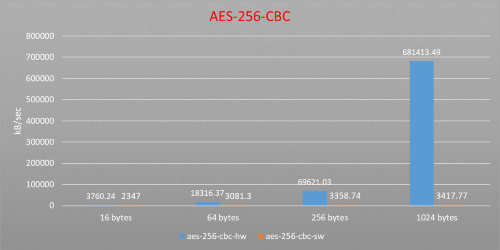

硬件加解密的分类

硬件加解密主要优点及引擎种类

STM32加解密技术

基于MEMS和FPGA的移动硬盘数据加解密系统

基于FPGA的可编程AES加解密IP

通过构架来处理加解密需求

通过构架来处理加解密需求

评论