什么是无杂散动态范围 (SFDR)?为什么SFDR很重要?

无杂散动态范围(SFDR)是指模拟信号中最大的无杂散动态范围。它是在硬件设备中测量的。它是指能够测量的模拟信号的最大幅度范围,其中没有杂散信号的干扰。SFDR是一个非常重要的概念,因为它描述了模拟信号处理系统的能力。在数字信号处理技术被广泛应用之前,模拟信号处理系统对于信号幅度范围有很高的要求,因此,SFDR是非常关键的指标。本文将详细探讨SFDR的相关知识,包括什么是SFDR、为什么SFDR很重要和如何测量SFDR。

一、何谓SFDR

无杂散动态范围是指模拟信号中最大的无杂散动态范围。它的含义是指在一个模拟系统中,输入信号的最大幅度与系统中出现的噪音的幅度之间的差异。 换句话说,SFDR表示了噪音与有用信号之间的差异。如果在一个模拟系统中使用低质量的信号处理器件,那么这种噪音可能非常大。在这种情况下,SFDR将非常低。另一方面,如果使用高质量的信号处理器件,噪声将非常小,SFDR将非常高。因此,SFDR是一个非常重要的指标,它可用于衡量模拟信号处理器件的质量。

二、SFDR的重要性

SFDR是一个非常重要的指标。它衡量了一个模拟信号处理系统的质量。如果SFDR非常低,那么意味着模拟信号处理器件将无法处理某些高幅度信号。这将导致信号失真、垃圾信息的插入,或者干扰其他信号。另一方面,如果SFDR非常高,那么意味着信号处理器件具有很好的质量和较高的性能。

在模拟信号处理系统中,信号强度的摆动范围是非常广泛的,有些信号的强度非常强,有些则很弱。如果信号处理系统的动态范围非常小,那么将导致很多强度很大的信号无法被识别。相反,如果信号处理系统的动态范围非常大,那么它可以很好的捕捉到信号,不论它们有多么强或弱。因此,SFDR是一个很重要的指标,它可以确保模拟信号处理器件具有足够的动态范围以适应信号的变化。

三、如何测量SFDR

如何测量SFDR是一个很重要的问题,因为测量SFDR要求高质量的信号处理器件和准确的测试设备。最常见的方法是使用频域分析仪。这种方法利用了信号的频率域特性,它通过将信号转换为频率域来进行分析。在频域分析中,可以识别出所有噪声元素和杂散信号,并确定它们的幅度和频率。然后,可以从信号的最大幅度和噪声的最小幅度之间计算SFDR。

四、结论

无杂散动态范围是一个非常重要的指标,它可以衡量模拟信号处理器件的质量。如果SFDR很低,那么会发生信号失真,垃圾信息的插入和干扰其他信号等问题。相反,如果SFDR高,那么模拟信号处理器件将具有更好的质量和更高的性能。测量SFDR的最简单方法是使用频域分析仪,它通过将信号转换为频率域来进行分析,从而可以确定信号幅度与噪声幅度之间的差距。

-

模拟信号

+关注

关注

8文章

1215浏览量

54393 -

信号处理器

+关注

关注

1文章

262浏览量

26111 -

SFDR

+关注

关注

0文章

52浏览量

13371

发布评论请先 登录

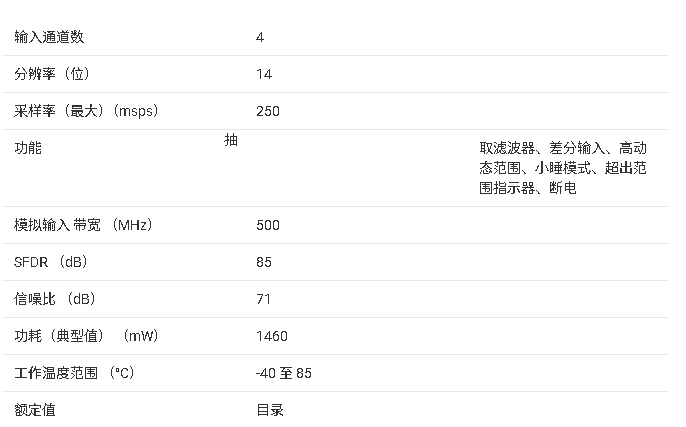

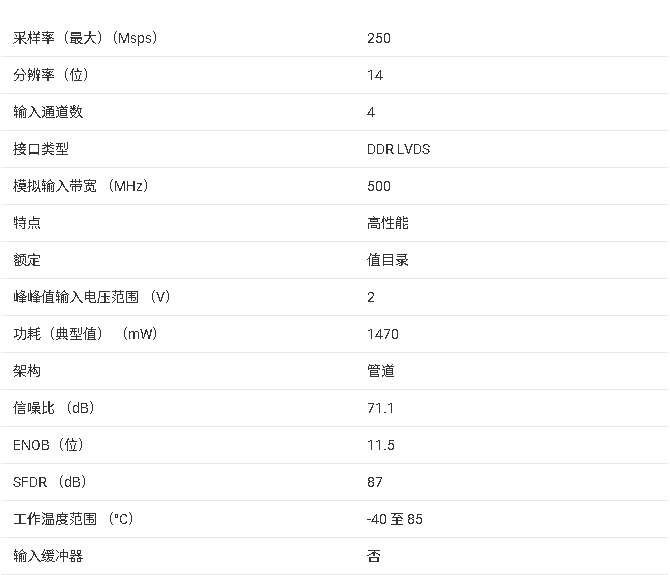

ADS58H40 四通道 250-MSPS 模数转换器技术规格与应用总结

无杂散、50 MHz 至 2.1 GHz 单通道小数 N 分频频率合成器 skyworksinc

什么是无杂散动态范围 (SFDR)?为什么SFDR很重要?

什么是无杂散动态范围 (SFDR)?为什么SFDR很重要?

评论