当使用上拉电阻和下拉电阻时,你需要理解它们的具体应用和原理以确保正确配置引脚,维持电平状态,并避免电路问题。以下是更详细的解释:

上拉电阻:

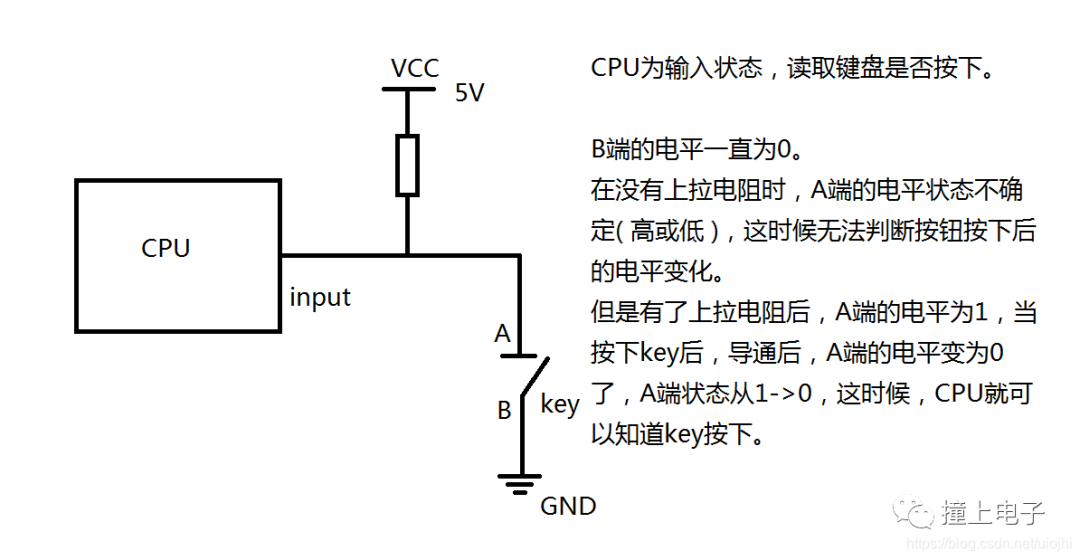

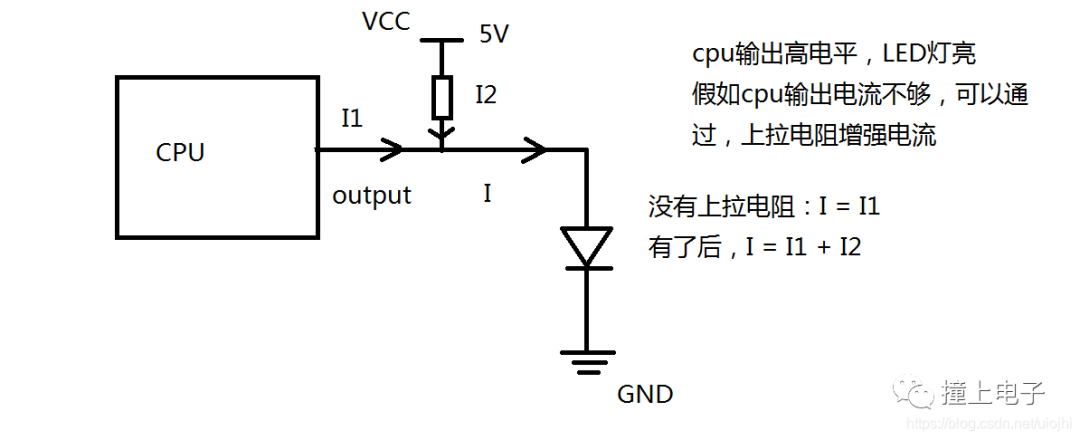

作用:上拉电阻用于保持引脚的电平在逻辑高("1")状态。它的主要作用是确保在没有外部输入信号时,引脚的电平保持高电平状态。原理:当引脚上拉电阻与电源电压(通常是Vcc或3.3V)连接时,引脚通过上拉电阻与电源电压相连。这使得引脚电平在没有外部信号输入时保持高电平。当外部事件将引脚连接到地(逻辑低)时,引脚的电平会变为低电平(逻辑"0")。应用:上拉电阻通常用于数字输入引脚,如按钮、开关或传感器。例如,当按钮未按下时,引脚保持在高电平状态。当按钮按下时,引脚的电平变为低电平,以表示按钮已被按下。下拉电阻:

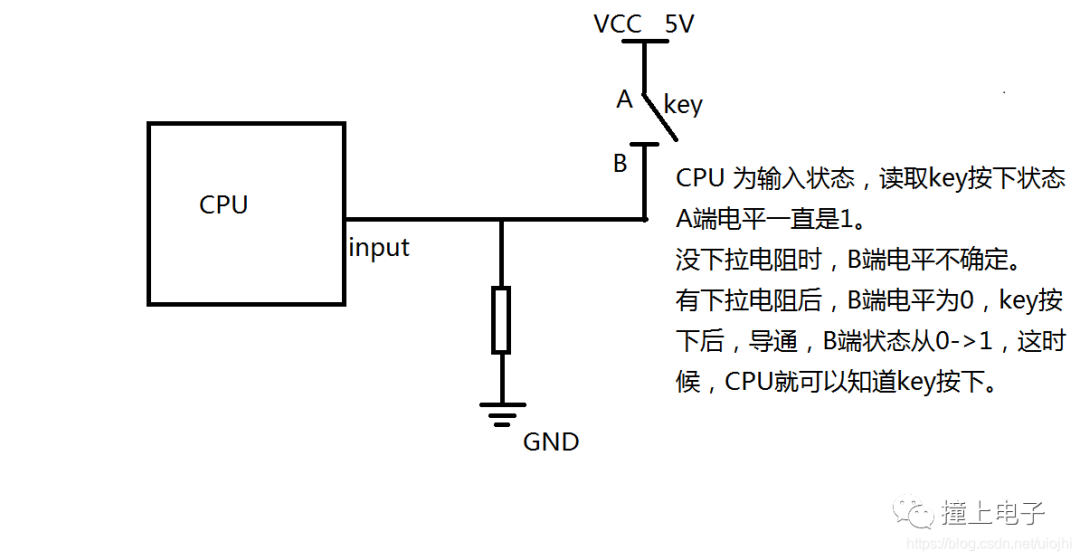

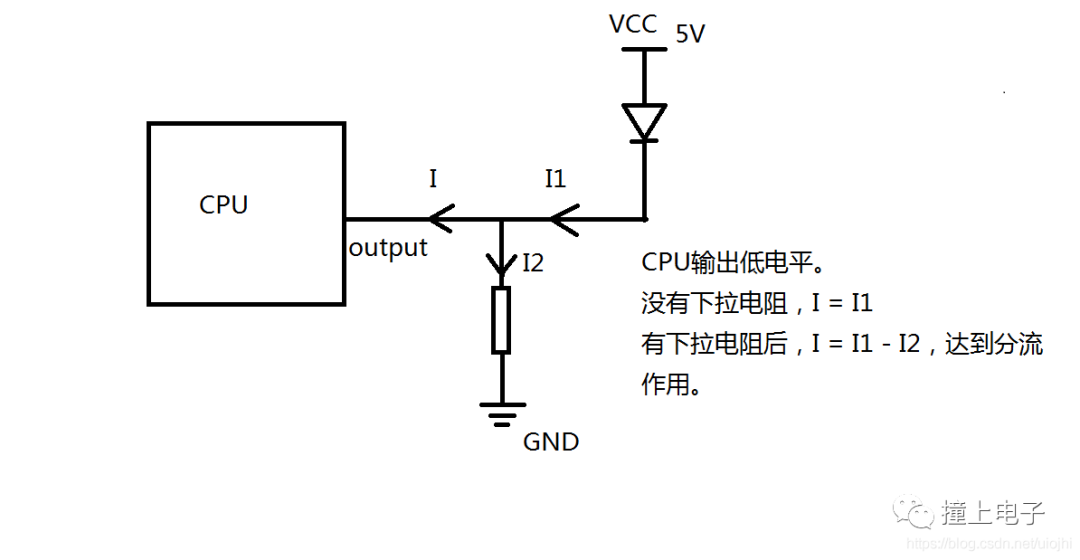

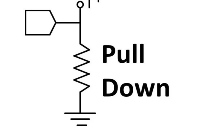

作用:下拉电阻用于保持引脚的电平在逻辑低("0")状态。它的主要作用是确保在没有外部输入信号时,引脚的电平保持低电平状态。原理:当引脚下拉电阻与地电压(通常是GND或0V)连接时,引脚通过下拉电阻与地电压相连。这使得引脚电平在没有外部信号输入时保持低电平。当外部事件将引脚连接到电源电压(逻辑高)时,引脚的电平会变为高电平(逻辑"1")。应用:下拉电阻通常用于数字输入引脚,如按钮、开关或传感器。例如,当按钮未按下时,引脚保持在低电平状态。当按钮按下时,引脚的电平变为高电平,以表示按钮已被按下。示例图示1,上拉电阻输入管脚

2,上拉电阻输出管脚

3,下拉电阻输入管脚

4,下拉电阻输出管脚

-

电阻

+关注

关注

88文章

5734浏览量

178557 -

电路

+关注

关注

173文章

6063浏览量

177473 -

电平

+关注

关注

5文章

370浏览量

41250

发布评论请先 登录

IO口8种工作模式和应用

CYW5557x 上的内部上拉/下拉电阻值是多少?

浮思特 | 电子电路下拉电阻详解:原理、计算与应用指南

CYUSB3065 (CX3) GPIO 所有输出都是推挽还是开漏? 需要配置外部上拉/下拉电阻吗?

三极管下拉电阻设计:稳定与效率的平衡艺术

上下拉电阻的原理和4种应用

上下拉电阻的原理和4种应用

评论