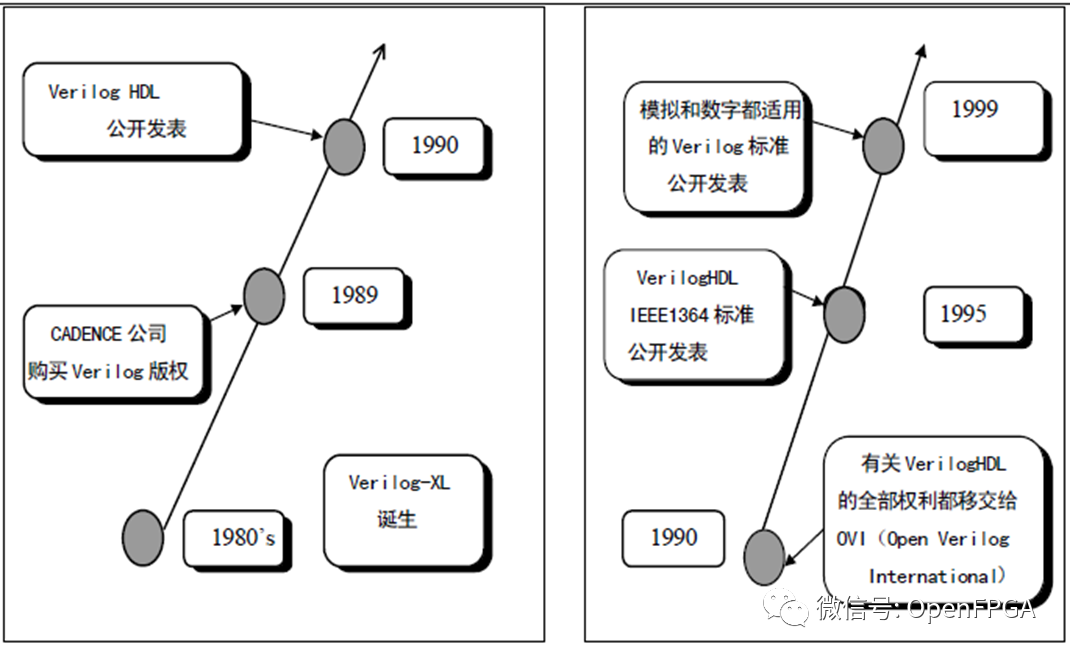

Verilog和System Verilog是同一硬件描述语言(HDL)的同义名称。SystemVerilog是IEEE官方语言标准的较新名称,它取代了原来的Verilog名称。Verilog HDL语言最初是于1 9 8 3年由Gateway Design Automation 公司为其模拟器产品开发的硬件建模语言。那时它只是一种专用语言。专有的Verilog HDL于1989年逐渐向公众开放,并于1995年由IEEE标准化为国际标准,即IEEE Std 1364-1995TM(通常称为“Verilog-95”)。IEEE于2001年将Verilog标准更新为1364-2001 TM标准,称为“Verilog-2001”。Verilog名称下的最后一个官方版本是IEEE Std 1364-2005TM。同年,IEEE发布了一系列对Verilog HDL的增强功能。

这些增强功能最初以不同的标准编号和名称记录,即IEEE Std 1800-2005TM SystemVerilog标准。2009年,IEEE终止了IEEE-1364标准,并将Verilog-2005合并到SystemVerilog标准中,标准编号为IEEE Std 1800-2009TM标准。2012年增加了其他设计和验证增强功能,如IEEE标准1800-2012TM标准,称为SystemVerilog-2012。在撰写本书时,IEEE已接近完成拟定的IEEE标准1800-2017TM或SystemVerilog-2017。本版本仅修正了2012版标准中的勘误表,并增加了对语言语法和语义规则的澄清。

verilog的发展历史及未来

原始Verilog

Verilog始于20世纪80年代初,是一家名为Gateway Design Automation的公司的专有硬件描述语言(HDL)。最初的Verilog HDL的主要作者是Phil Moorby。在20世纪80年代早期,数字仿真开始流行。一些电子设计自动化(EDA)公司提供了数字仿真器,但这些仿真器没有标准的硬件描述语言。相反,每个仿真器公司都提供了一种专用于该仿真器的专有建模语言。网表(Gateway)设计自动化也不例外。仿真器产品被命名为“Verilog XL”(Verification Logic,Accelerated的缩写),其附带的建模语言被称为“Verilog”。

Verilog XL仿真器和Verilog HDL在20世纪80年代后半期成为数字设计的主要仿真器和语言。促成这种流行的一些因素包括:1)速度和容量,2)ASIC定时精度,3)集成设计和验证语言,4)数字合成。

1、Verilog XL仿真器比大多数(如果不是全部的话)当代竞争对手的仿真器速度更快,设计容量更大,允许公司更有效地设计更大、更复杂的数字集成电路(IC)。

2、 在20世纪80年代后半期,许多电子设计公司正在从定制集成电路转向专用集成电路(ASIC)。网表(Gateway)设计自动化与主要ASIC供应商密切合作,Verilog XL成为确保ASIC仿真计时准确的黄金参考仿真器。ASIC供应商的这种偏好使Verilog成为COM的首选语言,COM是设计ASIC的公司。

3、20世纪70年代和80年代早期的主要数字仿真器通常涉及使用两种专有语言:门级建模语言来仿真数字逻辑,以及单独的专有语言来仿真刺激和响应检查。网关设计自动化背离了这一传统,将门级建模、抽象功能建模、刺激和响应检查集成到一种称为Verilog的语言中。

4、许多公司采用Verilog语言设计ASIC的第四个原因是能够将抽象的Verilog模型合成为门级模型。20世纪80年代后半期,Synopsys,Inc.与Gateway Design Automation达成协议,在Synopsys Design Compiler(DC)数字合成工具中使用专有的Verilog语言。与当时所有其他专有数字建模语言相比,仿真和合成Verilog语言的能力是一个巨大的优势。

开放verilog和VHDL

Verilog语言的快速增长和普及在20世纪90年代初突然放缓。电气和电子工程师协会(IEEE,通常发音为“I-triple-E”)发布了VHDL语言,作为第一个行业标准、非专有硬件描述语言。与Verilog类似,VHDL还提供了一种集成的数字建模和验证语言,并得到了ASIC供应商的支持(首先是在VHDL设计流程中使用经过认证的Verilog ASIC库)。随着VHDL仿真器和合成编译器的出现,许多设计公司开始回避使用专有语言,包括Verilog。还有一些其他因素,比如美国国防部(DOD)授权使用VHDL作为DOD设计的文档语言,也导致了从Verilog向VHDL的转变(DOD不要求设计工作使用VHDL,只要求最终文档使用VHDL)。

网关设计自动化公司(Gateway Design Automation)通过将Verilog发布到公共领域,阻止了这种远离专有HDL的做法。第一步工作就是要求将Verilog语言文档与Verilog XL仿真器产品文档分开。在这项工作进行期间,Cadence Design Systems得到Gateway Design Automation的请求并完成了这项工作;1991年,Verilog正式成为公共领域语言,成立了一个名为Open Verilog International(OVI)的非营利组织,目的是控制Verilog语言并促进其使用。

Verilog向公共领域的发布有效地阻止了Verilog向VHDL的流动。在接下来的二十年中,这两种HDL共存,并且可以说,在全球电子设计行业中保持了某种程度上均匀的总体使用。然而,2005年SystemVerilog的出现打破了VHDL的平衡,而Verilog在其新名称SystemVerilogt下再次成为数字设计和验证中使用的更主要的HDL语言。

IEEE Verilog-95和Verilog-2001

IEEE于1993年接管了Verilog语言,并在两年后发布了正式的IEEE Verilog HDL标准,即IEEE 1364-1995,昵称为“Verilog-95”。五年后,IEEE发布了1364-2001,绰号为“Verilog2001”,其中有许多用于建模和验证数字设计的增强功能。

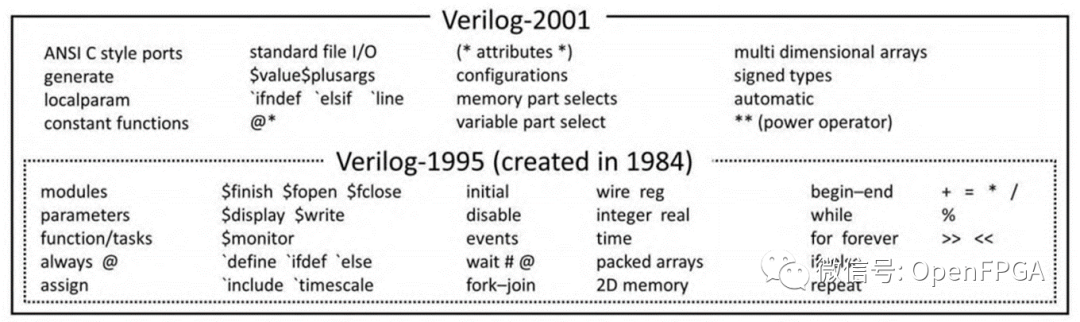

图1-1显示了Verilog-95中的主要语言功能,以及Verilog-2001中添加的主要新功能。请注意,此图并不是语言特性的全面列表。其目的是展示Verilog-2001添加到原始Verilog语言中的主要新功能。

图1-1:Verilog-95和Verilog-2001语言特性

SV向Verilog扩展-一个单独的标准

到2001年,典型数字集成电路的规模和复杂性从20世纪80年代开始发生了巨大的变化,当时Verilog和VHDL语言都是第一次出现。即使在Verilog-2001中增加了新功能,有效地建模这些大型设计以及验证这些复杂设计所需的大量激励和反复检查代码也变得越来越困难,为了解决Verilog-2001的语言局限性,Accellera开始为Verilog语言定义大量新功能。”这些扩展被概括为两个主要类别:

增强功能主要满足更高效、更准确地建模数字逻辑功能的需要。

为大型复杂设计编写高效广泛验证代码的功能增强。

定义下一代Verilog的最初工作是在IEEE之外完成的,由一个名为Accellera(现为Accellera Systems Initiative)的独立非营利组织完成。Accellera是一个think-tank组织,由开发电子设计自动化(EDA)软件工具的公司和使用这些软件工具的公司的代表组成。Accelera成立于20世纪90年代中期,由Verilog和VHDL用户组合并而成。后来,其他EDA小组也并入了Accelera,如SystemC Initiative。Accelera负责目前使用的许多EDA工程标准的初始开发工作。许多Accelera标准最终“成为IEEE标准”。

2002年末,Accellera发布了这些主要扩展的第一个版本,该版本将添加到IEEE Verilog-2001语言中。在Verilog-2001扩展的开发过程中,这些新的语言功能被称为“Verilog++”,但在最后一刻决定将这些扩展发布为“SystemVeriIog 3.0”。选择使用是为了表明,当扩展与Verilog结合时,它将是Verilog语言的第三代(Verilog-95是第一代,Verilog-2001是第二代),B Accellera继续定义对Verilog的更多扩展,一年后,在2003年发布了SystemVerilog 3.1标准。

需要注意的是,Accellera SystemVerilog 3.1文档不是一种完整的独立语言,它是IEEE 1364-2001 Verilog语言的一组扩展。Accellera最初的意图是,IEEE随后将这些扩展添加到下一版本的IEEE 1364 Verilog标准中,目标是1364-2005,昵称为Verilog-2005。然而,出于多种原因,IEEE Verilog标准委员会决定不立即将这些扩展合并到实际的Verilog 1364标准中。相反,IEEE为这些扩展指定了一个新的标准编号,在2005年,IEEE发布了1364-2005 Verilog标准,同时发布了1800-2005 SystemVerilog对Verilog标准的扩展。

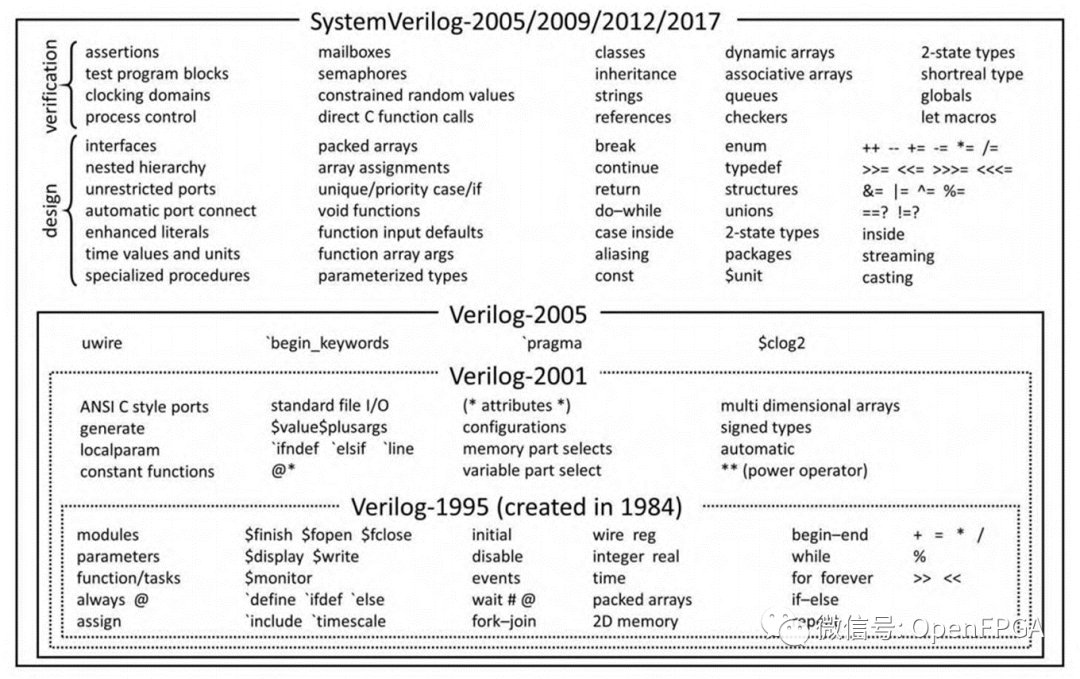

图1-2显示了SystemVerilog添加到Verilog-2001的主要功能。该图还显示,Verilog 1364-2005中包含了4项功能,而不是SystemVerilog 1800-2005标准。图1-2没有描述SystemVerilog的2005、、2009、 2012和2017版本之间的关系。SystemVerilog添加到传统Verilog中的大多数新功能都是在SystemVerilog-2005版本中实现的。2009和2012版本中只添加了少量附加功能,2017版本中没有添加任何新功能。

图1-2:带有SystemVerilog语言扩展的Verilog-2005

SystemVerilog取代Verilog

在发布这两个独立的标准后,IEEE立即开始将这两个标准合并在一起,合并了这两个大型文档。除了合并这两个标准外,IEEE还定义了许多附加SystemVeriIog功能(西蒙·戴维曼(Simon Davidmann)是数字仿真领域的早期先驱之一,他就Verilog和SystemVerilog的起源写了一本更详细的历史书,可以在《System Verilogfor Design,Second Edition》一书的附录中找到。)。合并后的Verilog和SystemVerilog标准作为IEEE 1800-2009 SystemVerilog标准发布。当时,IEEE终止了旧的Verilog-1364标准。“Verilog”的名称正式成为“SystemVerilog”。

硬件设计和验证这些设计的复杂性在不断发展,IEEE也在不断发展SystemVerilog标准以跟上步伐。2012年,IEEE发布了1800-2012 SystemVerilog标准。SystemVerilog-2017版本主要对SystemVerilog标准进行了修正,并未在2012标准中添加任何新的语言功能。

IEEE在2005年决定发布两个独立的标准——一个包含传统的Verilog语言(1364-2005),另一个只包含Verilog的扩展,称为SystemVerilog(1800-2005)——这让工程师们感到困惑。一个普遍存在的误解是Verilog是一种硬件建模语言,SystemVerilog是一种验证语言。这种理解是不对的!最初的Verilog语言始终是一种集成的建模和验证语言。SystemVerilog以实质性的方式扩展了原始Verilog HDL的建模方面和验证方面。SystemVerilog既是一种数字建模语言,也是一种数字验证语言。

审核编辑:刘清

-

FPGA设计

+关注

关注

9文章

431浏览量

28209 -

仿真器

+关注

关注

14文章

1052浏览量

88186 -

HDL语言

+关注

关注

0文章

48浏览量

9377

原文标题:谈谈Verilog和SystemVerilog简史,FPGA设计是否需要学习SystemVerilog

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

FPGA设计是否需要学习SystemVerilog

FPGA设计是否需要学习SystemVerilog

评论