请问双口RAM能用来进行跨时钟域传输数据吗?

双口RAM是一种用于在两个时钟域之间传输数据的存储器,因此它确实可以用于跨时钟域传输数据。在本篇文章中,我们将深入探讨双口RAM的工作原理以及如何利用它来进行跨时钟域传输数据。

一、双口RAM的工作原理

双口RAM是一种有两个读写口的存储器,因此可以在两个时钟域之间传输数据。它通常由一个存储单元阵列和控制逻辑电路组成。其中,存储单元阵列负责存储数据,控制逻辑电路则负责管理存储单元阵列和控制两个读写口的数据传输。

在双口RAM中,有一个时钟信号,被称为主时钟(CLKA),控制写入和读取数据的时序。主时钟和另一个时钟信号,被称为次时钟(CLKB),可以有不同的频率和相位。从而使得在两个不同的时钟域中可以并发地进行数据读写操作。

当从A端向B端写入数据时,数据会被存储在存储单元阵列中,并且通过控制逻辑电路,实现从A端到B端的数据传输。类似地,从B端向A端写入数据时,数据也会被存储在存储单元阵列中,并通过控制逻辑电路从B端到A端传输数据。

二、使用双口RAM进行跨时钟域传输数据

在实际应用中,双口RAM可以被用于跨时钟域传输数据。当我们需要在两个时钟域之间传输数据时,可以使用双口RAM将数据存储在中间缓存中,然后转移到目标时钟域。这个过程称为“双口RAM作为数据交换器”。

在使用双口RAM进行跨时钟域传输数据时,需要注意以下几点:

1. 时钟域转换

由于操作时钟不同,我们需要确保在两个时钟域中的数据传输操作在时间上是协同的。为此,需要使用时钟域转换电路将一个时钟域的信号转换为另一个时钟域的信号。

2.数据抖动

在双口RAM中,数据传输操作时间会受到时钟抖动的影响。因此,需要对时钟进行周期性重新校准,以避免数据丢失或传输错误。

3.数据宽度匹配

由于双口RAM的数据位宽是固定的,因此需要确保在传输数据时,源和目标数据位宽是匹配的。如果不匹配,则需要进行数据转换或者使用多个双口RAM进行数据传输。

三、总结

双口RAM能够在两个时钟域之间传输数据。它基于存储单元阵列和控制逻辑电路,可以实现在两个时钟域中并发地进行读写操作。在使用双口RAM进行跨时钟域传输数据时,需要进行时钟域转换、重校准时钟抖动以及确保数据宽度匹配等处理。双口RAM作为数据交换器在硬件设计中有着广泛的应用,实现了在不同时钟域之间的数据交换。

-

存储器

+关注

关注

39文章

7755浏览量

172177 -

RAM

+关注

关注

8文章

1400浏览量

120989 -

时钟信号

+关注

关注

4文章

510浏览量

30078

发布评论请先 登录

为何跨复位域问题是危险的“芯片杀手”

关于1061双网口配置问题求解

机器视觉网卡的双口、单口有什么区别?双口网卡适合哪些场景?

两个MCU之间快速传输数据的方法

位域解读

基于FPGA的高效内存到串行数据传输模块设计

数据预处理软核加速模块设计

使用MCU200T开发板的UART口进行数据传输

ram ip核的使用

SPI以太网口芯片DM9051ANX在ESP32 C3进行iPerf测试

黑芝麻智能跨域时间同步技术:消除多域计算单元的时钟信任鸿沟

【RK3568+PG2L50H开发板实验例程】FPGA部分 | ROM、RAM、FIFO 的使用

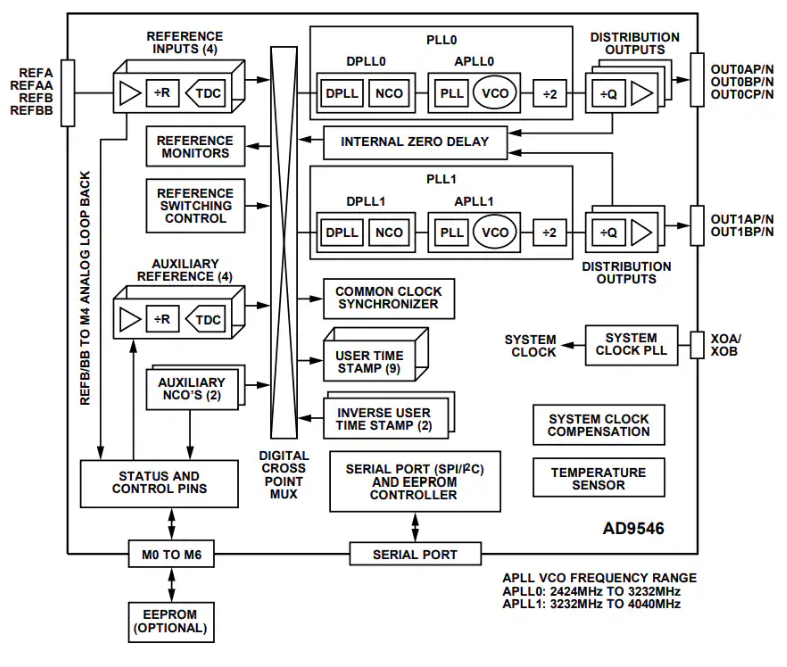

Analog Devices Inc. AD9546双通道DPLL 数字化时钟同步器数据手册

跨异步时钟域处理方法大全

请问双口RAM能用来进行跨时钟域传输数据吗?

请问双口RAM能用来进行跨时钟域传输数据吗?

评论