摘要:

本文将带你了解高低频的阻抗匹配电路概念及要点,最后从阻抗匹配的角度分析高速电路的振铃产生原因及解决办法。

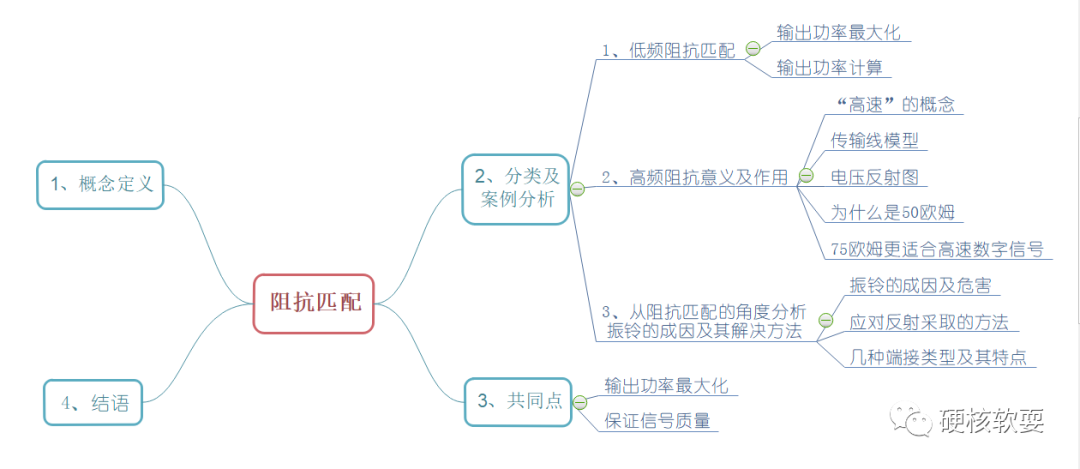

本章的思维导图如下:

一、阻抗匹配相关概念

在具有电阻、电感和电容的电路里,对交流电所起的阻碍作用叫用阻抗,常用Z来表示。阻抗的大小由交流电的频率f、电阻R、电感L、电容C共同决定。一个具体的电路,其阻抗随交流电频率的改变而改变。

1、输入阻抗

输入阻抗是指一个电路输入端的等效阻抗。其计算方法为:在输入端加上一个电压源u,测量输入端的电路i,则输入阻抗Zi = u / i。直流情况下,输入端等效为一个电阻,这个电阻的阻值就是输入阻抗的大小。

输入阻抗等同于电抗元件,反映的是对电流阻碍作用的大小。对于电压驱动电路,输入阻抗越大,对电压源的负载越轻,越容易被驱动,对信号源的影响越小;对于电流驱动电路,输入阻抗越小,对电流源的负载越轻,越容易被驱动,对信号源的影响越小。

对于低频电路,一般情况下可以认为:如果是用电压源来驱动的,则输入阻抗越大越好;如果是用电流源来驱动的,则阻抗越小越好。

对于高频电路,过高的输入阻抗会造成信号的反射,导致振铃和过冲,造成信号完整性问题。

无论高、低频电路,如果要获取最大输出功率,都需要做阻抗匹配。

2、输出阻抗

实际的信号源、放大器或者电源,都存在输出阻抗(理想的电压源输出阻抗为零),输出阻抗就是源的内阻。我们常用一个理想电压源串联一个电阻Rs来等效一个实际的电压源,这个Rs就是电压源的内阻。当电压源向负载供电时,由于电流I经过Rs,根据欧姆定律,Rs上的电压为 U(Rs) = I x Rs,导致负载上的电压小于电压源电压,即负载电压下降了。

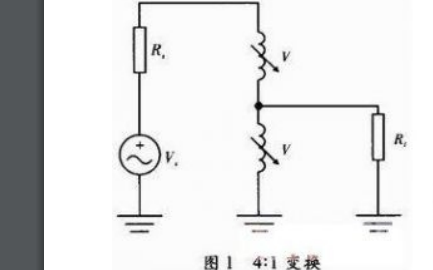

3、阻抗匹配

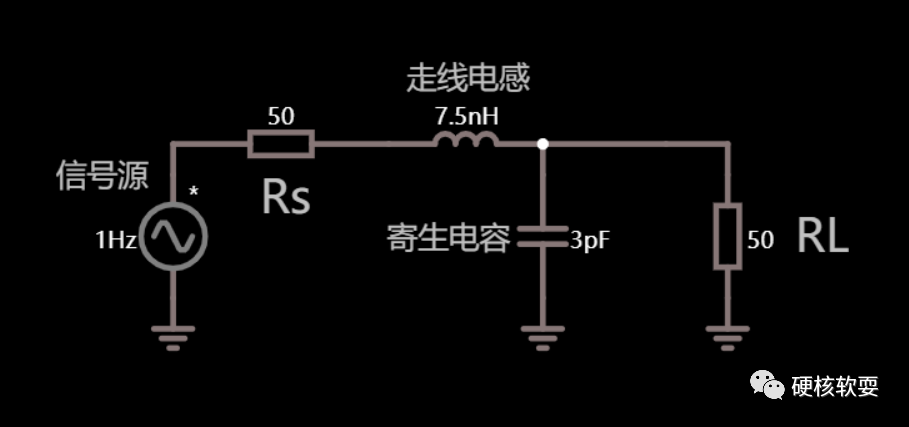

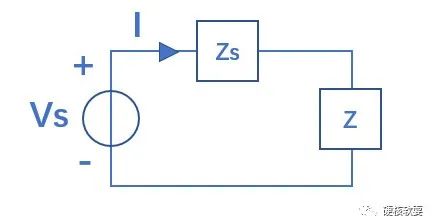

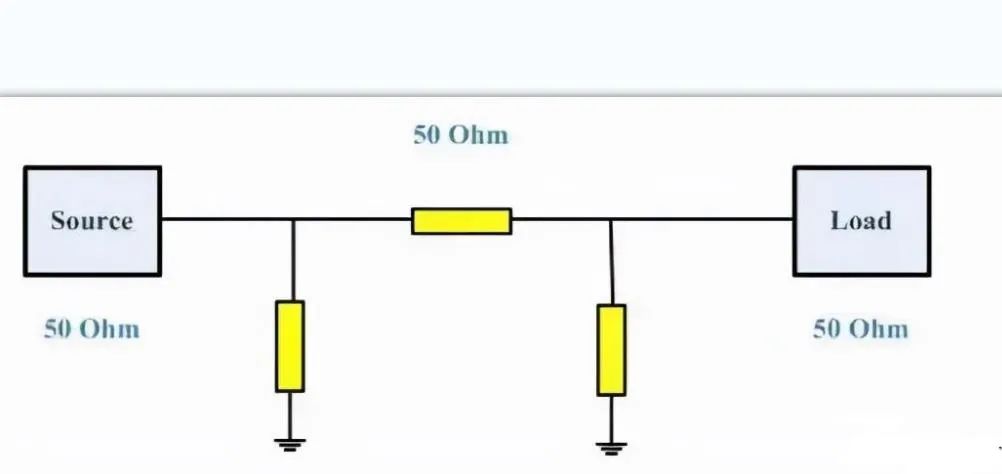

阻抗匹配是指信号源或者传输线跟负载之间的一种合适的搭配方式。无论高低频电路,源与负载之间的关系均可等效于以下电路(元器件参数可变):

图1

二、阻抗匹配分类

1、低频下的阻抗匹配

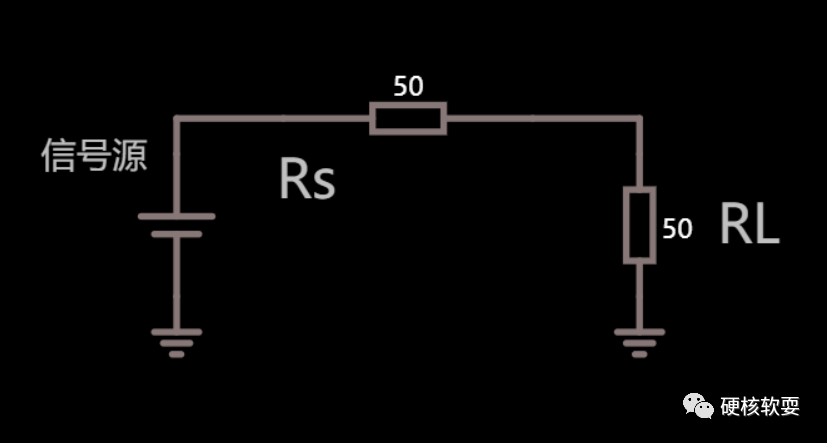

当信号源频率低时,寄生电感阻抗极小等效于短路,寄生电容阻抗极大等同于开路,于是图1可以简化为以下电路:

图2

将信号源看成直流电压源进行分析,Rs为电压源的内阻,负载为RL,电压源电动势设为U,则回路电流 I = U / (Rs + RL),由式子可以看出,回路电流由电压源内阻和负载共同决定,当Rs一定时,Rl越大,电流I越小,反之则I越大。 负载与电压源及其内阻构成串联电路,RL与Rs按照它们的电阻值比值共同分配电压源的电压,RL越大,则负载上的电压越大。这里需要注意的是, 负载分到的电压大不等于负载消耗的功率也大 ,因为功率不仅与电压有关,还和电流相关,此处计算负载上的功率 :

P = U*I

= I^2 * RL

= [ U / (Rs + RL) ]^2 * Rl

= U^2 / { [RL-Rs]2 / RL] + 4Rs }

可以看出,当负载电阻跟信号源内阻相等时,负载可获得最大输出功率,这就是我们常说的阻抗匹配之一。当然,如果我们想要负载电压大,就选择阻值大的负载。

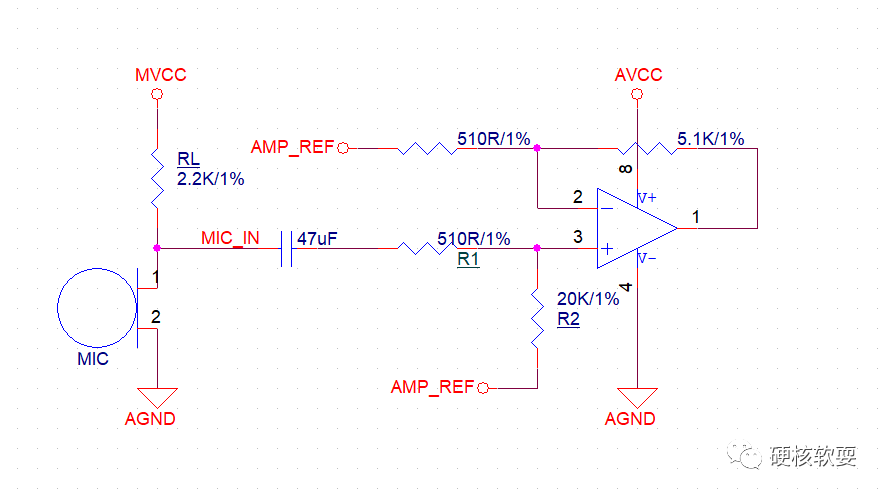

举例麦克风放大电路分析输入阻抗、输出阻抗以及阻抗匹配的关系:

图3

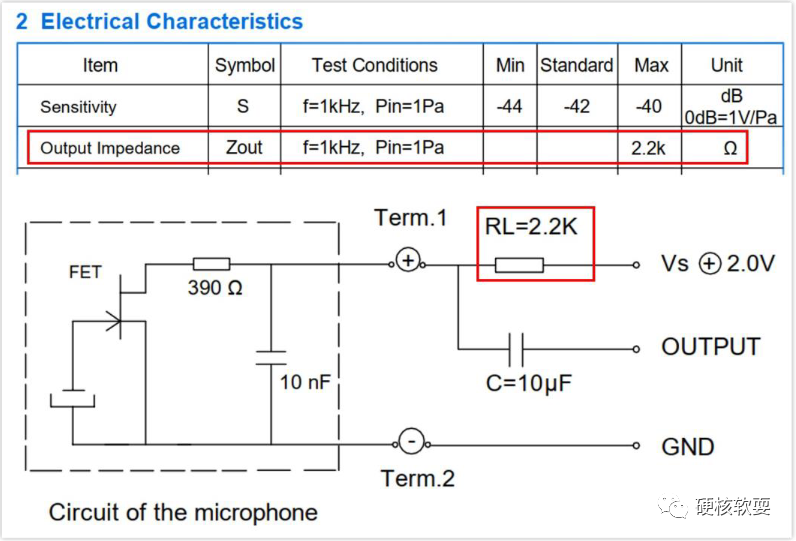

先看一下MIC的内部电路:

图4

如图,芯片规格书也提供了咪头的内部电路,其实就是个FET管放大电路。如果好好学习的话(论大学好好学习的重要性),就知道这个FET管放大电路的输出电阻就是那个RL,厂家这个RL是2.2KΩ,所以它就标注输出阻抗是2.2KΩ。

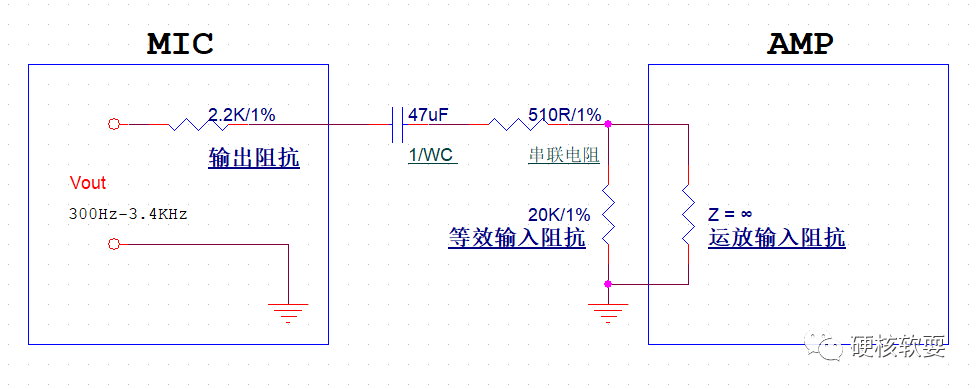

再看信号的通路,信号从咪头出发通过电容,在两个电阻分压后输入到运放的同相端,由于运放的同相端输入阻抗无穷大,所以分析阻抗时可视为断路,则信号通路可等效为以下电路:

图5

由图可见,MIC的输出阻抗、电容容抗、串联电阻R1(510Ω)及R2(20K)构成串联分压电路,信号在R2上的分压输入到运放的同相端。因为运放的输入阻抗很大(MΩ级别),所以信号输入到运放的等效输入阻抗为R2,即20KΩ。如果我们想要输入信号不能过小,那么R2不能用小电阻,不然达不到设计的放大目标,这种达不到设计性能的情况,也可以叫做阻抗失配。当然此处还有一个小细节,为什么要加上R2呢?如果断开R2,则MIC的信号几乎是全部输入到运放,但是因为运放的输入阻抗很大,容易把干扰也放大,所以用外部电阻R2调节信号的输入阻抗。

2、高频下的阻抗匹配

当信号源频率极高时,串联寄生电感阻抗不可忽略不计,并联寄生电容阻抗不可视为无穷大,若仅仅考虑内阻与负载的关系,忽略实际走线的寄生电感和寄生电容,当源阻抗和负载为复数时,则图1可以化成以下电路:

图6

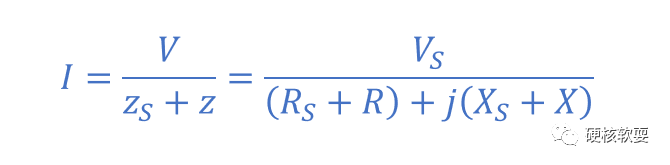

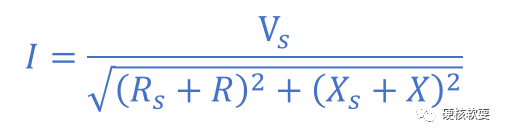

其信号源电压为Vs,信号源内阻为Zs = Rs + jXs,负载阻抗为Z = R +jX,电路中的电流为:

电流的幅度值为:

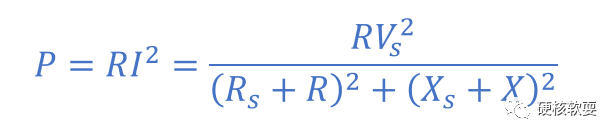

负载处的功率为:

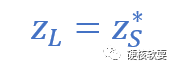

参照前文得到的结论,当R = Rs,X = -Xs时,负载的功率最大,即输出功率最大。这时有:

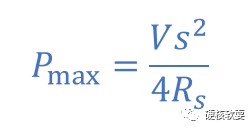

即信号源内阻与负载进行了共轭匹配,此时负载功率为:

Q:如果负载阻抗不能满足共轭匹配条件怎么办?

A:很简单,在源与负载之间加匹配网络,将负载阻抗变换成信号源阻抗的共轭匹配。这个阻抗变换是阻抗匹配的重要方法之一。

三、高速电路的反射及阻抗匹配

1、高速电路相关概念

1.1 集总参数电路与传输线

随着频率的提高,一般到十几兆开始,信号的传输不再是电压和电流,而是依靠电场和磁场传播,电磁场被锁定在导线和参考地之间。由于具有这种高频效应,若等效为电路的话,导线上各个位置处的电压不同(周期重复点除外),各个位置的电流也不同,这是与集总参数电路的明显区别,这种情况下称为分布参数电路,导线称为传输线。

若用 l表示电路本身的最大线性尺寸,用λ表示电压或电流的波长,则当不等式 λ>>l 成立,电路便可视为集总参数电路,否则便需作为分布参数电路处理。

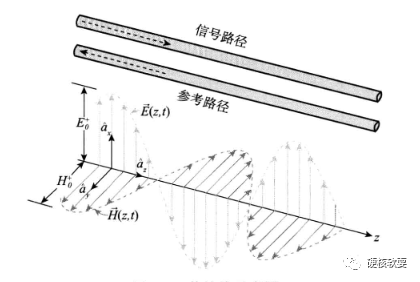

最简单的传输线由一对导体构成,把信号以电磁波的形式从一端送到另一端。构成传输线的形式多种多样,比如,PCB上的走线、双绞线、同轴电缆等。图7为传输线结构的简单示意图,两个导体中一个称为“信号路径”,另一个称为“参考路径”或者“返回路径”。两个导体构成了电磁波能够向前传播的物理环境,图7中同时画出了某一特定时刻电场强度和磁场强度沿空间分布的情况。当传输线上施加信号时,随着信号向前传播,沿空间分布的电场和磁场也发生变化,信号能量以电磁波的形式传输到末端。变化的电场和磁场产生电流,外在的表现就像是电流端从信号路径流入,然后从参考路径流回到发送端一样,这也是“参考路径”被称为“返回路径”的原因。

图7

传输线的行为特征和电容、电感、电阻等集总元件有非常显著的区别,必须用“动态”的思维才能理解传输线的特性。

1.2 高速与高频的关系

高速与高频的关系可以用两句话概括:

- 高速不等同于高频

- 高频是高速的载体

随着现代制程的缩小,电平跳变比以前更快,一些低频器件也要当成高速电路对待。举个栗子,1MHz的方波频率只是1MHz,但是边沿十分陡峭,这也意味着方波中含有丰富的高次谐波,高次谐波的频率远远大于1MHz,所以,高速的划分不能仅仅以频率来做界定。

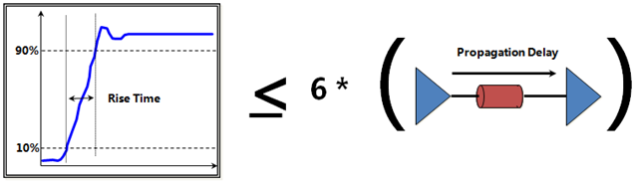

“那我们所说的高速设计的边界条件是什么呢?小陈认为是分布参数,传输线理论中的‘长线’,是上升时间小于六分之一传输线延时”——引自《高速先生》

图8

那么多长才算长线呢?

PCB上信号传输速度为6inch/ns,也就是0.1524m/ns,如果我们知道上升沿时间,根据公式 t < 6*L/(0.1524m) 便可算出长度值。

当前常规的时钟芯片,上升沿通常在2ns左右,在这些信号眼中,2000mil以上叫做长线。一些新的时钟芯片,虽然速率可能只有几十兆,但是芯片工艺有较大的改进上升沿较快,可能会达到400ps,在这些信号眼中,400mil以上叫做长线。与其上升时间相当的,还有大部分LVDS信号等。

当前DDR3,上升沿通常在100ps左右,在这些信号眼中,100mil以上叫做长线。对于10G信号来说,上升沿通常在25ps左右,这时候,25mil叫做长线。

2、高速电路的反射

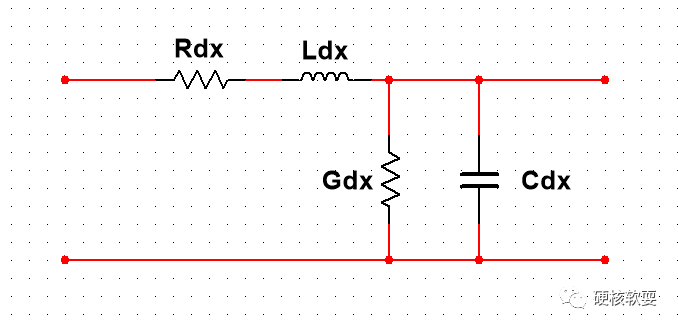

前文说过,高频是高速的载体,在分析高速电路时,从高频信号入手,当信号频率极高时,传输线上的寄生电感和寄生电容的阻抗影响不可忽略。可以用下图模型来表示单位长度的传输线:

图9

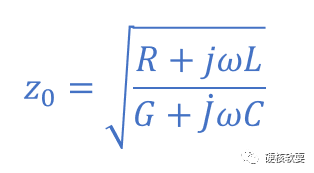

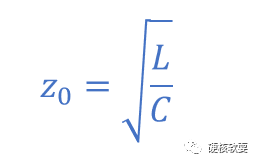

此模型下的特征阻抗表达式为:

在实际的PCB应用中传输线的电阻部分,可以忽略不计,即上式中的R和G为0,PCB传输线特征阻抗的一般表达式:

L是单位长度传输线的固有电感,C是单位长度传输线的固有电容。

需要注意的是,只有在传输线均匀的情况下才存在特征阻抗,即信号不论走到传输线的什么位置,感受到的阻抗都是相同的,即Z0。通常我们说的50Ω阻抗控制就是指特征阻抗。如果传输线非均匀,那么信号在这个传输线上传输到不同位置时感受到的瞬态阻抗不同,因此没有特征阻抗。

反射

信号在不均匀的传输线上传输,在不同位置感受到的瞬态阻抗不同导致反射,即阻抗不连续导致反射。

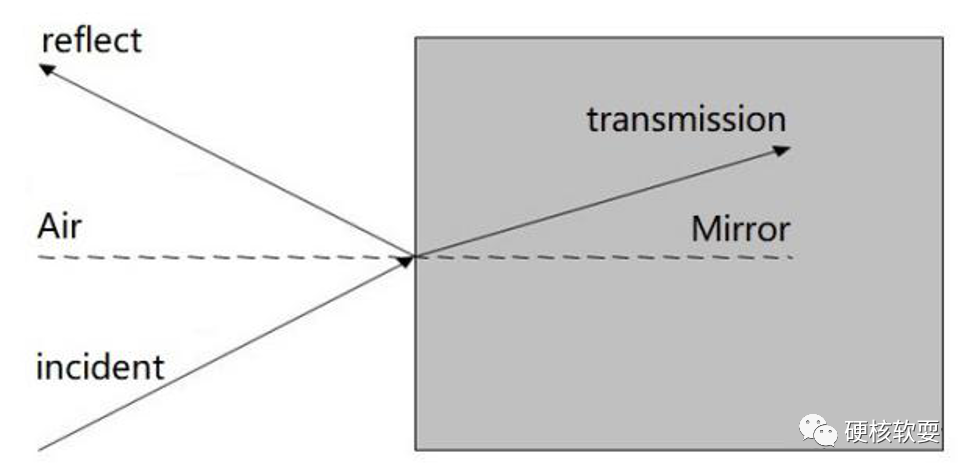

反射现象在自然界中普遍存在,例如光在不同介质中传播时发生反射,当光从空气射向玻璃,因为空气和玻璃是两种不同的介质(换言之,阻力不同),有一部分光被反射,另一部分光会折射进入另一种介质,如下图:

图10

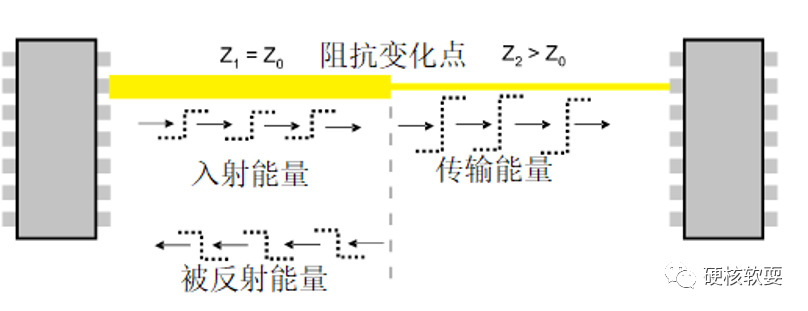

同样地,信号也一样,如果传输线的阻抗不一致,在阻抗跳变的地方,一部分能量继续传输,一部分能量会被反射回去,如下图:

图11

下面让我们用更严谨的理论和物理定理公式证明上述的观点正确:

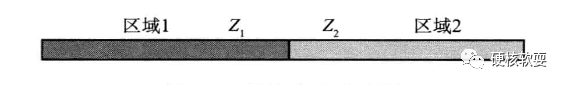

假设信号传输过程中,经过两个阻抗不同的区域,如图12所示,区域1阻抗为Z1,区域2阻抗为Z2,现在我们考察在区域分界面处的电压电流情况。

图12 阻抗突变示意图

很明显,在分界面处,电压必须是连续的,否则,在分界面处会产生无穷大的电场,这在真实世界中是不可能的。同样,分界面两侧的电流必须连续,否则分界面处会产生无穷大的磁场(这听起来是不是和“电容电压不能突变,电感电流不能突变“有联系,感兴趣的同学可以深入研究背后的奥妙~)。

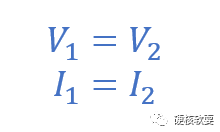

因此,下式1成立:

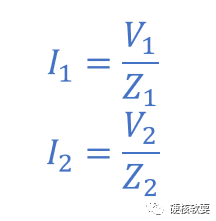

根据欧姆定律,必然有式2:

显然如果Z1≠Z2的情况下,上面的1、2式子不可能同时成立。如何解决这一困境?反射理论提供了一个很好的答案。从电磁波的角度来理解反射,在分界面处,一部分正向传播,另一部分反向传播。从电压电流角度,我们可以把区域1的电压V1分成两部分,一部分以电压Vinc正向传输,另一部分以电压Vreflect反向传输。其中Vinc称为入射电压,Vreflect称为反射电压。而V2记为Vtrans,称作传输电压。

由于分界面两侧电压相等,所以有式3:

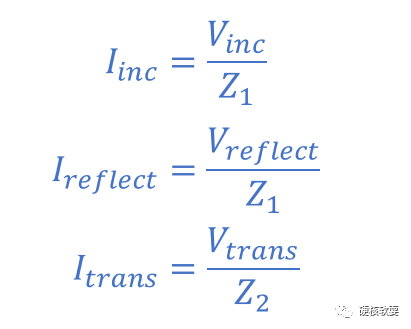

同理,入射电压Vin产生一个正向电流Iinc,反射电压Vreflect产生一个反向电流Ireflect。区域2的电流记为Itrans,要使分界面两侧电流相等,必有式4:

由此可得,任一截面处的电压或者电流都是入射波和反射波叠加的结果。

根据欧姆定律,有式5:

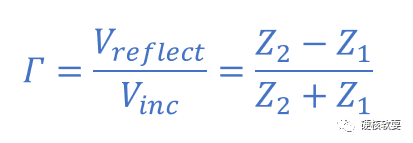

联合3、4、5式可得式4、式5:

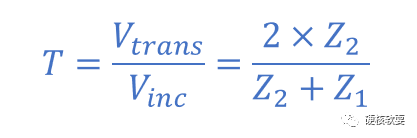

Γ称为反射系数,T称为传输系数。

当反射系数Γ ≠ 0,必然存在阻抗不连续点并引起信号反射。

3、反射的危害

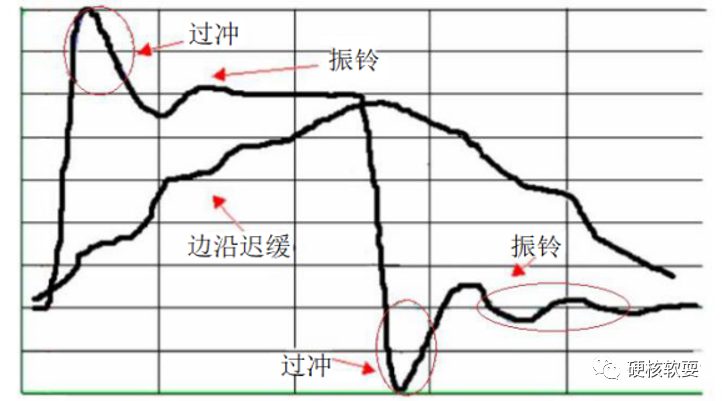

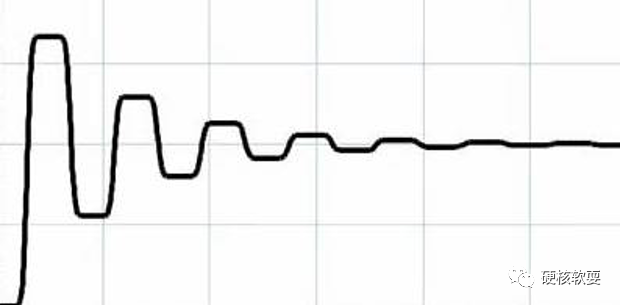

反射会造成信号出现过冲(Overshoot)、振铃(Ringing)、边沿迟缓(回勾现象)。过冲是振铃的欠阻尼状态,边沿迟缓是振铃的过阻尼状态。下图为信号反射的三种表现形式:

图13

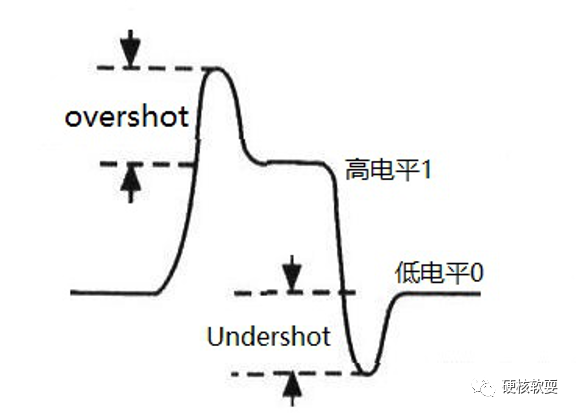

3.1 过冲和下冲

过冲指的是第一个峰值或谷值超过设定电压值,下冲是指下一个谷值或峰值,对于上升沿来说,过冲是指最高电压;对于下降沿来说,过冲是指最低电压。如下图所示:

图14

过冲严重时会引起保护二极管工作,导致过早地失效,严重时还会损坏器件。而过分的下冲,能够引起假的时钟或数据的错误,这样可能会给器件带来潜在的累积性伤害,缩短其工作寿命,从而影响产品的长期稳定性。一般信号的发送端的阻抗较低,信号接收端的阻抗较高,如果发送端的与接收端的阻抗不匹配,发送的信号会在发送端和接收端之间来回反射,从而导致信号的反射出现过冲和下冲。

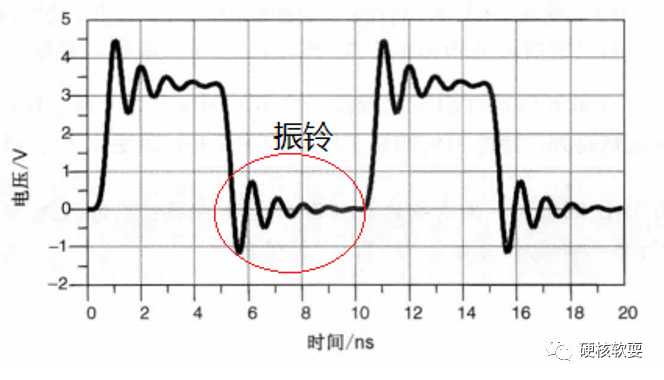

3.2 振铃

过冲和下冲反复就会出现振铃现象,过冲往往伴随有振铃,或者说,过冲是振铃的一部分。振铃产生的第一次峰值电压,就是过冲。为什么要将过冲和振铃分开来讲,是因为他们的危害不同,振铃除了具有过冲的危害之外还有它的波动可能会多次超过阈值判定电压造成误判,并且会急剧地增加功耗,影响器件寿命。下面是振铃的表现形式:

图15

4、深入探究反射的过程及解决方法

4.1 理想的源->负载传输模型

最理想模型是希望源端(Source)的输出阻抗为50欧姆,传输线的阻抗为50欧姆,负载端(Load)的输入阻抗也是50欧姆,一路50欧姆下去,这是最理想的。

图16

至于为什么是50欧姆,这里有个故事……

我们知道射频的传输需要天线和同轴电缆,射频信号的传输我们总是希望尽可能传输更远的距离,为了传输更远的距离,我们往往希望用很大的功率去发射信号便于覆盖更大的通信范围。可是实际上,同轴电缆本身是有损耗的,和我们平常使用的导线一样,如果传输功率过大,导线会发热甚至熔断。这样,我们就有一种期望,试图寻找一种能够传输大功率,同时损耗又非常小的同轴电缆。

图17

大概在1929年,贝尔实验室做了很多实验,最终发现符合这种大功率传输,损耗小的同轴电缆其特征阻抗分别是30欧姆和77欧姆。其中,30欧姆的同轴电缆可以传输的功率是最大的,77欧姆的同轴电缆传输信号的损耗是最小的。30欧姆和77欧姆的算术平均值为53.5欧姆,30欧姆和77欧姆的几何平均值是48欧姆,我们经常所说的50欧姆系统阻抗其实是53.5欧姆和48欧姆的一个工程上的折中考虑,考虑最大功率传输和最小损耗尽可能同时满足。而且通过实践发现,50欧姆的系统阻抗,对于半波长偶极子天线和四分之一波长单极子天线的端口阻抗也是匹配的,引起的反射损耗是最小的。

我们常见的系统中,比如电视TV和广播FM接收系统中,其系统阻抗基本上都是75欧姆,正是因为75欧姆射频传输系统中,信号传输的损耗是最小的,TV和广播FM接收系统中,信号的传输损耗是重要的考虑因素。而对于带有发射的电台而言,50欧姆是很常见的,因为最大功率传输是我们考虑的主要因素,同时损耗也比较重要。这就是为什么我们的对讲机系统中,经常看到的都是50欧姆的参数指标。

虽然50欧姆的指标比较常见,但75Ω电缆更适合于高频数字信号,因为75Ω同轴电缆的电容比50Ω同轴电缆的电容低(同轴传输线结构决定),而更低的电容有利于避免与逻辑低和逻辑高之间的快速过渡相关的高频内容过度衰减。

4.2 实际的传输模型

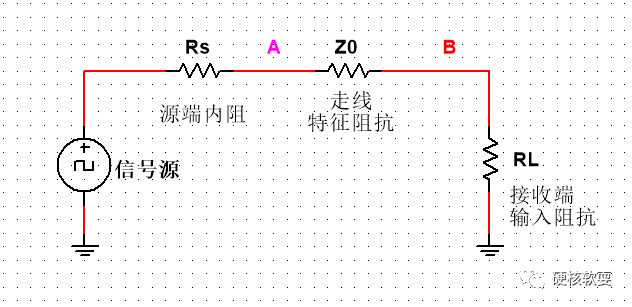

然而实际情况是:源端阻抗不会是50ohm,负载端阻抗也不会是50ohm。常见的驱动端(源端)输出阻抗Rs比较低,一般在几十欧姆以内,而接收端(负载端)输入阻抗RL很高,通常在几百KΩ以上,PCB的特征阻抗Z0一般和源端Rs、终端RL都不相同,实际的信号通路等效模型如下图:

图18

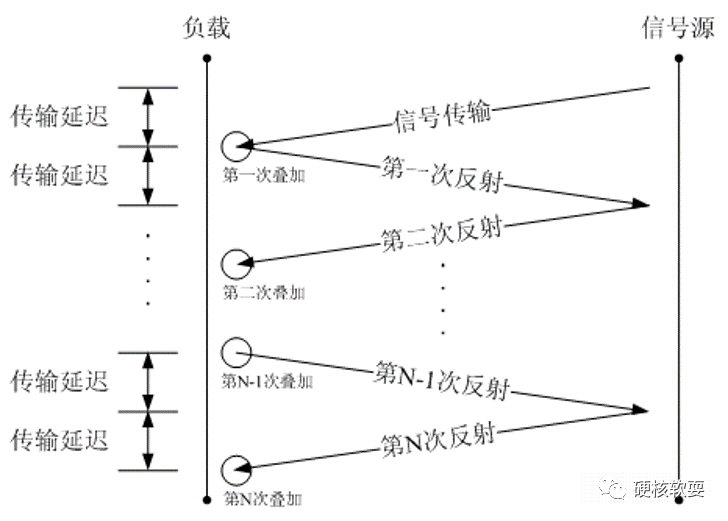

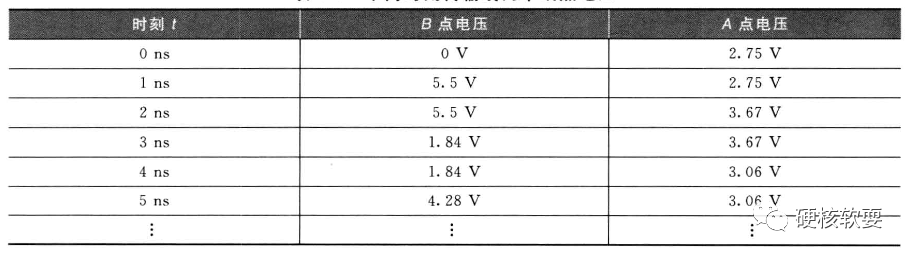

一般情况下,接收端(负载端)输入阻抗RL很高,在分析时可看成开路。图18中,A、B是阻抗不连续点,信号将在这两点多次反射,叠加,最终改变信号的形状。3.1小节所阐述的过冲和下冲是由信号第一次反射导致,3.2小节的振铃则是信号多次反射形成。下图是振铃产生的原因(B点表示负载,A点表示信号源):

图19

4.3 使用反弹图计算反射波形

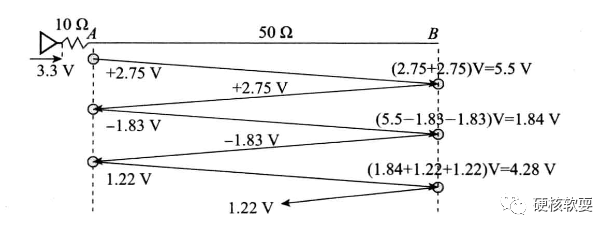

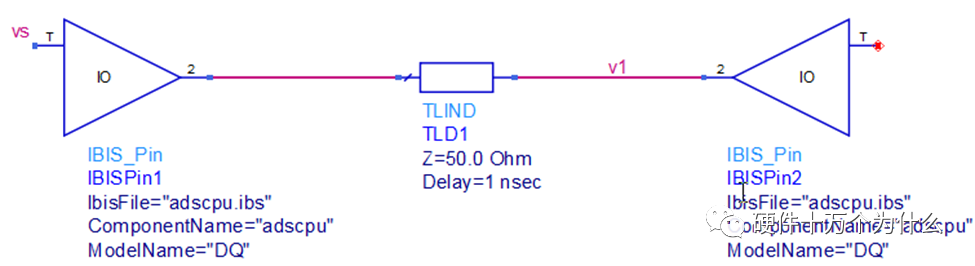

在4.2中,我们知道振铃的产生来源于信号的多次反射,在这小节中,我们通过一个实例来计算反射对波形的影响。这个例子中,我们使用特征阻抗Z0为50Ω的传输线,信号上升时间0ns,即理想方波信号,传输线延时1ns,传输线末端开路(RL=+∞),并且假定驱动器输出阻抗Rs为10Ω,如下图所示:

图20

第1次反射:信号在0ns时从芯片内部发出,经过10Ω输出阻抗和50ΩPCB特征阻抗的分压,实际加到PCB走线上的信号为A点电压[3.3×50/(10+50)]V = 2.75V。1ns后信号传输到源端B点,由于B点开路,阻抗无穷大,反射系数Γ=1,反射信号电压为Γ•2.75V = 2.75V。此时B点测量电压是(2.75+2.75)V = 5.5V。这里需要注意的一点是,在t=1ns这一时刻,B点的测量电压是入射电压与反射电压的叠加。

第2次反射:2.75V的反射电压在t=2ns时刻回到A点,阻抗从50Ω变为10Ω,发生负反射(注意此时从B点反射回来的2.75V信号向A点传播,对于A点来说相当于入射电压),反射系数为Γ = (10-50)/(10+50) = -2/3。所以A点反射电压为2.75V×(-2/3) = -1.83V。此时A点测量电压同样是入射电压和反射电压的叠加,即(2.75+2.75-1.83)V = 3.67V。

第3次反射:-1.83V反射电压向B点传输,t=3ns时刻到达B点,再次发生全反射,反射电压-1.83V。此时B点测量电压为(5.5-1.83-1.83)V = 1.84V。

第4次反射:从B点反射回的-1.83V电压在4ns时到达A点,再次发生负反射,反射电压1.22V。此时A点测量电压为(3.67-1.83+1.22)V = 3.06V。

第5次反射:1.22V反射电压在5ns时刻到达B点再次发生全反射,反射电压1.22V。此时B点测量电压为(1.84+1.22+1.22)V = 4.28V。

第6次反射:……

第7次反射:……

……

图21

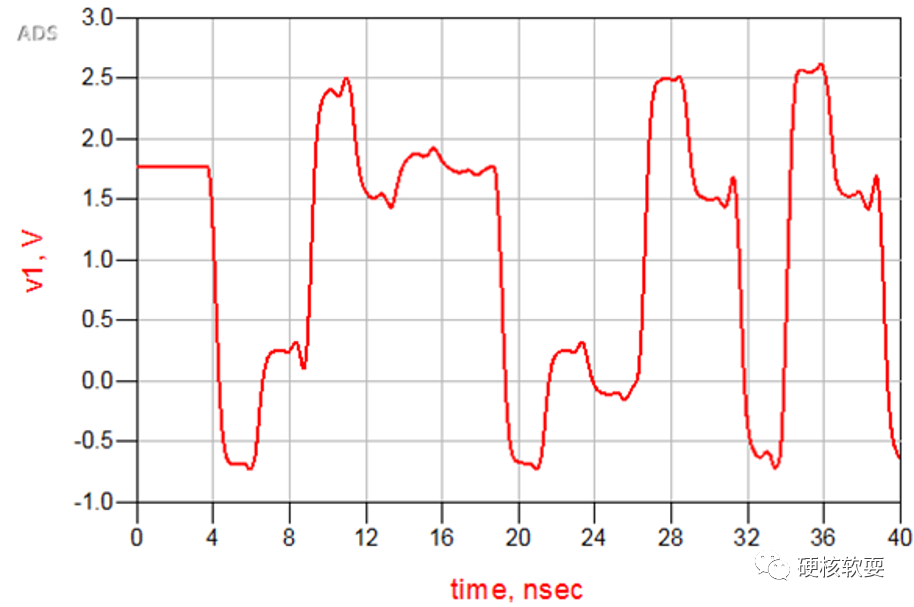

对于任何一个端点,一旦发生反射,该点电压就发生跳变,跳变的电压会一直持续到信号在该点再次发生发射为止。观察A、B点电压,存在上下波动,这就是振铃现象。它们的电平波动可由下图所示:

图22

4.3 解决信号反射的方法

由前文可知,振铃现象的原因是由信号反射引起的,而信号反射的根本原因就是阻抗不匹配,所以要减小乃至消除信号反射,必须进行阻抗匹配。

端接

高速电路常见的阻抗匹配方法是端接,通过采用电阻端接匹配来实现阻抗一致性。常见的端接方式有源端端接、终端并联端接、戴维宁端接、RC端接、差分端接等。那么端接电阻要使用多少?端接电阻怎么放置?阻值选择多大呢?

1)点对点拓扑结构

在介绍端接之前,先来了解电路的拓扑结构。电路的拓扑是指电路中各个元件之间的连接关系。常见的电路拓扑结构包含点对点的拓扑、星型拓扑、T型拓扑、菊花链拓扑等,最简单的拓扑就是点对点拓扑结构的连接设计。点对点设计也是最常见的电路拓扑设计,尤其是在高速电路中几乎都是点对点的连接设计。点对点虽然简单,但是这种拓扑设计限制了带负载的数量。点对点设计,由于驱动端的内部阻抗与传输线的阻抗常常不一样,很容易造成信号反射,使信号失真,造成信号完整性问题。

如图所示是点对点的拓扑结构,由驱动端、传输线和接收端组成。

图23 点对点无端接拓扑结构——图来自硬十

在这个电路拓扑中,其接收端的信号波形如图所示。

图24 点对点无端接拓扑信号波形

从波形上可以看出,信号在高电平时稳定电压在1.8V,最大值却达到2.6V,有800mV;最低值低于0V,达到了-700mV。这么大的过冲很容易损毁芯片,即使不损毁,也存在可靠性的问题。所以,在设计中需要把过冲降低,尽量保证电压幅值在电路可接受的范围内,如此案例尽量保证满足信号幅值在1.8V的±5%内,这时就需要通过端接电阻来改善信号质量。

2)源端端接

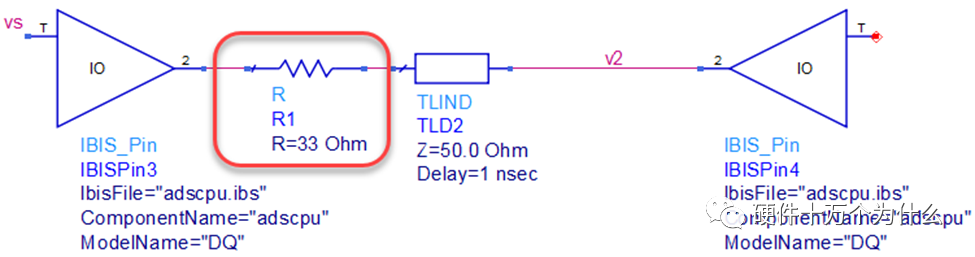

源端端接设计也叫做串联端接设计,是一种常用的端接设计。端接方式是在芯片端出来之后添加一颗端接电阻,这颗电阻尽量靠近芯片输出端,此时芯片内阻和这颗电阻可视为一体。在这种电路结构中,端接多大的电阻是关键。前文我们说过,一般源端输出阻抗比较小,通常在几十欧姆以内,如果线路特征阻抗设计为50Ω,那么源端串联电阻可以设计为33Ω,后面根据实际信号波形再细调端接电阻的阻值。如果需要更精确的端接电阻值,可以根据电路的实际情况进行仿真或计算获得。串联端接的原则是端接电阻尽量靠近源端,源端阻抗Rs与端接电阻R的值相加等于传输线的阻抗Z0。在前面的点对点拓扑结构中,加入电阻值为33Ω的端接电阻,其电路拓扑结构如图所示:

图25 源端端接拓扑结构——图来自硬十

此时接收端的信号波形如图所示:

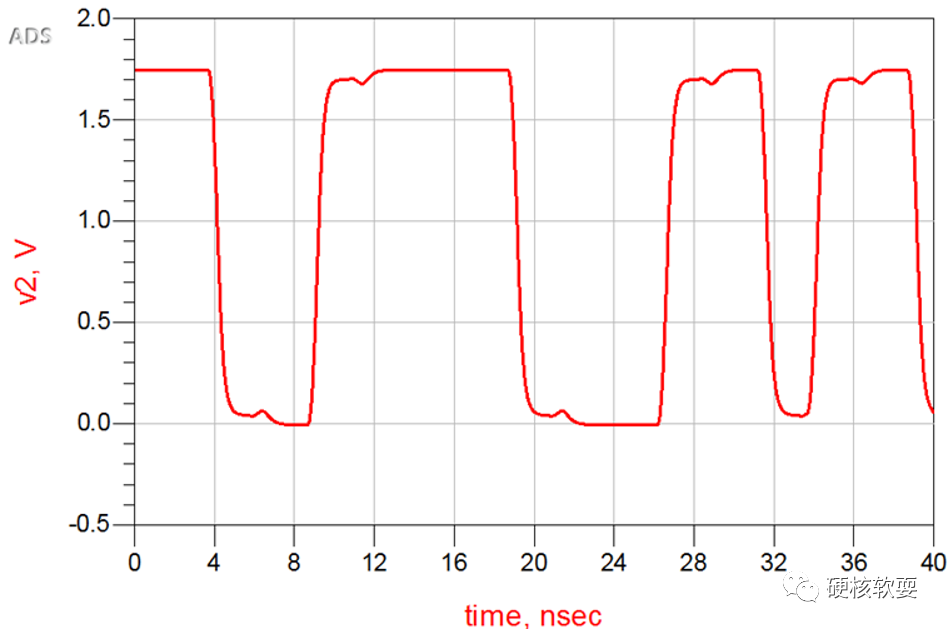

图26 点对点源端端接拓扑信号波形

使用源端端接后,过冲基本消除,信号质量得到极大的改善。另一方面,加入端接电阻后,信号的上升沿变缓,上升沿时间变长。

源端端接在电路匹配时,可以使电路匹配匹配得非常好,但是并不是适合每一种电路设计。源端端接有自身的一些特性,大致归纳如下:

(1)源端端接十分简单,只需要使用一颗电阻即可完成端接。

(2)当驱动器器件的输出阻抗与传输线特征阻抗不匹配时,使用源端端接在开始就可以使阻抗匹配;当电路不受终端阻抗影响时,十分适合使用源端端接;如果接收端存在发射现象(如容性反射),就不适合使用源端端接。

(3)适用于单一负载设计时的端接。

(4)当电路信号频率比较高,或者信号上升时间比较短(特别是高频时钟信号),不适合使用源端端接。因为加入端接电阻后,会使电路的上升时间变长(即RC时间常数变大)。

(5)合适的源端端接可以减少电磁干扰(EMI)辐射(前文说过,阻抗不连续时,会产生反射波,反射的能量有部分变成电磁波散发出去)。

细心的同学会发现,源端端接拓扑的模型,接收端的阻抗依然可以看作无穷大(即信号到达接收端时无处释放),则信号达到接收端时会产生全反射,但由于源端阻抗+端接电阻=传输线阻抗,所以初始时刻在传输线上的电压为信号电压的一半,根据反弹图可知,信号达到接收端并产生全反射之后,在接收端的电压即为信号电压,所以源端端接拓扑实际上是利用了信号的一次反射。

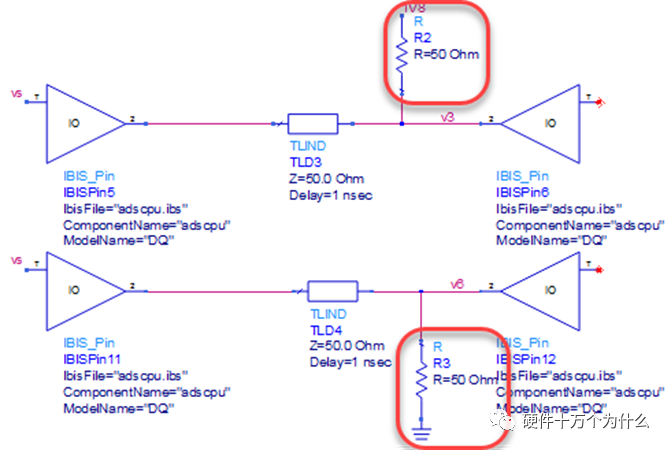

3)并联端接

并联端接即把端接电阻并联在线路中,一般把端接电阻在靠近信号接收端的位置,并联端接分为上拉电阻并联端接和下拉电阻并联端接。并联端接拓扑结构如图所示:

图27 并联端接拓扑结构——图来自硬十

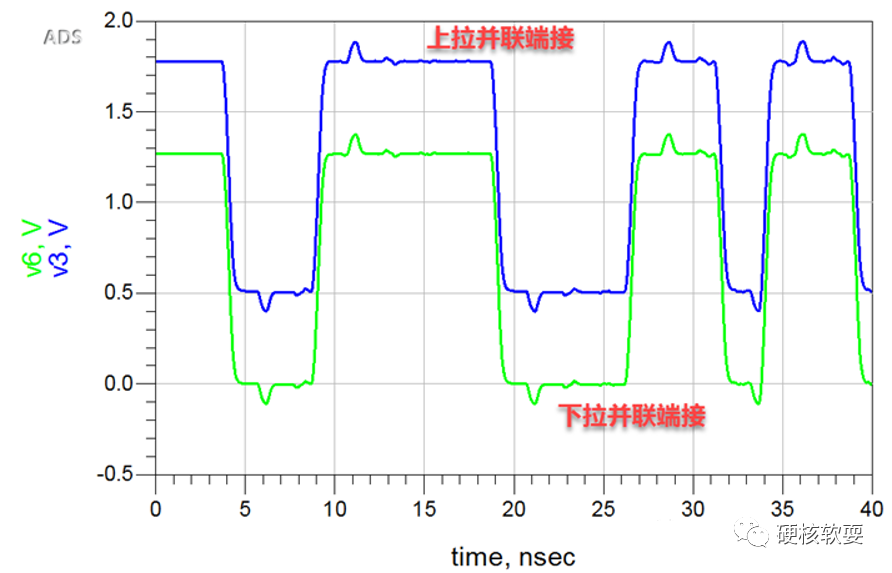

并联端接拓扑结构中,端接电阻值R0与传输线的阻抗一致,接收端的信号波形如图所示:

图28 并联端接拓扑信号波形

从波形上看,过冲基本被消除。上拉并联端接的波形低电平有很明显的上移,下拉并联端接的波形高电平有很明显的下移。无论是上拉并联端接还是下拉并联端接,信号波形的峰峰值都比使用源端端接的峰峰值要小一些。

并联端接放在接收端,能很好地消除反射,使用的元件也只是电阻。

从电路结构可以看出,即使电路处于静态,端接电阻也会消耗电流,所以驱动电流需求比较大,很多时候驱动端无法满足并联端接的设计,特别是在多负载下,驱动端更难满足并联端接需要消耗的电流。所以,一般并联端接不用于TTL和CMOS电路。同时,因为幅值被降低,电路的噪声容限也被降低了。

4)戴维宁端接

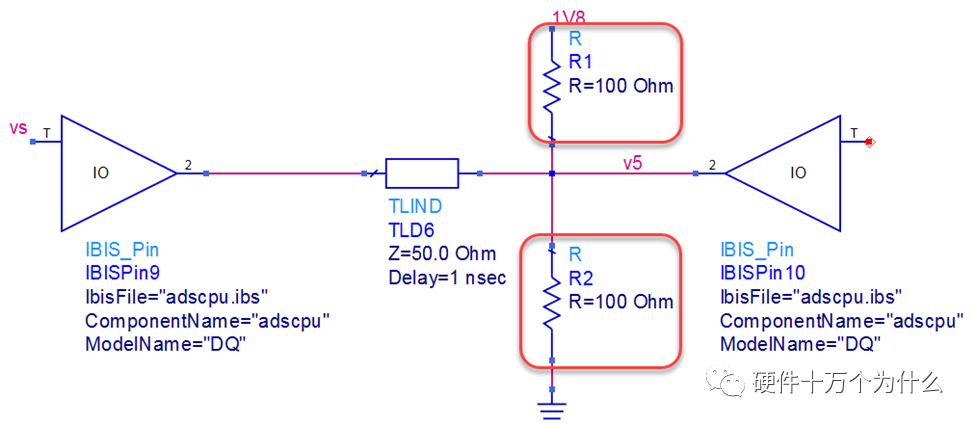

戴维宁端接就是使用两颗电阻组成分压电路,即使用上拉电阻R1和下拉电阻R2构成端接,通过R1和R2吸收反射能量。戴维宁端接的等效电阻(R1||R2)必须等于走线的特征阻抗。戴维宁端接拓扑结构如图所示:

图29 戴维宁端接拓扑结构——图来自硬十

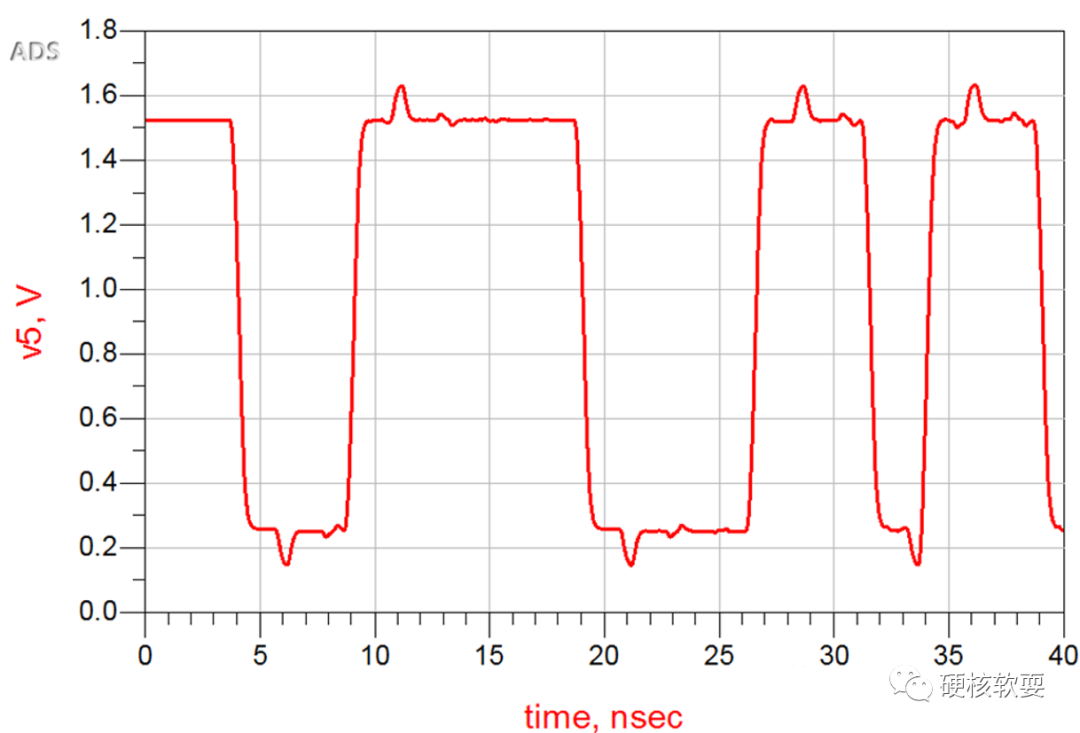

使用戴维宁端接后,接收端的信号波形如图所示:

图30 戴维宁端接拓扑信号波形

从波形上看,戴维宁端接匹配的效果也很好,基本能消除过冲的影响。戴维宁端接可以看成上拉并联端接和下拉并联端接的合体,前者信号波形的低电平等于后两者信号波形低电平的平均值,前者信号波形的高电平等于后两者信号波形高电平的平均值,波形峰峰值相等。因为使用了两颗电阻,所以戴维宁端接比并联端接的直流功耗少,但由于也一直存在直流功耗,所以对电源的功率要求比较多,对源端的驱动能力要求也高。同样地,因为信号波形的幅度降低了,所以噪声容限也被降低。同时,因为使用了两颗分压电阻,电阻的选型也相对更麻烦些,使很多电路设计工程师在使用这类端接时总是非常谨慎。在实际应用中,DDR2和DDR3的数据和数据选通信号网络的ODT端接电路就采用了戴维宁端接。

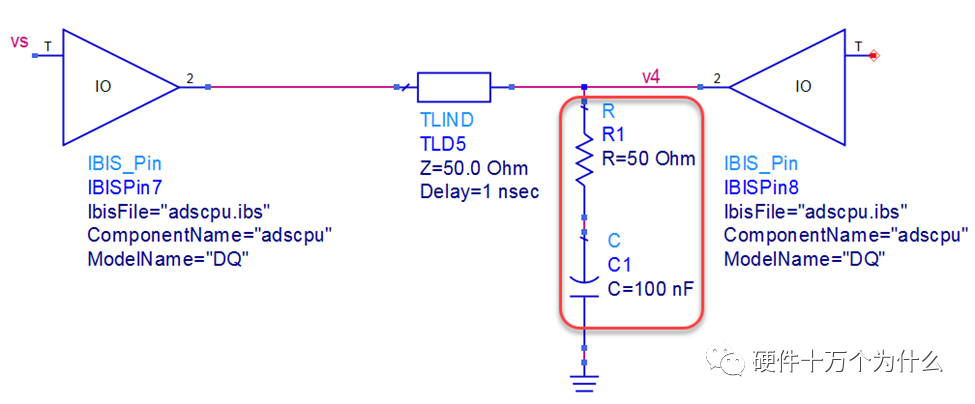

5)RC端接

RC端接在并联下拉端接的电阻下面串联一颗电容到地,即RC端接是由一颗电阻和一颗电容组成的端接。RC端接也可以看作是一种并联端接。电阻值的大小等于传输线的阻抗,电容值通常取值比较小。RC端接拓扑结构如图所示:

图31 戴维宁端接拓扑结构——图来自硬十

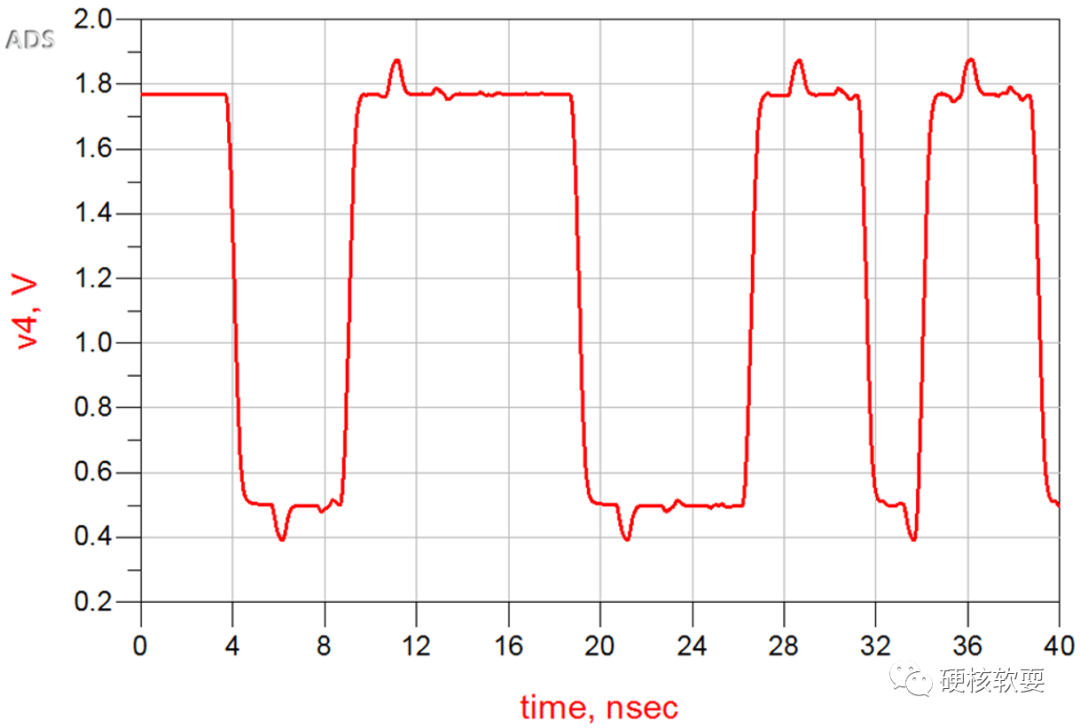

使用RC端接后,接收端的信号波形如图所示:

图32 RC端接拓扑信号波形

从波形上看,RC端接基本能消除过冲的影响。RC端接信号接收端的波形和上拉并联信号接收端的波形相似,在信号为高电平时,C被充电,充满电后可以看作直流电源。RC端接能很好地消除源端带来的反射影响,但是也可能导致新的反射。由于RC端接拓扑中有电容存在,所以电路的静态直流功耗非常小。

同样地,信号波形的低电平提升了很多,所以RC端接后电路的噪声容限被降低。由于引入了RC延时,所以RC端接拓扑中信号波形边沿也明显变缓慢,其变化程度与RC端接的时间常数τ有关(τ=RC)。所以,RC端接并不适合十分高速的信号和时钟电路端接。同时,RC端接需要使用电阻和电容两颗元件。

上面分析的几种端接类型基本都能达到电路匹配的效果,使信号在传输过程中不失真,满足信号完整性的设计要求。从电气性能的角度看,端接匹配不仅可以改善信号质量,还可以用于控制信号边沿变化的速率,即控制信号的上升时间,也可以改变信号电平的类型,起到转换的作用。电子产品设计是一个系统工程,涉及方方面面,其中包括信号完整性和电源完整性,也包括电磁兼容性、电路可靠性、可加工性、成本等,在使用端接来解决反射问题时,也要考虑这些方面的因素。在实际应用中,需要根据项目工程的应用选择端接类型。

四、高低频阻抗匹配共同点

前文说过,阻抗匹配是指信号源或者传输线跟负载之间的一种合适的搭配方式。怎么才算合适则取决于我们的设计目的。而高低频电路中,阻抗匹配的共同点有以下两个点:

(1)功率最大化

在低频电路中,我们通过阻抗匹配来获取最大的输出功率。而在高频电路中,阻抗不匹配会导致反射,反射也会导致损耗。我们总是希望有用的射频信号能够无衰减或者小衰减的传输到负载,如果阻抗不匹配的话,反映到系统的就是该器件的回波损耗差。回波损耗也是损耗。这个反射回去的射频信号,会对系统造成很大的影响,甚至烧坏某些器件。阻抗匹配就是为了电磁波能够更好的传播,同时也是让输出功率最大化。

(2)保证信号质量

在低频电路中,如果输出功率太小,则容易受到外界的干扰,严重影响信号质量,特别是传感器类的微弱信号,如果阻抗不匹配,更容易受到干扰,产生失真。

而在高频电路中,如果阻抗不匹配,就会产生反射,信号出现过冲(Overshoot)、振铃(Ringing)、边沿迟缓(回勾现象),造成严重的信号完整性问题。阻抗匹配则是保证信号质量的有效手段。

五、结语

本篇从阻抗匹配的概念定义开始,阐述了高低频下阻抗匹配的意义、匹配方法以及阻抗匹配对于高低频电路的共同作用,其中夹带着高低频电路的相关知识点,旨在让读者对阻抗匹配有足够的了解以及遇到相关的信号完整性问题时能找到有效的对策。对于阻抗匹配,本文只是抛砖引玉,远远没有结束,特别是在本文没有提及的射频电路中,阻抗匹配还有很多种方式,其中宽带阻抗匹配更有利于整个系统设计,而最为高级的一个阻抗匹配方式是滤波器的设计,限于篇章和知识储备,本文不一一展开,对此有兴趣的读者可自行查阅。

-

阻抗匹配

+关注

关注

14文章

372浏览量

32142 -

高速电路

+关注

关注

8文章

170浏览量

24917 -

振铃

+关注

关注

0文章

28浏览量

18123 -

输入阻抗

+关注

关注

0文章

131浏览量

16386 -

输出阻抗

+关注

关注

1文章

104浏览量

12790

发布评论请先 登录

电子大神传授的经验:阻抗匹配原理及负载阻抗匹配

什么是阻抗匹配原理?什么是负载阻抗匹配?

如何在stm32外部接入阻抗匹配电路?

分立元件组成的阻抗匹配电路

阻抗匹配电路的原理及其应用介绍

阻抗匹配的基本原理和负载阻抗匹配的方法说明

高低频的阻抗匹配电路概念及要点 高速电路的振铃产生原因及解决办法

高低频的阻抗匹配电路概念及要点 高速电路的振铃产生原因及解决办法

评论