点击上方“泰克科技” 关注我们!

点击上方“泰克科技” 关注我们!

随着高速串行 (HSS) 通信通道扩展到多个通道并提升到更快的比特率,确保硬件互操作性变得越来越复杂。模块加载会在背板上产生损伤,这些损伤必须在系统级别使用经过校准的测量系统进行验证。必须特别注意测试设置,才能提高主机背板上插入的不同模块的互操作性。例如,必须注意系统中的模块和背板,无论它们是作为整体相互连接,还是分别独立存在。本应用指南将讨论与背板通道相关的HSS信号注意事项。

讨论:

■背板注意事项

■背板信号有效载荷和信号耦合

■测试点指示

■测试平台校准

■损耗模型和预算

■探头/电缆互连

■嵌入/去嵌入

■抖动和噪声分析

■干扰对象/干扰源分析

背板注意事项

现代背板可以通过进行物理信号测量或模拟通道操作裕量 (COM) 来验证。这里我们将重点讨论通过在系统的多个测试点进行物理信号测量来验证背板的注意事项。这些测量应在信号链的近端和远端进行,通道路径应表示为发射器和接收器端点之间所有通道路径的组合。建议单独测量背板通道,以便验证插入损耗、连续性、反射和串扰。此外,在执行系统级测试时,应在将插卡(PIC) 插入背板之前,根据其规格验证每个插卡的信号质量。

必须验证的因素

•每个背板通道的损耗预算规范(损耗会有所不同)

•通道走线和互连中的不连续性造成的损伤

•相邻走线和层板上的干扰对象/干扰源耦合引起的串扰

•信号的抖动和噪声特性(SDLA将允许在每个特定 S参数的测试点进行测量,而无需移动探头点)

•通过加压信号模式进行抖动和眼图测试

•具备适当背板隔离的校准测量系统

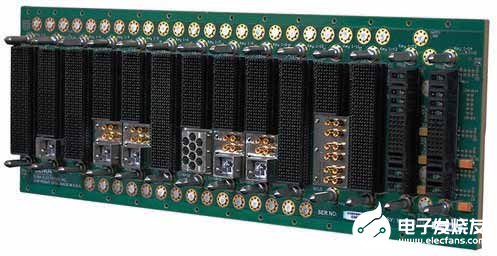

模块和背板注意事项

•在插入PIC之前表征背板

• 使用校准夹具和适当的适配器互连来测量损耗预算,以分路信号

• 使用分线板(也称为“Paddle Card”)在指定测试点测量从PIC穿过背板的信号传输

背板信号有效载荷映射和信号耦合

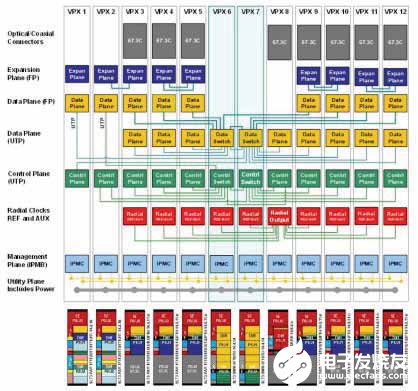

通常,背板应在同一系统中支持商用现货(COTS)和专有PIC。然而,在分布式背板架构中,HSS信号会受到信号损伤,例如通道损耗、信号耦合不完美和模块负载回波损耗。此外,每个模块都将具有高功率和低功率操作要求的电信号。在同一背板上支持如射频 (RF)和光学标准等混合模式通道和组合带来了更多的挑战。

背板配置在尺寸和功能上存在显著差异。通常情况下,我们必须对混合信号进行管理,以便在背板上正常运作。HSS信号容易受到串扰、EMI和其他形式的耦合影响。正确的模块布局是确保互操作性的关键考虑因素,可通过维持适当的通道损耗预算来实现。

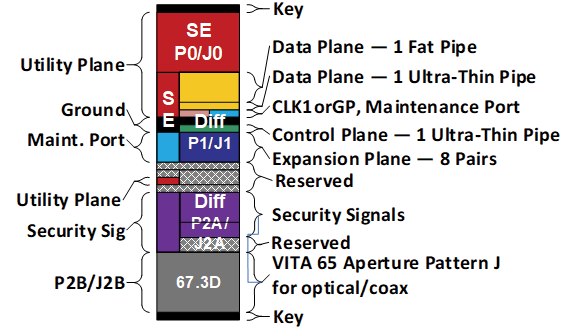

混合信号背板架构的结构化信号组映射和布局,显示背板总线、离散信号和电源/接地层。

连接器布局定义了特定背板连接器支持的PIC类型。为了确保适当的互操作性,背板和PIC的组合通道损耗不得超过通道的总损耗预算。因此,对于具有HSS总线的PIC,必须额外考虑背板插槽的布局。

了解更多

扫描二维码,立即下载完整版应用指南!

测试点指示

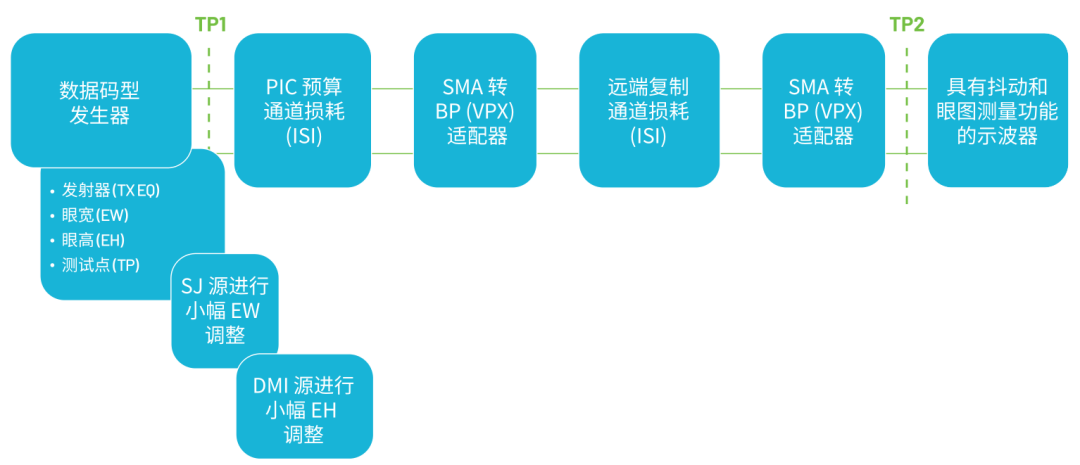

为了确保HSS信号的测量结果准确,必须使用经过校准的测量系统测量指定测试点的信号。测量系统应包括适当的互连适配器、ISI损耗夹具和复制通道。

•TP1直接连接到示波器以进行校准测量

•码型发生器将传输如一致性、PRBS或自定义等测试码型,其振幅上具有不同压力,需要对其进行校准以实现正确的压力损伤 , 从而满足测试规范中的传输均衡要求

•随机和正弦(调整眼宽)抖动损伤

•合路器用于注入差模(调整眼高)和共模干扰

•TP2信号在背板通道远端进行示波器测量,可实现全通道压力测量

•TP2信号注入到近端的背板

•进行校准通道损耗补偿

•进行复制通道损耗补偿

校准结果

•补偿信号路径中的实际损耗

•补偿HSS测试模式中的RJ和SJ损伤

•使用传输通道均衡来补偿压力信号EH和EW

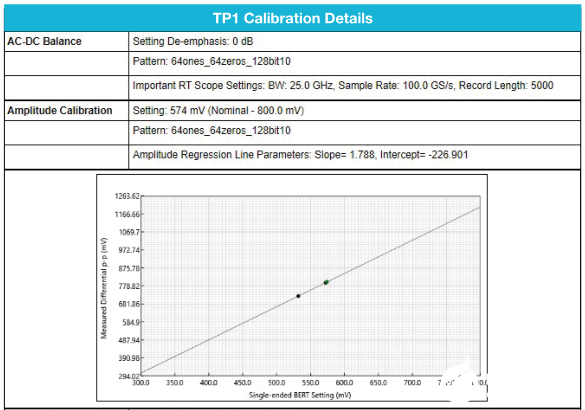

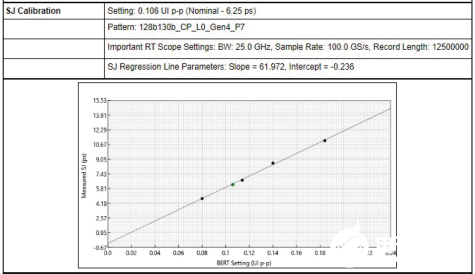

测试平台校准TP1(示例图)

TP1校准旨在补偿从信号源到ISI损耗夹具以及Rj和Sj正弦抖动曲线中的信号幅度损失。这些校准将用于补偿码型发生器输出电平,以抵消信号到达TP1注入点的损耗。

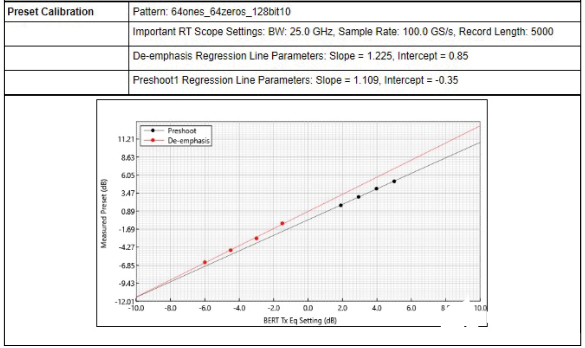

幅度校准旨在补偿由于通道损耗变化和数据模式变化导致的发生器输出电压变化。一致性测试码型 (Compliance Pattern) 提高了测试结果的一致性。TX均衡Presets经过校准,可为预期的通道衰减准备信号。

TX均衡Presets经过校准,可为预期的通道衰减准备信号。

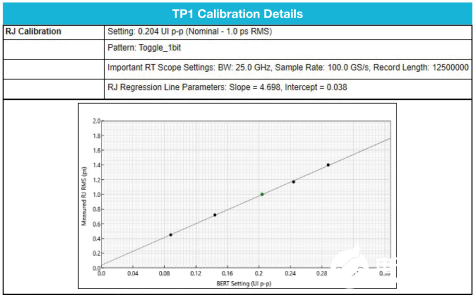

测试平台校准TP1(示例图)

真实地注入随机抖动(RJ)到数据码型中,用于了解系统对随机(无界)抖动的敏感性。

正弦抖动(SJ), 有时甚至考虑相邻通道的串扰引入的抖动,也会被真实的注入到数据码型中,用于了解系统对有界抖动的敏感性。

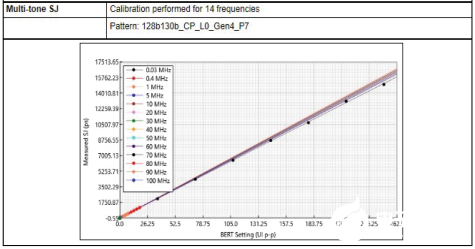

多音SJ用于测试接收器在指定频率下的时钟恢复抖动跟踪(例如PLL环路带宽)。

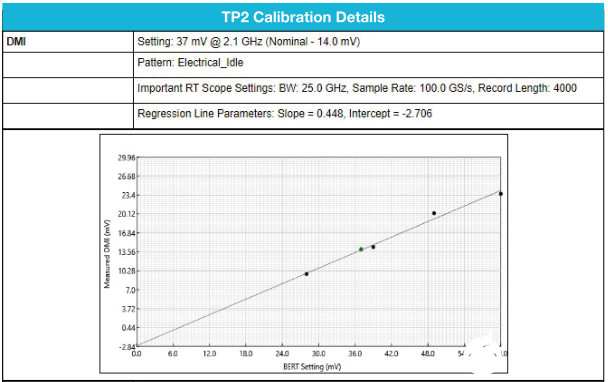

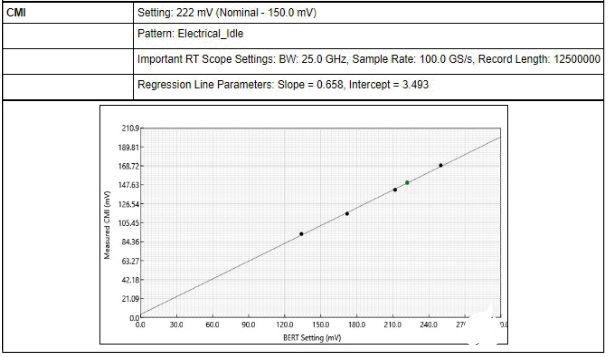

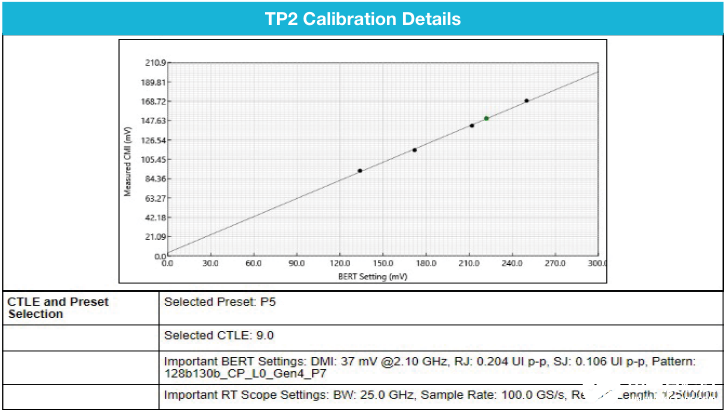

测试平台校准TP2(示例图)

TP2校准提供了一种包括差模干扰(DMI)和共模干扰 (CMI)等效项的方法,这些是用于模拟系统串扰的必要条件。

DMI是在已知损耗的通道上测量的,该通道代表物理通道。ISI/DMI/SJ共同用于以确定性方式设置EH和EW。

CMI是在已知IL损耗的通道上测量的,该通道代表物理通道。

测试平台校准TP2(示例图)

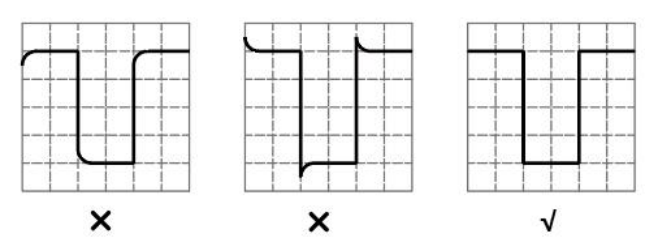

信号加重/去加重允许对TP1和TP2处的信号进行所需的TX均衡(通道中的校准响应),用于为HSS信号测试指定的适当测试模式打开信号眼图。

|结论|

(注:受篇幅限制,请大家扫描文中二维码下载完整版应用指南学习~)

从模块到背板的HSS信号将在通道信号路径上受到损伤。校准的测试方法可实现适当的补偿,从而实现互操作性。

■使用校准的测试夹具,并观察通道中的通道损耗预算以便进行信号补偿。

■采用信号通道的嵌入和去嵌入技术,无需移动探头即可在所有测试点进行精确测量。

■模块和背板都可能出现串扰,因此最好分别表征串扰然后将它们作为整体系统来表征。

点击阅读原文,

了解更多高速接口测试方案!

欲知更多产品和应用详情,您还可以通过如下方式联系我们:

邮箱:china.mktg@tektronix.com

网址:tek.com.cn

电话:400-820-5835(周一至周五900)

将您的灵感变为现实

我们提供专业的测量洞见信息,旨在帮助您提高绩效以及将各种可能性转化为现实。

泰克设计和制造能够帮助您测试和测量各种解决方案,从而突破复杂性的层层壁垒,加快您的全局创新步伐。我们携手共进,一定能够帮助各级工程师更方便、更快速、更准确地创造和实现技术进步。

扫码添加“泰克工程师小助手”

立享1对1专属服务!

点击“阅读原文”了解更多!

原文标题:应用指南 | 信号完整性背板测试

文章出处:【微信公众号:泰克科技】欢迎添加关注!文章转载请注明出处。

-

泰克科技

+关注

关注

2文章

228浏览量

20690

原文标题:应用指南 | 信号完整性背板测试

文章出处:【微信号:泰克科技,微信公众号:泰克科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

PKDV5161差分探头在数字信号完整性测试中的应用

IDT信号完整性产品:解决高速信号传输难题

PK6350无源探头在高速数字总线信号完整性测试中的应用案例

普源示波器DS1102如何精准应对5G信号完整性测试

揭秘高频PCB设计:体积表面电阻率测试仪如何确保信号完整性

普源DHO924示波器在信号完整性测试中的表现

了解信号完整性的基本原理

应用指南 | 信号完整性背板测试

应用指南 | 信号完整性背板测试

评论