设计任务

在EGO1开发板上实现2选1多路选择器。

设计分析

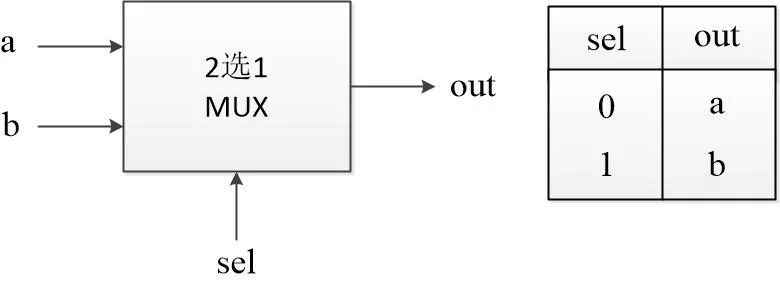

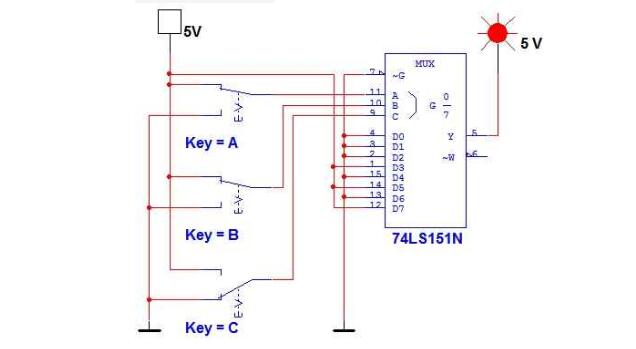

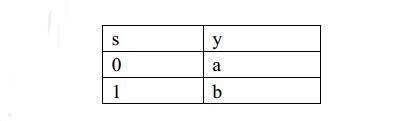

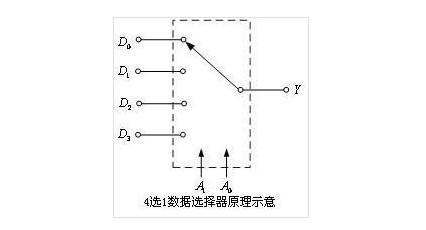

(1)设计电路逻辑关系如下图,明确输入、输出信号。

▲ 2选1多路选择器

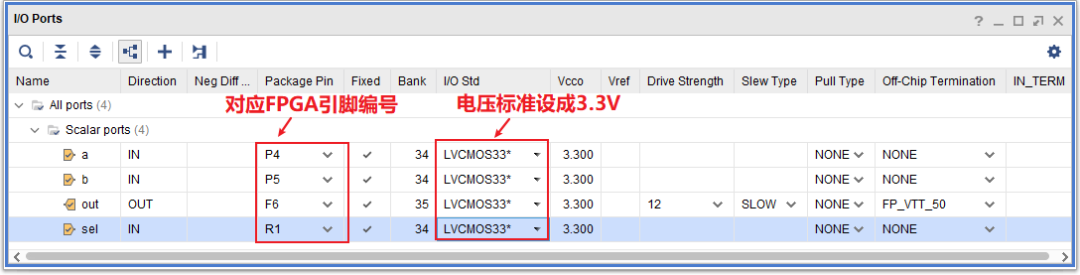

(2)确定信号与FPGA引脚关系。(将在第6步添加设计约束中用到)

根据丝印标识可知如下对应关系。(可参考硬件原理图或EGO1用户手册)

a→P4 //SW6

b→P5 //SW7

sel→R1 //SW0

out→F6 //LD2-7

设计流程

1. 创建FPGA设计工程

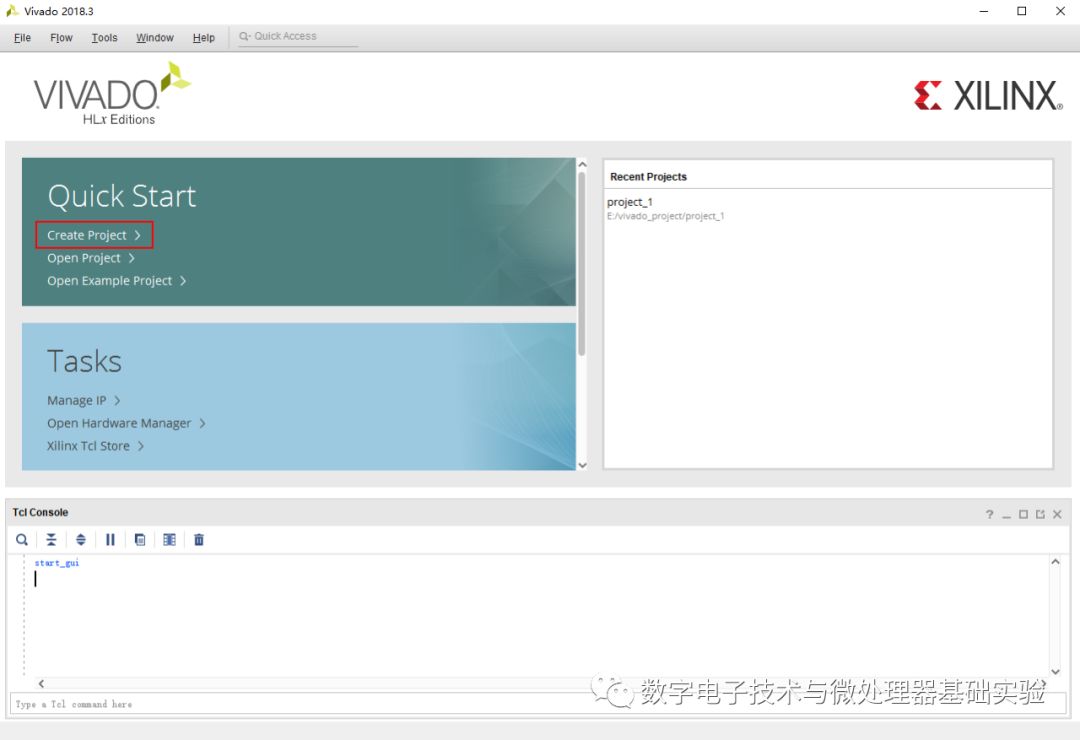

(1)双击桌面图标启动vivado。

(2)创建一个FPGA工程。

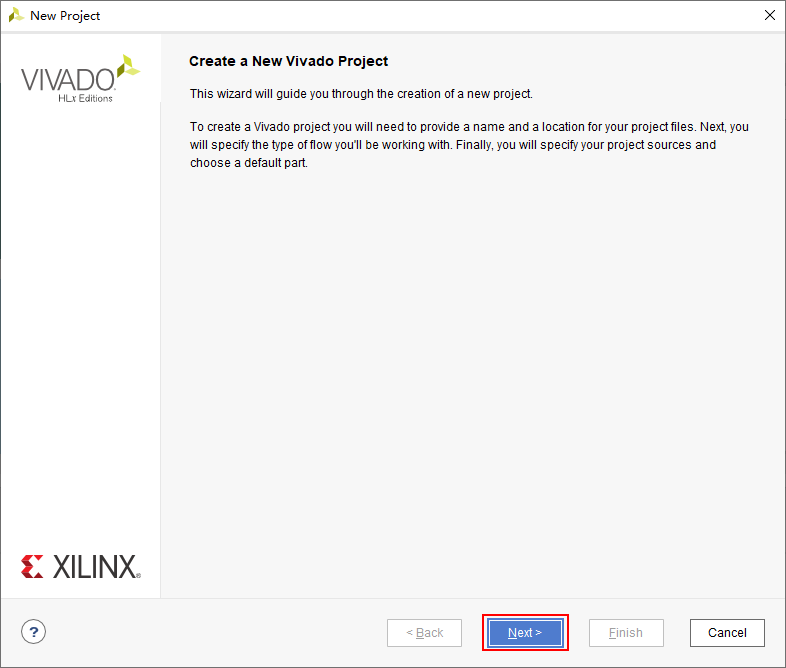

(3)进入新建工程向导。

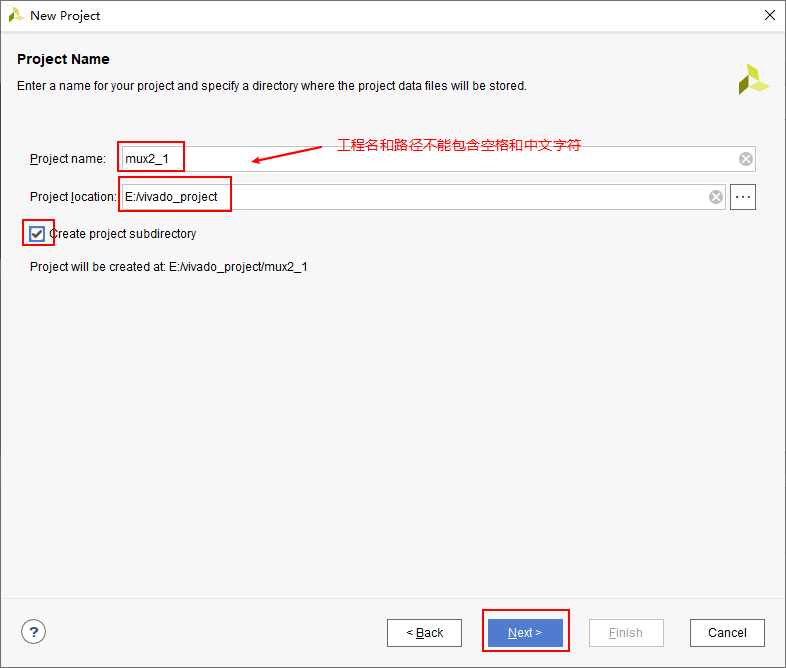

(4)填写工程名称和路径,选择“Create project subdirectory”。

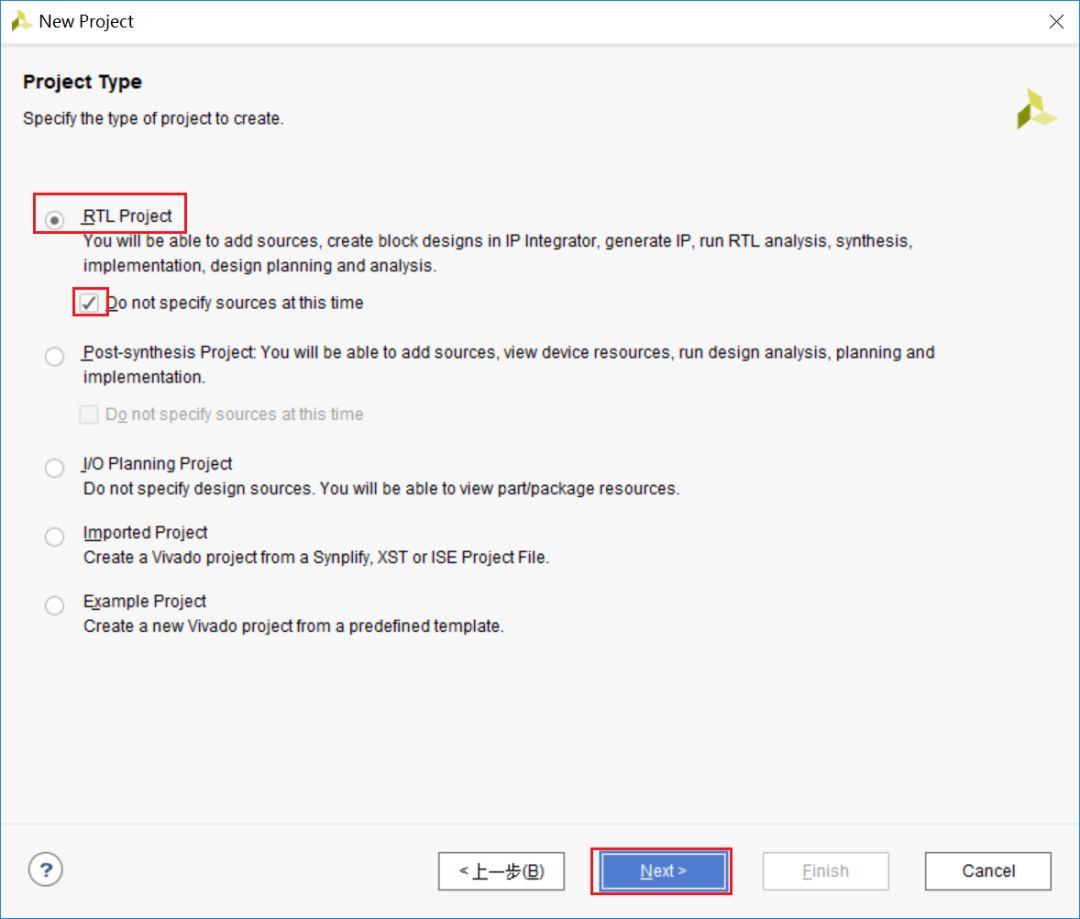

(5)选择创建“RTL Project”。勾选复选框“Do not specify sources at this time”(不在当前阶段创建源程序)。

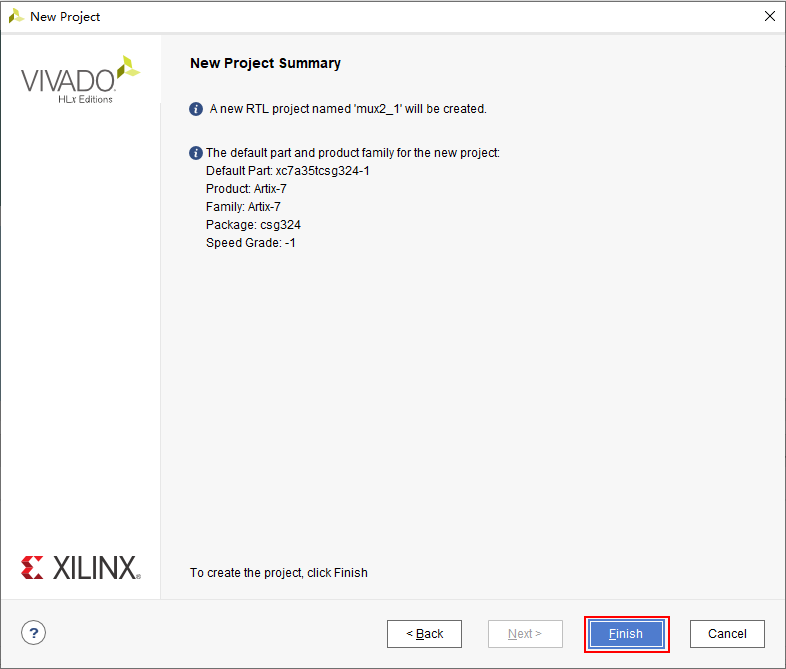

(6)选择设计所用的具体FPGA型号,可以根据器件系列,封装,速度等级以及温度级别进行筛选,也可以直接填入器件型号进行搜索。EGO1开发板所用芯片为Xilinx公司的 xc7a35tcsg324-1 ,属于Artix-7系列,封装为csg324,速度等级为-1。

(7)工程信息概览,单击“Finish”,完成工程创建。

2. 添加源文件

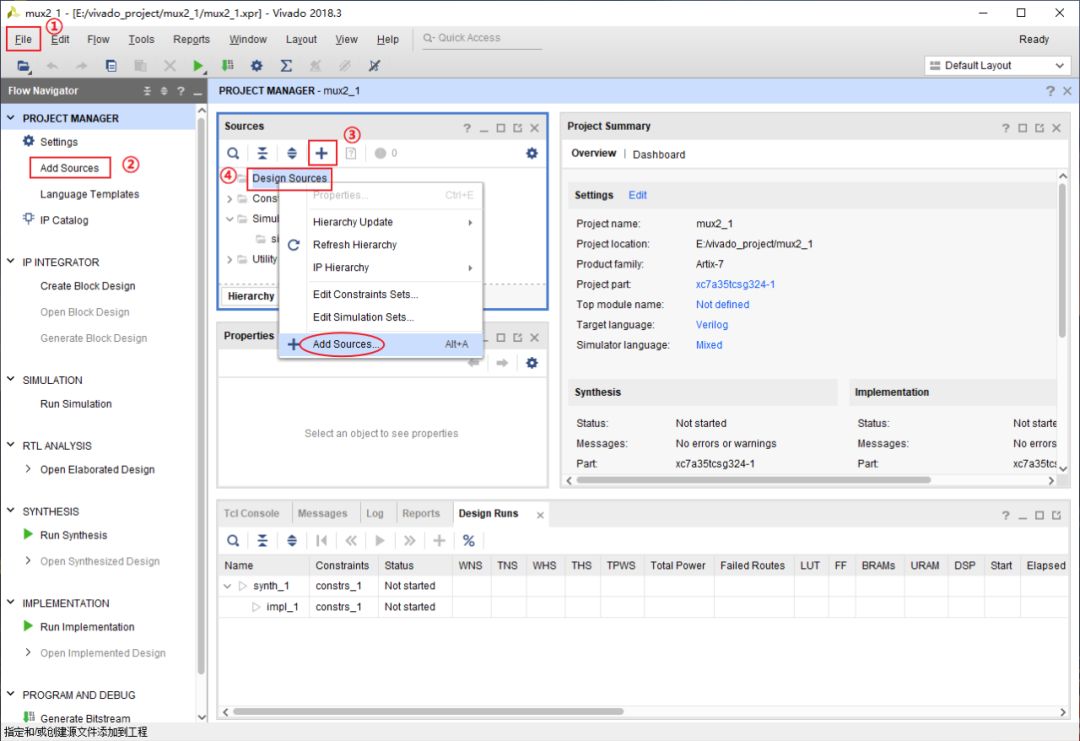

(1)有四种方式可以打开源程序添加窗口。

可以创建约束文件,设计源文件和仿真文件。这里选择创建设计源文件Add or create design sources。

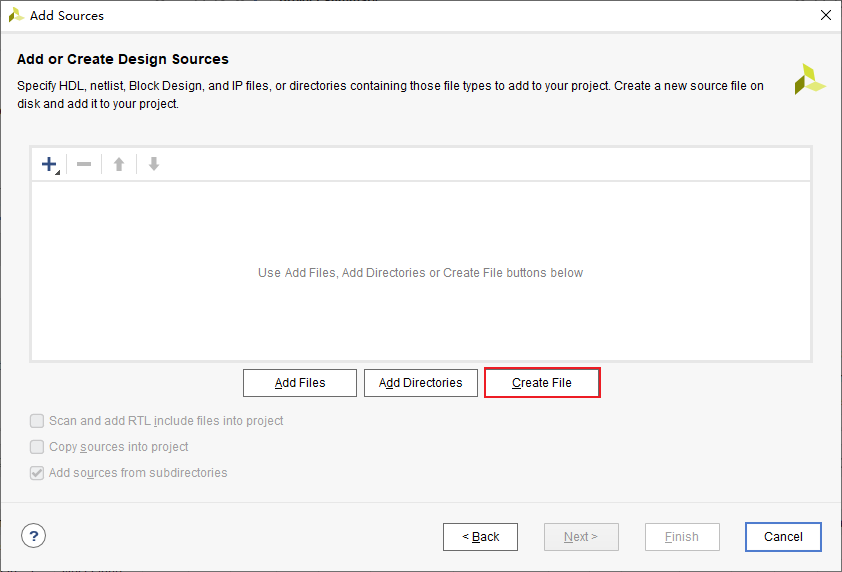

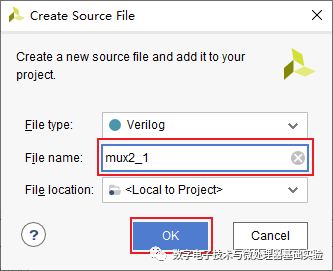

(2)选择“Create File”,弹出对话框中输入文件名“mux2_1”。

(3)模块端口定义,可以添加模块的端口信号。也可以选择不添加,待后续直接在源程序界面输入程序。

设计主界面中sources窗口下出现了如下图所示的mux2_1.v源程序文件,双击打开文件,添加代码。

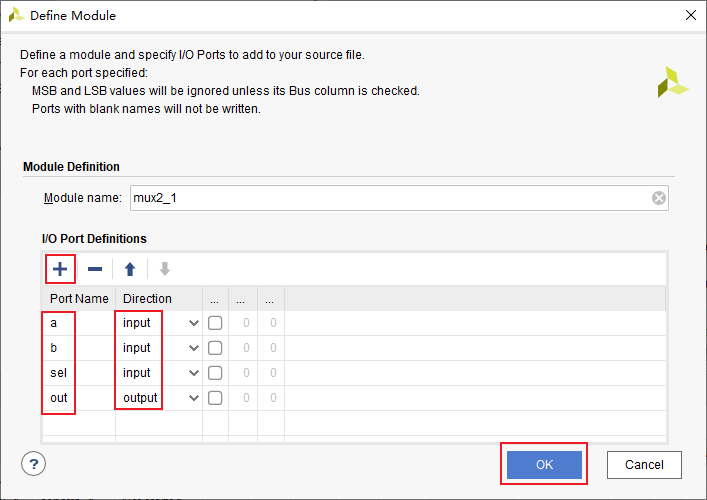

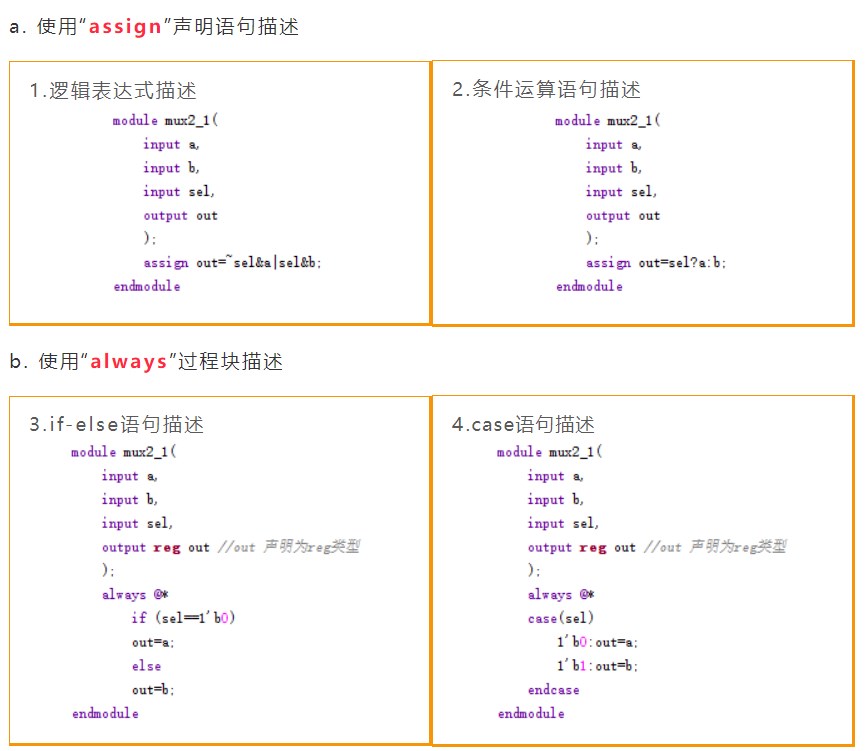

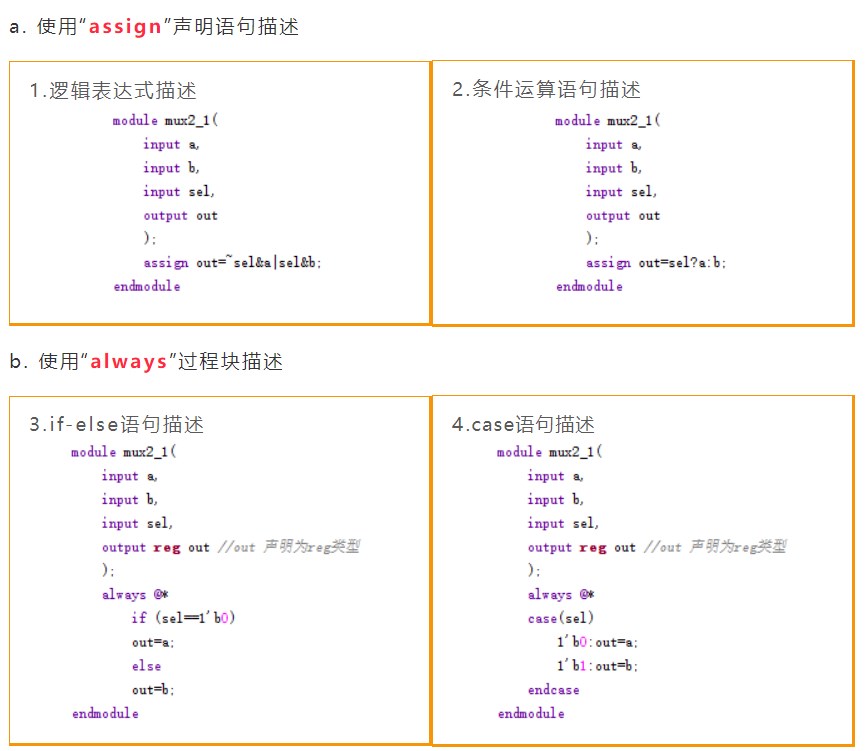

(4)添加Verilog HDL描述。对同一个电路可以有多种描述方式,以下给大家提供了2类主要功能定义的方法,4种不同的语句描述。请选择1种添加到源程序中。

(5)编辑完成后,保存源文件。

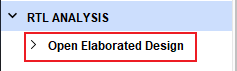

3. RTL分析

用Verilog语言描述电路的时候,可能出现语法或逻辑上的错误。一般语法错误在编写程序的过程中,vivado会自动检测并在程序界面中有所提示,在Messages中也会提示“Error”。对于逻辑错误软件是不会提示的,最多在Messages中的“Warning”提示中找到一些蛛丝马迹。而设计者可以利用RTL分析进行逻辑和功能检查。

(1)点击左侧流程向导栏(Flow Navigator)中的“Open Elaborated Design”,弹出提示框,点“OK”。

(2)RTL原理图查看。下图即打开的RTL原理图。该原理图是根据HDL描述生成的,可以根据原理图检查设计是否符合要求。

4.行为仿真

检验设计是否满足功能要求。如果直接在FPGA芯片上测试,可能因为多次综合、实现而浪费时间。

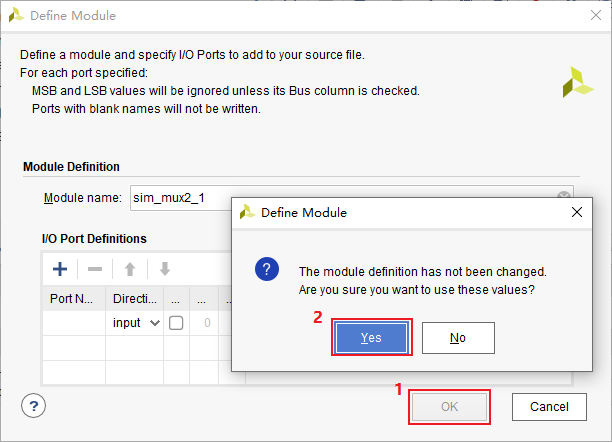

(1)创建仿真文件sim_mux2_1.v。添加方法与添加源程序方法相同,但选择的是Add or Create Simulation Sources选项。

(2)按下图操作,直接点击“OK”→“Yes”,不添加端口定义。

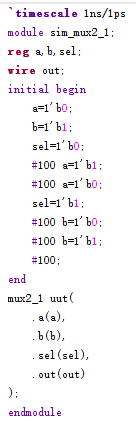

(3)sources窗口中双击打开仿真文件sim_mux2_1.v,输入代码。这里提供两种测试代码供大家参考比较。

参考代码a:

参考代码b:

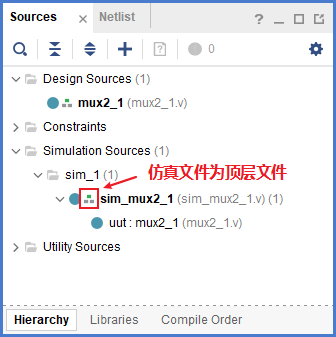

(4)保存。保存文件后,sim_mux2_1.v自动变成顶层文件(品字形图标标识),否则,右键选择“Set as Top”。mux2_1.v为下层模块,模块名为uut。

(5)运行仿真。单击左侧Flow Navigator中Run Simulation,选择Run Behavioral Simulation。

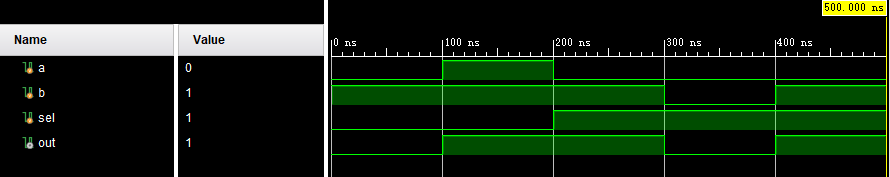

(6)观察仿真波形。

代码a仿真结果:

代码b仿真结果:

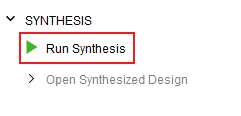

5.设计综合

综合: 将较高层次逻辑设计代码或原理图等设计输入转化为较低层次的由FPGA芯片中底层基本单元表示的电路网表。

(1)单击左侧Flow Navigator中的Run Synthesis。

综合运行时,在软件右上角会显示当前状态,如下图所示。

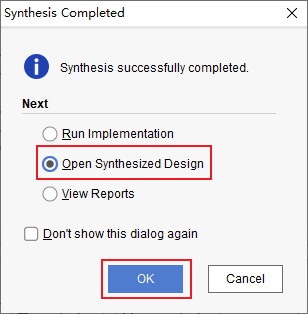

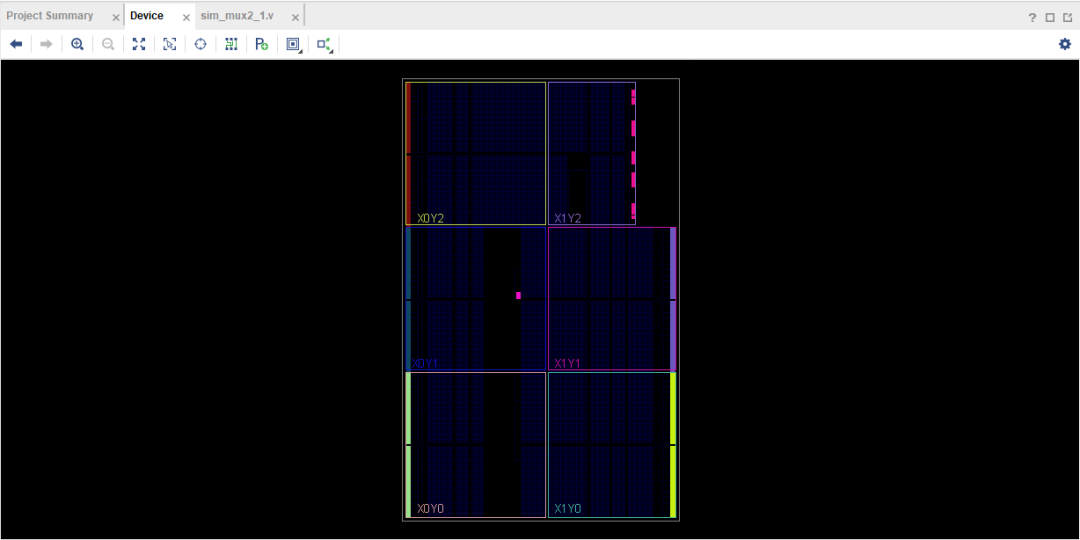

(2)运行完毕,弹出对话框,选择Open Synthesized Design,会自动打开Device窗口,显示的是芯片内部构架。

▲ Artix-7 FPGA器件的内部结构图

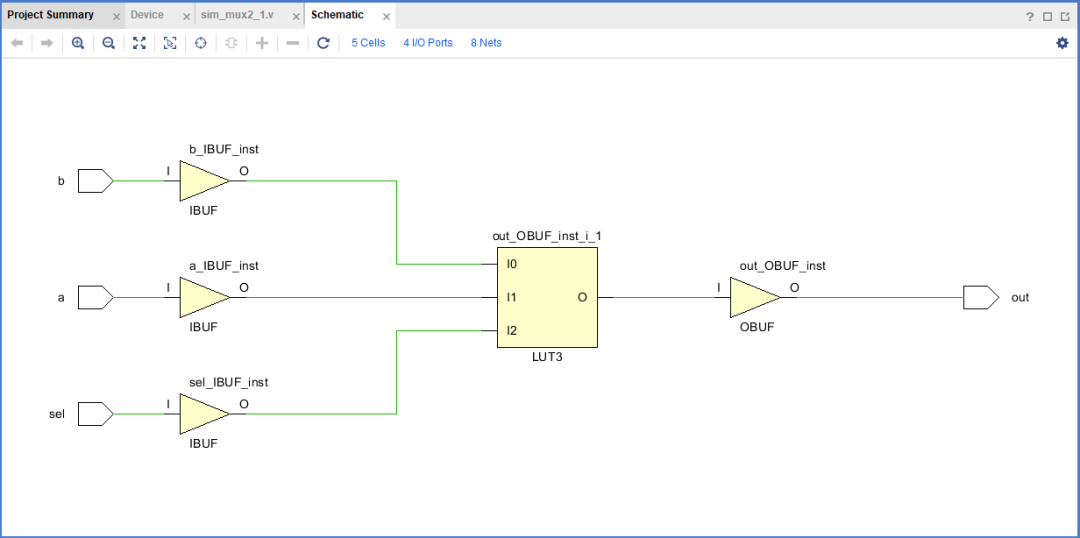

(3)打开Schematic,可以看到综合后的原理图,采用的是FPGA中基本单元搭建的,如本实验使用了一个LUT3查找表。

(4)在Sources窗口下方Cell Properties窗口中,选择Truth Table,可以看到逻辑表达式和真值表。

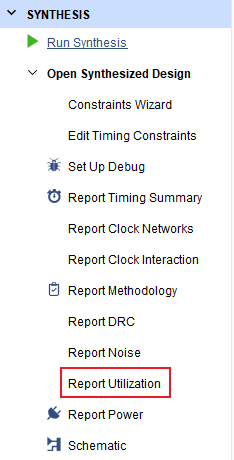

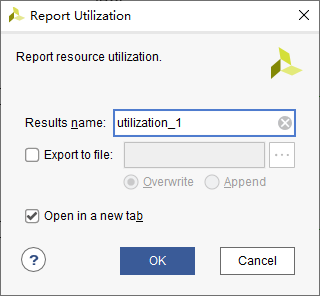

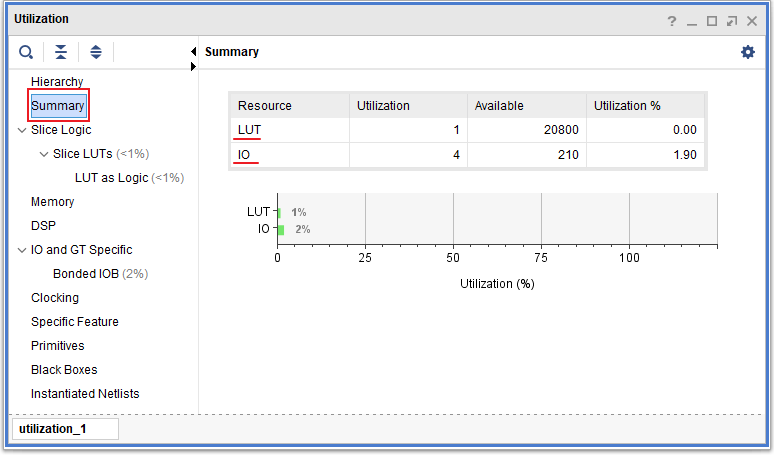

(5)单击Report Utilization,可以查看当前设计的资源利用率的详细报告。

可以看到本设计使用了 1个LUT ,总共20800个,利用率小于0.01%; 4个I/O ,总共120个,利用率为1.90%。

6.添加设计约束

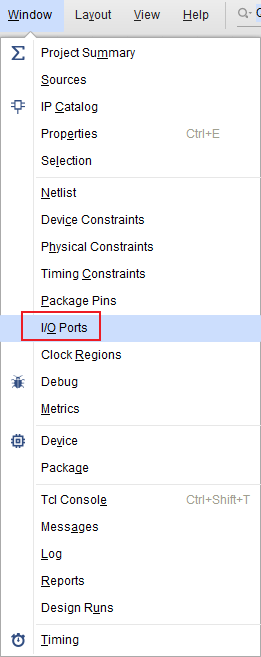

(1)在Window下拉菜单中选择I/O Ports。

(2)按照下图修改电压标准,添加端口对应的FPGA引脚编号。

(3)保存。Sources视图中可以看到Constraints目录下生成的mux2_1.xdc文件。打开可以看到自动生成的约束代码,如下图所示:

(4)在Window下拉菜单中选择Package,可以打开I/O规划视图,如下图所示。可以看到设计所占用的FPGA引脚分布(图中用红色圆圈标识)。

添加约束的快捷方式:新建空白约束文件,打开EGO1官方提供的约束文件“EGo1.xdc”,选择相应的约束语句,直接拷贝,并修改端口名称即可。

7.设计实现

实现: 将综合后的电路网表针对具体指定器件以及相关物理与性能约束进行优化、布局、布线并生成最终可以下载到FPGA芯片内的配置文件的过程。

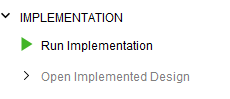

(1)单击左侧Flow Navigator中的Run Implementation。

(2)实现过程结束后弹出对话框,可以选择Open Implemented Design,也可以选择Generate Bitstream(生成配置FPGA的比特流文件)。这里选择Open Implemented Design。

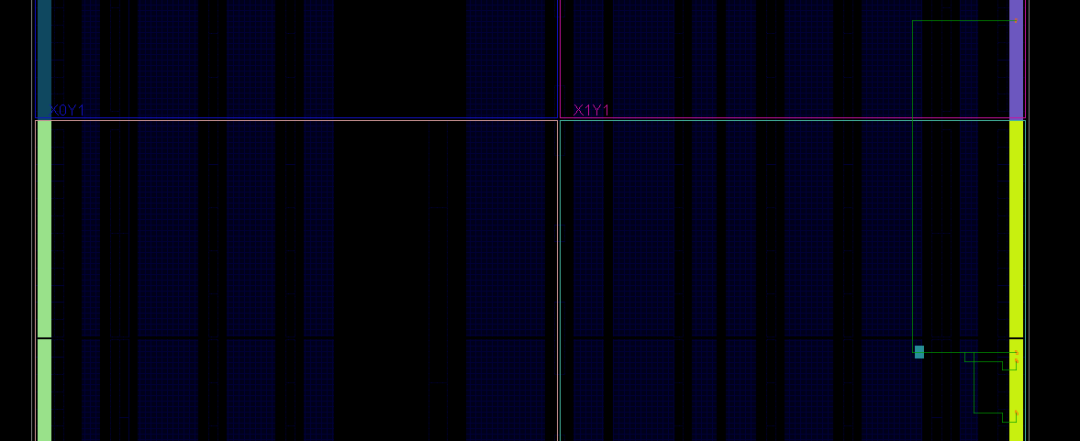

可以看到在器件结构图中设计所用到的器件,如图中红色圆圈标识部分,可以放大查看。

点击工具栏中布线图标,放大视图,可以看到器件之间的连线(图中绿色部分)。

8.时序仿真

时序仿真: 之前的行为仿真是功能仿真,并未涉及毛刺、竞争冒险等时序问题。实现执行后器件完成了布局布线,在此阶段后的仿真可得到各种时序所导致的延时问题。

(1)单击Run Simulation,在浮动菜单中单击Run Post-Implementation Timing Simulation。

(2)仿真波形如下,调整波形,可以观察信号延时。下图中,输入信号a在100ns处由0变为1,而输出信号out在108.590ns处才发生变化,时延约8.6ns。

9.比特流文件的生成与下载

(1)实现结束后直接选择Generate Bitstream,或单击左侧Flow Navigator中Generate Bitstream。

(2)将开发板与电脑连接,并确保电源开关打开。点击Open target,单击Auto Connect。

(3)点击Program device,在出现的对话框中直接点击Program,比特流文件就配置到器件中了。

10.实验现象观察

将SW0置0,拨动SW6,则最左侧LED灯随SW6的状态变化;将SW0置1,则LED灯随SW7的状态变化。

-

RTL

+关注

关注

1文章

393浏览量

62382 -

FPGA芯片

+关注

关注

3文章

250浏览量

40851 -

时序仿真

+关注

关注

0文章

14浏览量

7572 -

HDL语言

+关注

关注

0文章

48浏览量

9312 -

多路选择器

+关注

关注

1文章

22浏览量

6838

发布评论请先 登录

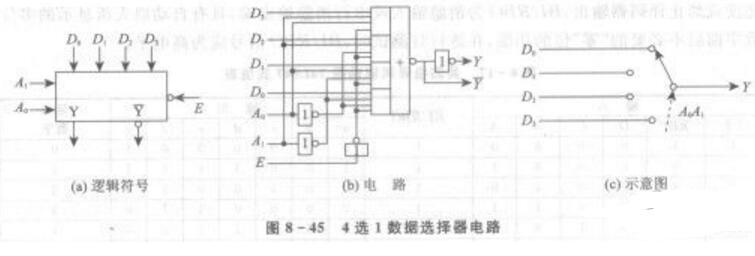

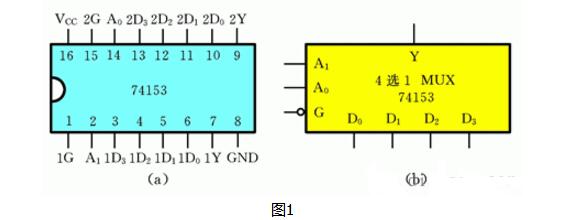

EDA四选一多路选择器的设计

8选1多路选择器电路图(五款8选1多路选择器电路)

Verilog HDL之多路选择器设计

使用Verilog语言实现持续赋值方式定义2选1多路选择器的程序

使用Verilog语言实现持续赋值方式定义2选1多路选择器的程序

Verilog数字系统设计——简单组合逻辑2(4选1多路选择器)

教你学Vivado—以2选1多路选择器为例

教你学Vivado—以2选1多路选择器为例

评论