本文介绍一个FPGA开源项目:UDP RGMII千兆以太网通信。该项目在我之前的工作中主要是用于FPGA和电脑端之间进行图像数据传输。本文简要介绍一下该项目的千兆以太网通信方案、以太网IP核的使用以及Vivado工程源代码结构。

Vivado 的 Tri Mode Ethernet MAC IP核需要付费才能使用,因此本文提供完整工程源码。

01软硬件平台

- 软件平台:Vivado 2017.4;

- 硬件平台:XC7K410TFFG900-2;

02RGMII接口

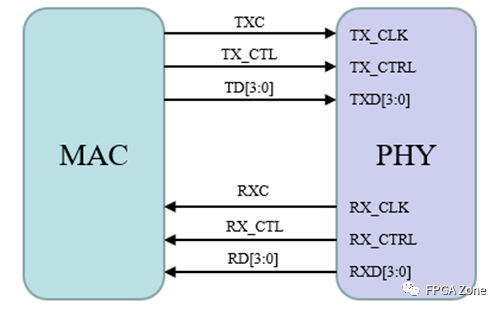

本设计采用 RGMII 接口的 88E1512 芯片。RGMII 接口的主要优势在于,它可以同时适用于1000M、100M、10M三种速率,并且接口占用引脚数较少。

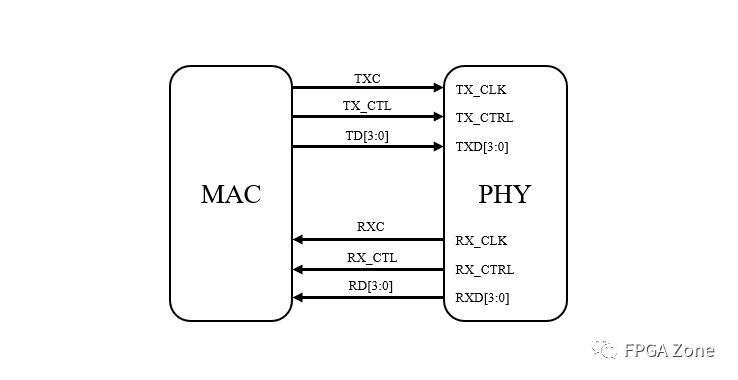

RGMII 使用 4bit 数据接口采用上下沿 DDR(Double Data Rate)的方式在一个时钟周期内传输 8bit 数据信号,即上升沿发送或者接收数据的低4位[3:0],下降沿发送或者接收数据的高4位[7:4]。同理,使用 1bit 控制接口采用 DDR 的方式在一个时钟周期内传输 2bit 控制信号。

- 发送端:tx_clk,tx_d[3:0],tx_ctrl;

- 接收端:rx_clk,rx_d[3:0],rx_ctrl;

- 三种速率模式

RGMII 接口适用于1000M、100M、10M三种传输速率。

当工作于1000M时,时钟信号TXC和RXC均为 125MHz,4bit数据信号上下沿值均有效,控制信号上下沿值也均有效。

当工作于100M时,时钟信号TXC和RXC均为25MHz,4bit数据信号只有上升沿值[3:0]有效,相当于此时数据信号切换为单沿SDR(Single Data Rata)4位输模式。控制信号仍为上下沿有效。

当工作于10M时,时钟信号TXC和RXC均为2.5MHz,数据信号和控制信号的使用和100M速率时完全相同。

03UDP通信方案

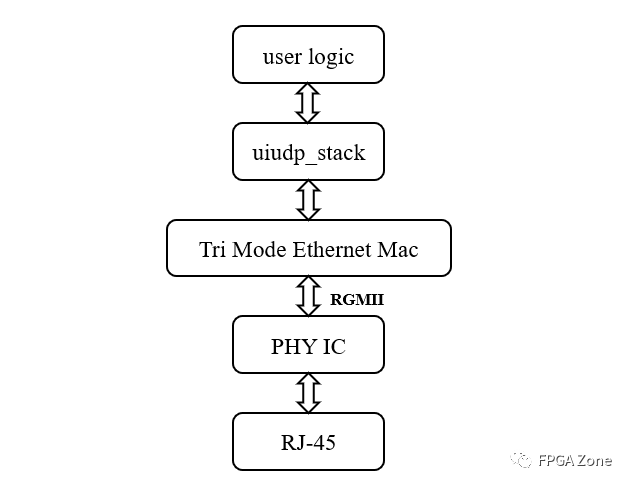

该以太网通信方案参考米联客例程设计,硬件接口采用RGMII,IP核调用Vivado 的 Tri Mode Ethernet MAC。通信方案如下图所示,最上层为用户逻辑模块,用于处理和使用解析后的以太网通信数据;uiudp_stack 模块采用米联客例程提供的协议栈网表文件;FPGA 以太网IP核采用Tri Mode Ethernet Mac;PHY芯片采用 88E1512;最后 RJ-45 接口通过网线与上位机连接。

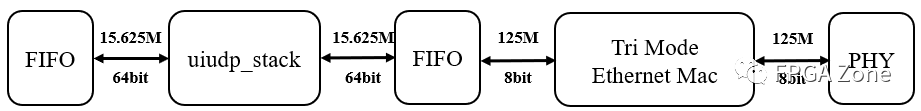

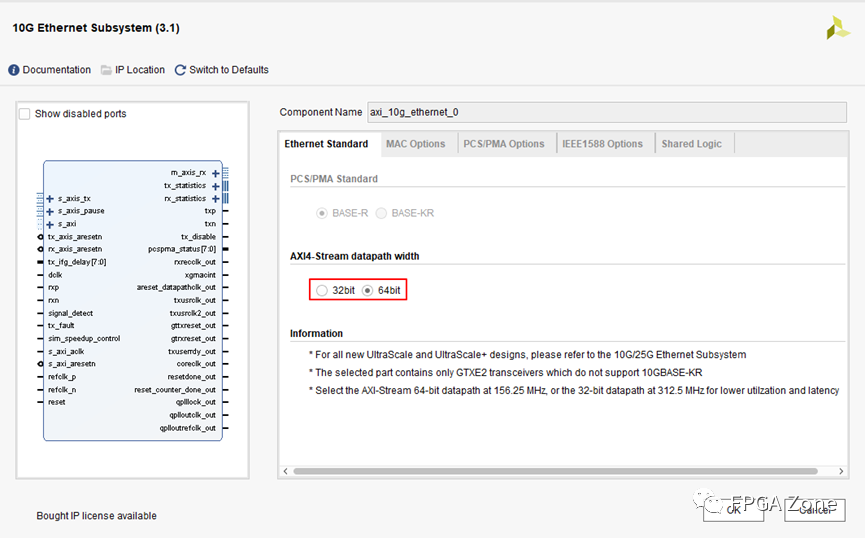

下图为以太网数据环路传输测试方案,在电脑上通过网络调试助手向FPGA发送任意小于1472字节长度的UDP数据包。由于Tri Mode Ethernet Mac IP核接口数据流为8bits/125M,而uiudp_stack为64bits/15.625M,因此需要在中间插入FIFO缓存模块,进行数据位宽转换以及数据跨时钟域处理。

04工程源码结构

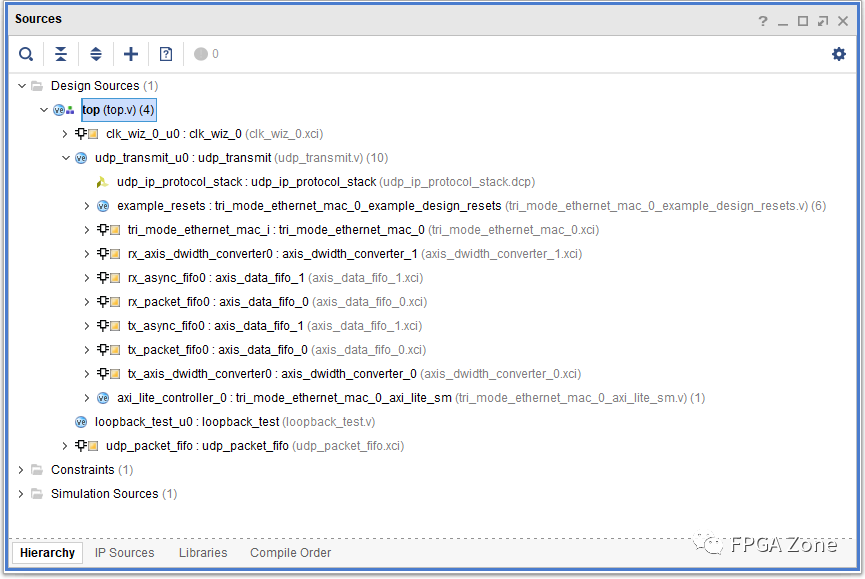

下图是该项目 Vivado 工程源码结构:

其中,

- udp_transmit:UDP以太网数据收发模块;

- loopback_test:UDP以太网数据回环传输测试模块;

- tri_mode_ethernet_mac_0_axi_lite_sm:用于配置、读取以太网IP核寄存器等。

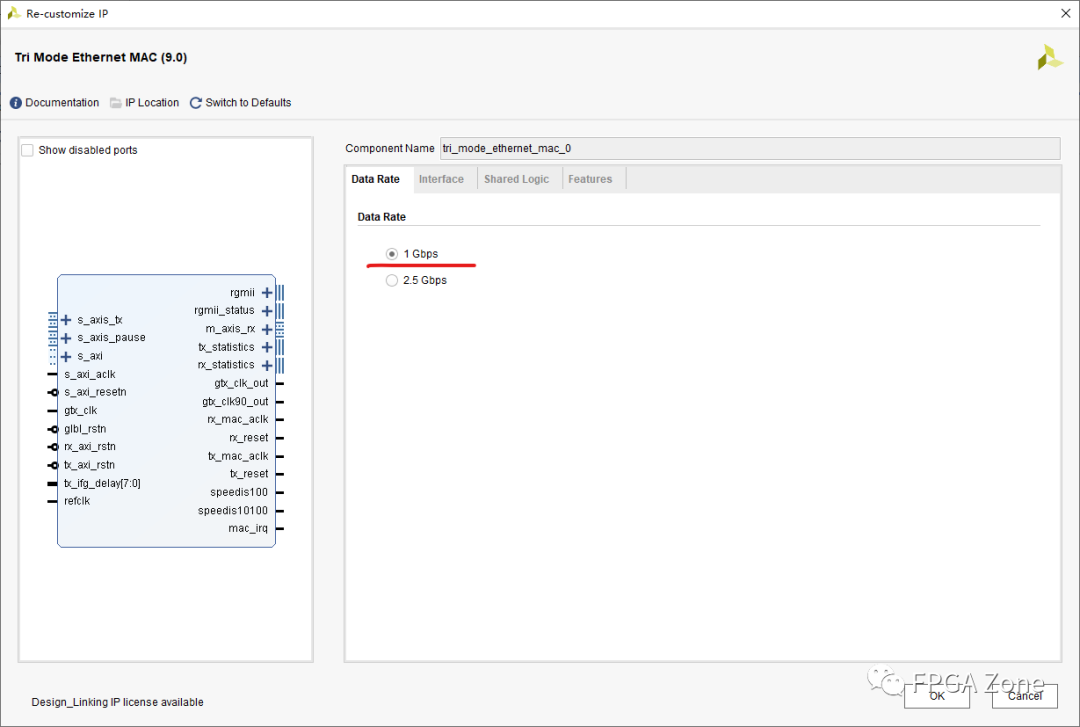

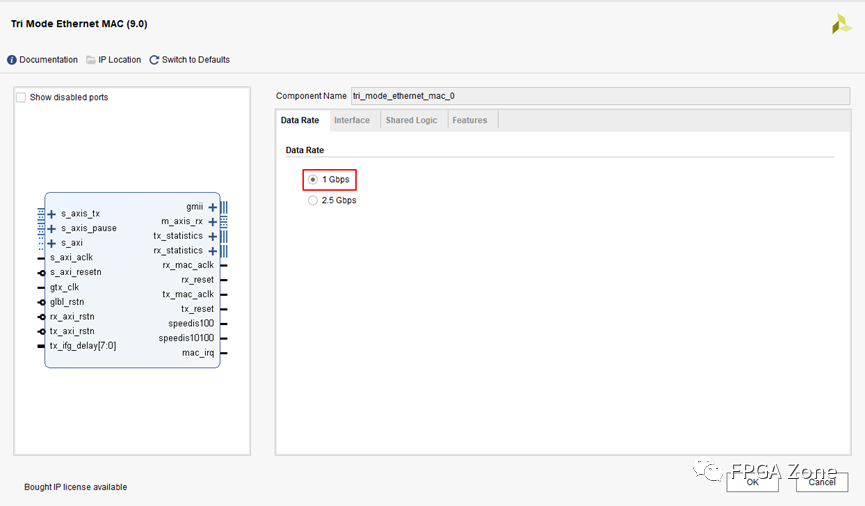

05IP核参数配置

使用千兆通讯,因此将速率设为 1Gbps;

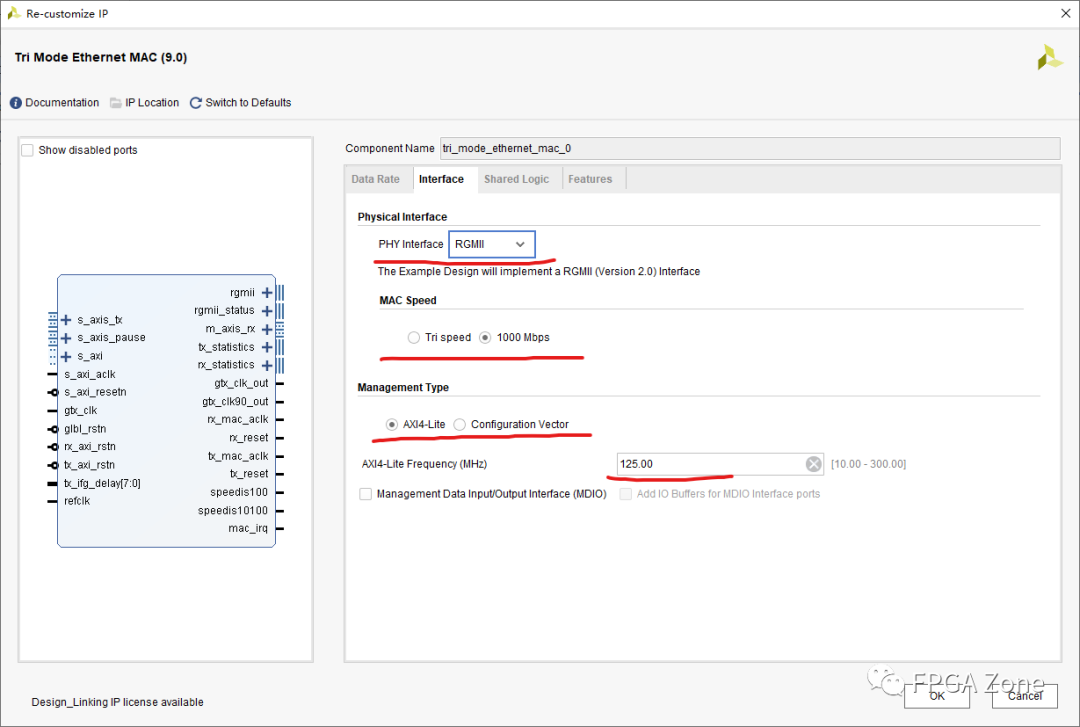

接口参数配置如下:

另外,有关 UDP 协议栈 uiudp_stack 的详细信息这里不再介绍,其pdf文档和源码一起提供,有需要的小伙伴可以自己去查阅。

06其它注意事项

- PHY芯片 复位信号 :上电后将复位信号拉高;

- FPGA RGMII输出 I/O 口 电平标准 :配置成 SSTL 电平标准。

-

FPGA

+关注

关注

1664文章

22504浏览量

639341 -

千兆以太网

+关注

关注

0文章

80浏览量

14305 -

UDP

+关注

关注

0文章

335浏览量

35529 -

Vivado

+关注

关注

19文章

860浏览量

71408 -

RGMII

+关注

关注

0文章

31浏览量

12761

发布评论请先 登录

以太网通讯在FPGA上的实现

DE2-115开发板以太网通信问题

以太网通讯控制仪器,使用UDP协议,仪器无响应

简谈基于FPGA的千兆以太网设计

基于FPGA的UDP RGMII千兆以太网设计

基于FPGA的UDP RGMII千兆以太网通信方案

基于FPGA的UDP RGMII千兆以太网通信方案

评论